1 系統(tǒng)工作原理

數(shù)字化儀模塊主要由前端信號調(diào)理通路、模數(shù)轉(zhuǎn)換電路,、數(shù)據(jù)存儲單元,、數(shù)據(jù)采集控制電路、PXI接口電路等部分組成,,其原理框圖如圖l所示,。

高速

2 系統(tǒng)設(shè)計實現(xiàn)

2.1 模塊化的FPGA設(shè)計

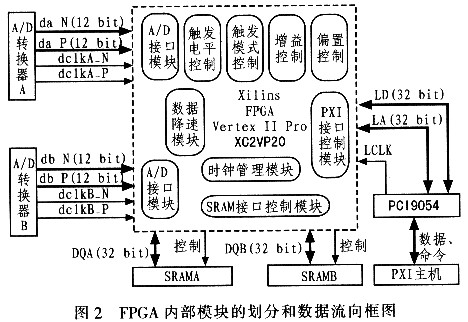

本文所設(shè)計的數(shù)字化儀是基于高性能FPGA芯片實現(xiàn)的,,F(xiàn)PGA承擔(dān)了絕大部分的控制和數(shù)據(jù)處理任務(wù),是本設(shè)計的核心器件,。對FPGA進(jìn)行模塊 化設(shè)計,,是大型系統(tǒng)設(shè)計的常用方法。合理分割功能模塊,,能加快FPGA的開發(fā),,也有利于代碼的移植和重復(fù)利用。在設(shè)計時將FPGA分成高速A/D接口模 塊,、數(shù)據(jù)降速模塊,、調(diào)理通路控制模塊、存儲接口模塊,、PXI接口控制模塊等主要功能模塊設(shè)計,。FPGA內(nèi)部模塊劃分和數(shù)據(jù)流向如圖2所示。

A/D接口模塊主要實現(xiàn)FPGA和高速A/D轉(zhuǎn)換器的互聯(lián),,以LVDS格式總線接收數(shù)據(jù)和采樣時鐘,,該部分電路決定數(shù)據(jù)采集的穩(wěn)定性,需要從硬 件和軟件兩個方面保證,;數(shù)據(jù)降速模塊采用抽取濾波器將信號降低到需要的采樣速率,;調(diào)理通路控制模塊主要實現(xiàn)對A/D前端電路的控制,包括耦合方式,、匹配阻 抗選擇,、增益自動控制、偏置和觸發(fā)電平控制等,;PXI接口部分主要實現(xiàn)和PXI主機(jī)的通訊譯碼,;存儲控制模塊完成對外部SRAM的控制,實現(xiàn)數(shù)據(jù)緩存,;時 鐘管理模塊負(fù)責(zé)采樣時鐘的分頻,、倍頻等處理。

2.2 高速數(shù)據(jù)采集和存儲接口設(shè)計

高速數(shù)據(jù)采集系統(tǒng)的輸入輸出接口設(shè)計是尤為重要的,,高速IC芯片的相互連接是決定數(shù)據(jù)采集系統(tǒng)穩(wěn)定性的關(guān)鍵因素之一,,低功耗及高的信噪比是有待 解決的主要問題。通常實現(xiàn)高速采集系統(tǒng)中芯片間互聯(lián)有兩種接口:PECL和LVDS,。正電壓射極耦合邏輯PECL(Positive Emit-ter-Coupled Logic)信號的擺幅小,,適合于高速數(shù)據(jù)的串行或并行連接,PECL間的連接一般采用直流耦合,,輸出設(shè)計為驅(qū)動50 Ω負(fù)載至(VCC -2V),,連接電路如圖3所示,。

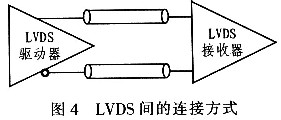

低壓差分信號LVDS(Low Voltage Differential Signal)標(biāo)準(zhǔn)是一種小振幅差分信號技術(shù),它使用非常低的幅度信號(100~450 mV),。通過一對平行的PCB走線或平衡電纜傳輸數(shù)據(jù)。在兩條平行的差分信號線上流經(jīng)的電流方向相反,,噪聲信號同時耦合到兩條線上,,而接收端只關(guān)心兩信號 的差值,于是噪聲被抵消,。由于兩條信號線周圍的電磁場也互相抵消,,故差分信號傳輸比單線信號傳輸電磁輻射小很多,從而提高了傳輸效率并降低了功耗,。 LVDS的輸入與輸出都是內(nèi)部匹配的,,采用直連方式即可,連接方式如圖4所示,。

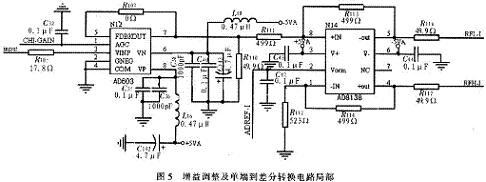

本設(shè)計中,。A/D轉(zhuǎn)換器選用Mamix公司的MAXl215,該芯片是一款12 bit/250 Ms/s的高速A/D轉(zhuǎn)換器,,它具有出色的SNR和SFDR特性,,使用250 MHz差分采樣時鐘,接收差分輸入信號,,輸出12位LVDS格式的差分?jǐn)?shù)字信號,,提供差分同步時鐘信號。為了提高測試精度,,單端的輸入信號需要轉(zhuǎn)換成差分 模式后再送入A/D,,增益調(diào)整及單端到差分轉(zhuǎn)換電路的局部如圖5所示??紤]阻抗匹配問題,,在單端信號轉(zhuǎn)換為差分模式時,需要在2個差分線上串聯(lián)50 Ω的匹配電阻,,作為LVDS信號的發(fā)送端,。

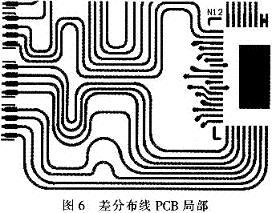

在PCB的設(shè)計中,對差分線要進(jìn)行特別處理,。差分線在走線區(qū)間內(nèi)的實際布線公差應(yīng)控制在5 mil內(nèi),;差分對內(nèi)兩條線之間的距離應(yīng)盡可能小,以使外部干擾為共模特征,;要保證每個差分對內(nèi)的長度相互匹配,,以減少信號扭曲;采用電源層作為差分線的信 號回路,,因為電源平面有最小的傳輸阻抗,,可以有效減少噪聲影響,。圖6所示為本設(shè)計PCB的局部。

本設(shè)計中FPGA作為LVDS信號的接收端,,首先需要將A/D輸入的LVDS差分?jǐn)?shù)據(jù)和同步時鐘信號轉(zhuǎn)換成單信號,。此處選用了xilinx公司 的VirtexⅡ-Pro系列FPGA,該系列的FPGA嵌入了高速I/O接口,,能實現(xiàn)超高帶寬的系統(tǒng)芯片設(shè)計,,支持LVDS、LVPECL等多種差分接 口,,適應(yīng)性很強(qiáng),,為高速數(shù)據(jù)接口提供了完善的解決方案。LVDS差分信號的接收可以通過例化IBUFDS_LVDS這個模塊來實現(xiàn),,同時在程序中設(shè)置使用 內(nèi)部的匹配電阻,,實現(xiàn)LVDS的阻抗匹配。差分時鐘信號由全局時鐘輸入腳接入FPGA,,然后通過調(diào)用xFPGA特有的數(shù)字時鐘管理模塊(DCM),,將時鐘 轉(zhuǎn)換成單信號并進(jìn)行分頻、移相等處理,,作為后續(xù)處理的時鐘信號,。

2.3 PXI接口設(shè)計

PXI是PCI在儀器領(lǐng)域的擴(kuò)展(PCI eXtensions for Instrumentation),它將CompactPCI規(guī)范定義的PCI總線技術(shù)發(fā)展成適用于試驗,、測量與數(shù)據(jù)采集場合應(yīng)用的機(jī)械,、電氣和軟件規(guī) 范,從而形成了新的虛擬儀器體系結(jié)構(gòu),。PXI模塊化儀器系統(tǒng)具備高速的性能,,并與PCI保持兼容性,形成一種主流的虛擬儀器測試平臺,。本設(shè)計中使用 PCI9054進(jìn)行PXI接口硬件的設(shè)計,,PCI9054是美國PLX公司生產(chǎn)的一款32位/33 MHz通用PCI總線控制器專用器件,它具有強(qiáng)大的功能和簡單的用戶接口,,為PCI總線接口的開發(fā)提供了一種簡便方法,。

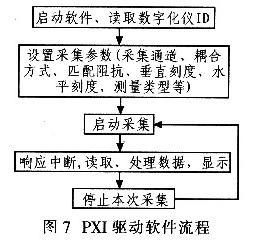

2.4 PXI驅(qū)動開發(fā)

PXI的軟件要求包括支持Microsoft Windows NT和95(WIN32)這樣的標(biāo)準(zhǔn)操作系統(tǒng)框架,要求所有儀器模塊帶有配置信息(configuration information)和支持標(biāo)準(zhǔn)的工業(yè)開發(fā)環(huán)境(如NI的LabVIEW,、LabWindows/CVI和Microsoft的VC/C++,、VB和 Borland的C++等),而且符合VISA規(guī)范的設(shè)備驅(qū)動程序(WIN32 device drivers),。本設(shè)計應(yīng)用K

3 結(jié)束語

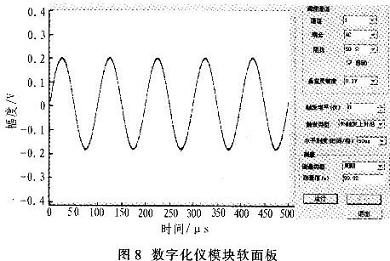

本文給出了基于PXI總線接口的高速數(shù)字化儀模塊的設(shè)計實現(xiàn)方法,,介紹了高速數(shù)據(jù)采集系統(tǒng)中LVDS接口,、LVPECL接口電路結(jié)構(gòu)及連接方 式,并在所設(shè)計的數(shù)字化儀模塊中得到應(yīng)用,。系統(tǒng)可以穩(wěn)定的工作在250 MHz,,實現(xiàn)高精度、長時間的數(shù)據(jù)采集和分析,。該數(shù)字化儀模塊已成功應(yīng)用于多個PXI測試系統(tǒng)中,廣泛應(yīng)用于工業(yè)自動化,、通信,、科研、軍事,、航空航天,、消 費(fèi)電子等多個領(lǐng)域。