1 引 言

頻率測(cè)量不僅在工程應(yīng)用中有非常重要的意義,而且在高精度定時(shí)系統(tǒng)中也處于核心地位,±1個(gè)計(jì)數(shù)誤差通常是限制頻率測(cè)量精度進(jìn) 一步提高的重要原因。由于測(cè)頻技術(shù)的重要性,使測(cè)頻方法也有了很大的發(fā)展,常用數(shù)字頻率測(cè)量方法有M法,T法,和M/T(等精度測(cè)量法)法。M法,T法, 和M/T法都存在±1個(gè)計(jì)數(shù)誤差問題:M法存在被測(cè)閘門內(nèi)±1個(gè)被測(cè)信號(hào)的脈沖個(gè)數(shù)誤差,T法或M/T法也存在±1個(gè)字的計(jì)時(shí)誤差,這個(gè)問題成為限制測(cè)量 精度提高的一個(gè)重要的原因。全同步頻率測(cè)量法[1],從根本上消除了限制測(cè)量精度提高的±1個(gè)計(jì)數(shù)誤差問題,從而使頻率測(cè)量的精度和性能大為改善。

基于對(duì)FPGA器件和EDA技術(shù)以及全同步測(cè)頻方法的研究[2,3],介紹一種利用FPGA實(shí)現(xiàn)DC~100 MHz全同步數(shù)字頻率計(jì)的實(shí)現(xiàn)方法,并給出VHDL實(shí)現(xiàn)代碼和仿真波形。整個(gè)系統(tǒng)在研制的FPGA/CPID實(shí)驗(yàn)開發(fā)系統(tǒng)上調(diào)試通過。本設(shè)計(jì)采用了高集成度的現(xiàn)場(chǎng)可編程門陣列(Field Program-mable Gata Array,F(xiàn)PGA)Flex EPF10k20TCl44-4芯片[4],通過軟件編程對(duì)目標(biāo)器件的結(jié)構(gòu)和工作方式進(jìn)行重構(gòu),能隨時(shí)對(duì)設(shè)計(jì)進(jìn)行調(diào)整,使得本設(shè)計(jì)具有集成度高、結(jié)構(gòu)靈活、開發(fā)周期短、可靠性高的優(yōu)點(diǎn)。

在文獻(xiàn)[2,5]中所描述的等精度頻率測(cè)量方法中,其測(cè)頻原理如圖1所示。

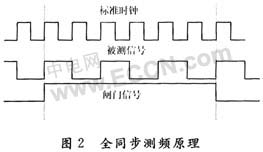

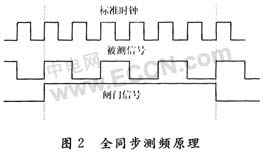

其 誤差與閘門時(shí)間和標(biāo)準(zhǔn)時(shí)鐘頻率有關(guān),閘門時(shí)間越長(zhǎng),標(biāo)準(zhǔn)時(shí)鐘頻率越高,誤差越小。因此,用等精度測(cè)頻法時(shí)所取的標(biāo)準(zhǔn)時(shí)鐘頻率比較高(10 MHz以上),因此±1計(jì)數(shù)誤差相對(duì)很小。標(biāo)準(zhǔn)時(shí)鐘頻率不可能無(wú)限制提高,并且隨著頻率提高,產(chǎn)品成本成倍增加,對(duì)于生產(chǎn)應(yīng)用沒有意義。因此本設(shè)計(jì)用改進(jìn) 的等精度頻率測(cè)量方法--全同步測(cè)量來實(shí)現(xiàn)數(shù)字頻率計(jì)的設(shè)計(jì)。在全同步的情況下,閘門信號(hào)不僅與被測(cè)信號(hào)同步,還與標(biāo)準(zhǔn)時(shí)鐘同步。其原理圖如圖2所示。

2 全同步測(cè)頻原理簡(jiǎn)述

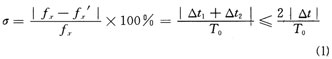

由文獻(xiàn)[1,6]可知:設(shè)開啟閘門時(shí)脈沖同步時(shí)間差為△t1,關(guān)閉閘門時(shí)脈沖同步時(shí)間差為△t2,脈沖同步檢測(cè)最大誤差為△t,則有:△t1≤△t,△t2≤△t。頻率測(cè)量的相

對(duì)誤差如式(2)所示:

由式(1)可知,誤差只與脈沖檢測(cè)電路準(zhǔn)確度有關(guān),顯然,控制△t來提高頻率測(cè)量精度是有效的,而且實(shí)現(xiàn)走來比提高標(biāo)準(zhǔn)時(shí)鐘頻率更容易。

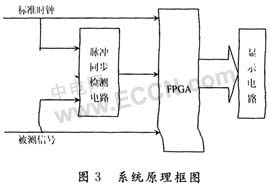

在以上分析的基礎(chǔ)上,本設(shè)計(jì)采用FPGA來實(shí)現(xiàn)全同步數(shù)字頻率計(jì)。其系統(tǒng)原理框圖如圖3所示。由圖3可知,設(shè)計(jì)的絕大部分由FPGA完成,只有脈沖同步檢測(cè)電路由74LS系列與非門來實(shí)現(xiàn),以及顯示部分由數(shù)碼管構(gòu)成。

3 全同步數(shù)字頻率計(jì)模塊設(shè)計(jì)

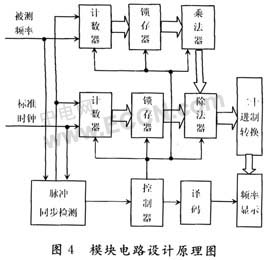

由系統(tǒng)原理框圖3,則其FPGA內(nèi)部模塊電路設(shè)計(jì)原理如圖4所示。

設(shè) 計(jì)原理圖主要由以下幾部分組成:脈沖同步檢測(cè)電路、2個(gè)計(jì)數(shù)器、2個(gè)鎖存器、控制器、乘法器、除法器、澤碼電路等組成。工作原理如下:被測(cè)頻率與標(biāo)準(zhǔn)時(shí)鐘 分別送給脈沖同步檢測(cè)電路與2個(gè)計(jì)數(shù)器,當(dāng)脈沖同步檢測(cè)電路檢測(cè)到被測(cè)頻率與標(biāo)準(zhǔn)時(shí)鐘相位同步時(shí),脈沖同步檢測(cè)電路發(fā)出同步信號(hào),2個(gè)計(jì)數(shù)器開始計(jì)數(shù),當(dāng) 脈沖同步檢測(cè)電路再次檢測(cè)到間步信號(hào)時(shí),義發(fā)出同步信號(hào),計(jì)數(shù)器停止計(jì)數(shù)。同時(shí)計(jì)數(shù)器的計(jì)數(shù)值鎖存到鎖存器,時(shí)序乘法器從鎖存器中取得被測(cè)頻率的計(jì)數(shù)值與 標(biāo)準(zhǔn)時(shí)鐘頻率進(jìn)行乘法運(yùn)算,然后再將乘法器運(yùn)算所得的值與標(biāo)準(zhǔn)時(shí)鐘的計(jì)數(shù)值送給除法器,乘法器的結(jié)果為被除數(shù),標(biāo)準(zhǔn)時(shí)鐘的計(jì)數(shù)值為除數(shù),運(yùn)算所得結(jié)果就是 被測(cè)信號(hào)的頻率,然后冉經(jīng)過二卜進(jìn)制轉(zhuǎn)換變成BCD碼,送給數(shù)碼管顯示。本設(shè)計(jì)采用10 MHz的標(biāo)準(zhǔn)時(shí)鐘,由于乘法器輸入是27位二進(jìn)制,相當(dāng)于9位10進(jìn)制數(shù),而10 MHz的標(biāo)準(zhǔn)時(shí)鐘為107Hz,因此用被測(cè)頻率的計(jì)數(shù)值乘以108可得到一位小數(shù)點(diǎn)。

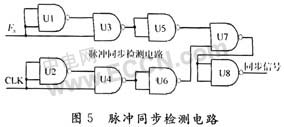

3.1 脈沖同步檢測(cè)電路

脈沖同步檢測(cè)電路 沒計(jì)原理圖如圖5所示。U1~U8為74LS系列與非門,同步檢測(cè)電路利用門電路的延時(shí)來構(gòu)成。當(dāng)被測(cè)信號(hào)及標(biāo)準(zhǔn)時(shí)鐘都處在低電平時(shí),U1,U2輸出為高 電平,U3,U4的輸出為高電平,U5,U6輸出為低電平,則U8輸出為低電平。當(dāng)被測(cè)信號(hào)(Fx)及標(biāo)準(zhǔn)時(shí)鐘的上升沿同時(shí)到來時(shí),由于門電路具有延時(shí)特 性,因此U1,U2并不馬上變?yōu)榈碗娖剑且?jīng)過一個(gè)延時(shí)才變?yōu)榈碗娖健S谑荱3,U4的輸入端都是高電平,則U3,U4

輸出為低電平,U5,U6的輸出為高電平,則U8輸出為高電平。但是當(dāng)且儀當(dāng)Fx與CLK的上升沿在在延時(shí)時(shí)間內(nèi)同時(shí)到達(dá)時(shí)U8才會(huì)輸出高電平。74LS系列與非門的延時(shí)最小為4 ns,最大為15 ns,因此最大誤差為11ns。根據(jù)公式(2)得:

![]()

當(dāng)T0為1 s時(shí),其精度可達(dá)到10-7,如再減小相位誤差,則可提高頻率計(jì)的精確度。

3.2 FPGA芯片內(nèi)部模塊電路設(shè)計(jì)和仿真結(jié)果

FPGA芯片內(nèi)部模塊電路設(shè)計(jì)和仿真結(jié)果如圖6到圖9所示。

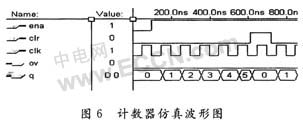

3.2.1 計(jì)數(shù)器

此 計(jì)數(shù)播為27位二進(jìn)制,具有計(jì)數(shù)使能端(ena)、異步清零端(clr)、時(shí)鐘輸入端(clk)、進(jìn)位輸出端(ov)等。當(dāng)異步清零端(clr)為高電平 時(shí),不管計(jì)數(shù)使能端是否有效,時(shí)鐘上升沿是否到來,計(jì)數(shù)器都立即清零,即q=0。只有異步清零端(clr)為低電平,并且汁數(shù)使能端為高電平,有上升沿到 來時(shí),計(jì)數(shù)器才開始計(jì)數(shù),當(dāng)計(jì)數(shù)器計(jì)滿時(shí),進(jìn)位輸出為高電平。計(jì)數(shù)器VHDL程序仿真圖如圖6所示。

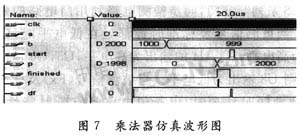

3.2.2 乘法器

由 于本設(shè)計(jì)所用的乘法器位數(shù)較寬,而組合邏輯乘法器位數(shù)越多耗用的硬件資源成倍增長(zhǎng),并且本設(shè)計(jì)不需要有很高的運(yùn)算速度,考慮到硬件資源與運(yùn)算速度,因此采 用時(shí)序電路來實(shí)現(xiàn)乘法器,其原理是通過逐項(xiàng)移位相乘相加來實(shí)現(xiàn)。他是一種犧牲運(yùn)算時(shí)間換取硬件資源的方案。乘法器的VHDL程序仿真圖如圖7所示。

3.2.3 除法器

除法器則可通過移位相減相除來實(shí)現(xiàn),其工作原理與剩法器是一樣的,其VHDL程序仿真圖如圖8所示。

3.2.4 控制器

控 制器工作時(shí)序如下:當(dāng)同步信號(hào)(clk)上升沿到來時(shí),計(jì)數(shù)使能信號(hào)(cp)立即變成高電平,鎖存信號(hào)(creg)及清零信號(hào)(clr)變成低電平,同步 信號(hào)(clk)的上升沿再次到來時(shí),除清零信號(hào)(clr)外,其余信號(hào)均取反,當(dāng)同步信號(hào)(clk)的下降沿到來時(shí),清零信號(hào)(clr)變成高電平。當(dāng)同 步信號(hào)又到來時(shí),重復(fù)上述過程,其仿真結(jié)果如圖9所示。

3.2.5 頂層設(shè)計(jì)

由 模塊電路設(shè)計(jì)原理圖4,經(jīng)過VHDL編程,得到各模塊的VHDL設(shè)計(jì)實(shí)體,然后對(duì)各模塊的設(shè)計(jì)實(shí)體在Max+PlusⅡ中進(jìn)行仿真,驗(yàn)證各模塊的正確性。 最后再設(shè)計(jì)一個(gè)頂層文件把各模塊按圖4連接起來,便構(gòu)成了一個(gè)全同步數(shù)字頻率計(jì)的FPGA內(nèi)部硬件電路。下面給出頂層文件的仿真結(jié)果,由仿真圖10可看 出:124×108/93=13 333 333,由于使用的是10 MHz的晶振,因此還有一位小數(shù)點(diǎn)最終顯示的結(jié)果應(yīng)該是1 333 333.3Hz。由仿真圖11知,小數(shù)位在數(shù)碼管的第二位上有效,其余位均無(wú)效。仿真結(jié)果與期望結(jié)果一致。至此,本設(shè)計(jì)得到成功驗(yàn)證。

4 結(jié) 語(yǔ)

本 文利用Altear公司的FPGA芯片F(xiàn)lexEPF10k20TC144-4 [5],使用VHDL語(yǔ)言設(shè)計(jì)了全同步數(shù)字頻率計(jì),在Max+PlusⅡ中進(jìn)行了各模塊的仿真,達(dá)到了預(yù)期結(jié)果。全同步數(shù)字頻率計(jì)是目前精度最高的頻率計(jì) 之一。在高速時(shí)鐘隨處可見的現(xiàn)代電子系統(tǒng),有著非常廣泛的研究?jī)r(jià)值。從某種程度上說他是以犧牲時(shí)間來?yè)Q取精確度的,但一般情況下測(cè)頻系統(tǒng)對(duì)時(shí)間的要求并不 高,并且由于電子系統(tǒng)對(duì)系統(tǒng)時(shí)鐘的準(zhǔn)確度越來越高,因此全同步數(shù)字頻率計(jì)有著廣泛的應(yīng)用空間。