隨著現(xiàn)代通信技術(shù)的迅速發(fā)展,信號的調(diào)制方式向多樣化發(fā)展,,解淵技術(shù)也隨之不斷向前發(fā)展,。為了對高速大帶寬的信號進行實時解調(diào),現(xiàn)在很多的解調(diào)關(guān)鍵算法都是在高速硬件上用可編程邏輯器件(FPGA)實觀,,利用FPGA強大的資源和實時處理能力來快速的實現(xiàn)信號的跟蹤,、鎖定和解調(diào)但是,基于硬件的實現(xiàn)方案和基于軟件的方案相比,,往往存在不能迅速適應(yīng)調(diào)制樣式改變的問題,。為了有效斛決這個問題,筆者通過基下FPGA部分動態(tài)町重構(gòu)技術(shù),,提出了相應(yīng)的解決方案,。

1 FPGA部分動態(tài)可重構(gòu)技術(shù)介紹

從90年代以來,隨著FPGA芯片技術(shù)的逐步成熟和發(fā)展,,F(xiàn)PGA在各個領(lǐng)域中的應(yīng)用逐漸擴大,,芯片內(nèi)部的資源規(guī)模也成倍增加。但是,,隨著FPGA容量的擴大,,F(xiàn)PGA的設(shè)計和實現(xiàn)也漸漸出現(xiàn)了下面的瓶頸問題:

1)FPGA芯片內(nèi)部布線隨著設(shè)計復(fù)雜度的增加,布線的難度成平方增加,,布線的時間也成倍增加,。

2)對于大容量的FPGA,為了保證設(shè)計時約定的性能,為了滿足時序約束條件,,最終實現(xiàn)版本的實際資源利用率反而下降,。

3)大容量的FPGA一旦設(shè)計完成后,對其進行部分模塊的調(diào)整和優(yōu)化經(jīng)常需要很長時間,。

在此上述這些原因的基礎(chǔ)上,,F(xiàn)PGA的重配置技術(shù)應(yīng)需而生。FPGA重配置技術(shù)分為完全重配置技術(shù)和部分動態(tài)可重構(gòu)技術(shù)兩種,。其中FPGA完全重配置技術(shù)就是通過FPGA外部的配置處理單元,,通過對FPGA配置管腳的編程,來實現(xiàn)整個FPGA內(nèi)容的切換,,這種方式在目前已經(jīng)得到了較為廣泛的應(yīng)用,。而FPGA部分動態(tài)可重構(gòu)技術(shù)是通過FPGA內(nèi)部或外部的配置處理單元,對FPGA內(nèi)部部分資源的時分復(fù)用,,來實現(xiàn)FPGA內(nèi)部部分模塊的切換,。

對這兩種配置技術(shù)進行比較,可以看到FPGA部分動態(tài)可重構(gòu)技術(shù)的優(yōu)勢在于以下這些方面:

1)提高了配置速度,。完全重配置需要配置整個FPGA的比特流文件,,而部分動態(tài)可重構(gòu)技術(shù)只需要配置相應(yīng)模塊的邏輯內(nèi)容,文什大小相差懸殊,,在相同的配置時鐘頻率下,,部分動態(tài)可重構(gòu)技術(shù)的配置速度是完全配置的幾分之一或者幾十分之一。

2)省略了完全配置后的復(fù)位,、下達參數(shù)的流程,。完全重配置在配置完成后,整個FPGA處于初始狀態(tài),,需要重新對接口進行初始化,,并配置運行參數(shù)。而部分動態(tài)可重構(gòu)技術(shù)不用進行全局復(fù)位,,下達參數(shù)也只需要針對重構(gòu)的模塊,。

3)保存了FPGA運行的中間結(jié)果和數(shù)據(jù)。完全重配置很難保存FPGA運行的中間結(jié)果,,如果外接DDR SDRAM等存儲單元,,也會因為接口的重新復(fù)位而導(dǎo)致數(shù)據(jù)混亂,而部分動態(tài)可重構(gòu)技術(shù)完全不用擔心這些問題,。

部分動態(tài)可重構(gòu)技術(shù)具有上述相對與完全重配置技術(shù)的優(yōu)勢外,,也和完全重配置技術(shù)一樣,具有低功耗和靈動性高的優(yōu)點,,并且具備遠程加載功能,,可以通過有線網(wǎng)絡(luò)或者無線網(wǎng)絡(luò)來實現(xiàn)超距環(huán)境下的FPGA功能變更,。

部分動態(tài)可重構(gòu)技術(shù)和完全重配置技術(shù)相比,對FPGA設(shè)計人員的開發(fā)能力和規(guī)劃能力要求更高,,下面通過對一個簡單的數(shù)字信號解調(diào)系統(tǒng),,來給出部分動態(tài)可重構(gòu)技術(shù)的實現(xiàn)途徑。

2 FPGA部分動態(tài)可重構(gòu)技術(shù)的硬件實現(xiàn)方案

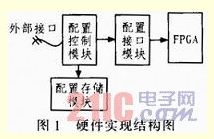

FPGA部分動態(tài)可重構(gòu)的硬件實現(xiàn)如圖1所示,,為了保證FPGA配置的可靠性,,本文采用了FPGA外部單元控制配置流程的實現(xiàn)方式。一個基本的實現(xiàn)結(jié)構(gòu)除了被配置的FPGA外,,需要有配置控制模塊,、配置接口模塊和配置存儲模塊這3個部分。其巾配置控制模塊一般由DSP,、單片機,、ARM處理器或者PowerPC選擇,主要功能是從配置存儲模塊或者外部接口中獲取配置比特流文件,,并在需要部分動態(tài)重構(gòu)的時刻把配置比特流文件傳送到配置接口模塊。配置接口模塊一般由FPGA或者CPLD實現(xiàn),,功能是接收配置控制模塊傳輸?shù)呐渲帽忍亓?,進行相應(yīng)的時序轉(zhuǎn)換,產(chǎn)生滿足FPGA配置時序的信號,,從而對FPGA進行配置,。配置存儲模塊一般是FLASH或者SDRAM,可以長期或者臨時保存多個配置比特流文件,。

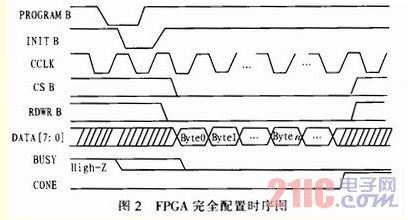

在圖1的結(jié)構(gòu)中,,配置接口模塊是實現(xiàn)的關(guān)鍵模塊,根據(jù)配置速度和穩(wěn)定性的要求,,可以采用Slave SelectMap或者Slave Setial配置模式,,從性能考慮,一般選擇Slave SelectMap這種并行配置模式,,在配置時鐘最高50MHz,、配置管腳32位的情況下,配置速度可以達到1.6Gb ps,。在Slave SelectMap模式下,,配置接口模塊和FPGA的管腳連接可以參考XilinxVinex-5 Configuration User Guide中相應(yīng)章節(jié),本文不再贅述,。并根據(jù)如圖2所示的配置時序,,來實現(xiàn)FPGA完全配置比特流文件的下載和功能實現(xiàn)。

在進行配置部分動態(tài)可重構(gòu)比特流文件時,,因為該比特流文件不像完整的配置比特流文件一樣具有文件頭,,而是只有幀地址、配置數(shù)據(jù)及校驗和,當所有配置內(nèi)容傳輸?shù)紽PGA后,,不會有DONE信號拉高來表示配置結(jié)束,。在這種情況下,必須監(jiān)視傳輸來的配置數(shù)據(jù),,當出現(xiàn)部分重配置文件的結(jié)束標志DESYNCH(0000000D)時,,就可以判斷部分重構(gòu)流程結(jié)束,可以運行新的重構(gòu)模塊,。

3 基于FPGA部分動態(tài)可重構(gòu)的信號解調(diào)系統(tǒng)開發(fā)流程

3.1 FPGA模塊劃分

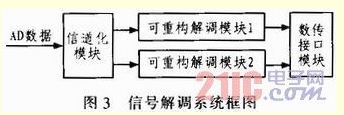

在完成了支持FPGA部分動態(tài)可重構(gòu)的硬件實現(xiàn)后,,下面開始規(guī)劃信號解調(diào)系統(tǒng)的FPGA設(shè)計架構(gòu)。如圖3所示,,信號解調(diào)系統(tǒng)主要由信道化模塊,,可重構(gòu)解調(diào)模塊和數(shù)傳接口模塊組成。

信道化模塊主要是把AD數(shù)據(jù)進行信道化處理,,進行濾波,,下變頻、信道選擇和抽取,??芍貥?gòu)解調(diào)模塊是針對不同調(diào)制樣式的分別實現(xiàn)不同的解調(diào)模塊,并根據(jù)實際需要進行部分重構(gòu),。數(shù)傳接口模塊是把解調(diào)的結(jié)果傳輸?shù)紽PGA外,,進行后續(xù)處理和在界面中顯示。

3.2 FPGA模塊的設(shè)計和實現(xiàn)

按照圖3所示的結(jié)構(gòu),,按照下面步驟進行基于部分動態(tài)可重構(gòu)技術(shù)的FPGA程序設(shè)計:

1)把需要部分重構(gòu)的FPGA模塊設(shè)計為一個空盒,,即只有輸入輸出管腳,沒有實際內(nèi)容的空模塊,。在進行空模塊的管腳規(guī)劃時要綜合考慮多種解調(diào)樣式下的接口兼容性,,保證一個模塊接口能涵蓋需要處理的所有樣式。

2)分別完成不需要部分重構(gòu)的FPGA予模塊,,并完成FPGA頂層模塊,。

3)對FPGA頂層模塊進行綜合,產(chǎn)生頂層網(wǎng)表,。

4)按照步驟1)中的模塊定義格式完成針對不同調(diào)制模式的解淵模塊,,如qpsk_demod,fsk_demod等,,并通過仿真驗證,,然后逐模塊分別綜合成單獨的模塊網(wǎng)表文件,保存到不同的目錄中,。

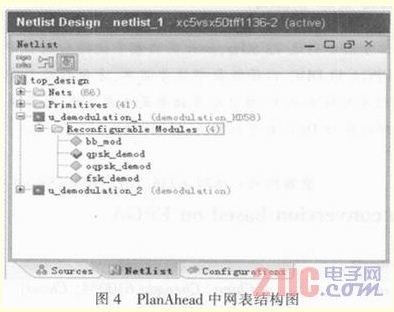

5)在PlanAhead工具中導(dǎo)入FPGA頂層網(wǎng)表,,注意在導(dǎo)入選項中選擇支持部分重構(gòu),。在PlanAhead工具中把2個空的可重構(gòu)解調(diào)模塊設(shè)定為可重構(gòu)分區(qū)(ReconfigurablePartition),如圖4所示,,并把步驟4)中綜合好的模塊網(wǎng)表指定為可重構(gòu)模塊下的可選內(nèi)容,。

6)在PlanAhead工具的Device視圖中,對可重構(gòu)模塊劃分分區(qū)(PBlock),,目前分區(qū)只支持矩形,,要求分區(qū)包含的資源數(shù)目略大于解淵模塊所需資源的最大值,其中包括邏輯資源(查找表和寄存器),,乘法器(DSP48E)和RAM資源,。

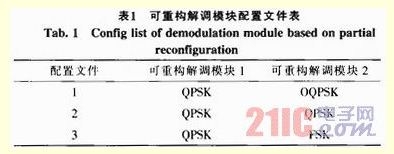

7)根據(jù)對2個可重構(gòu)解調(diào)模塊的不同配置,產(chǎn)生多個配置文件,,配置文件的一個例子如表1所示,,并逐一進行布局布線,產(chǎn)生完整的配置比特流文件和用于部分重構(gòu)的比特流文件,。對于每一組配置文件,,會產(chǎn)生一個包含靜態(tài)邏輯的完整配置比特流文件,和2個用于部分重構(gòu)的比特流文件,,分別對應(yīng)2個不同的分區(qū),,配置加載時不能隨便互換。

8)對表1中配置文件進行設(shè)計規(guī)則檢查比較,,保證各組配置文件生成的完整配置的比特流文件是一致的。

9)完成以上設(shè)計后,,首先調(diào)用任意一個完整配置文件進行加載,,保證FPGA成功運行靜態(tài)邏輯,然后根據(jù)需要,,選擇表1中的配置文件表中的任何1組,,進行部分動態(tài)加載。

4 應(yīng)用結(jié)果

以上設(shè)計經(jīng)過實際驗證,,可以實現(xiàn)2路信號在不同調(diào)制樣式的解調(diào),,當信號樣式變化時,動態(tài)加載相應(yīng)的解調(diào)模塊,,可以迅速完成功能切換,,實現(xiàn)對應(yīng)的解調(diào)功能。經(jīng)過實際測試,,部分動態(tài)可重構(gòu)模塊的加載速度存10 ms以內(nèi),,極大的提高了原有系統(tǒng)的性能。

5 結(jié)論

目前國際上對FPGA可重構(gòu)技術(shù)的研究極為廣泛,,本文介紹了一種基于Xilinx FPGA的部分動態(tài)可重構(gòu)技術(shù)的信號解調(diào)系統(tǒng),,可以把不同的解調(diào)模塊定位到芯片內(nèi)部同一邏輯資源部分,,通過重構(gòu)這些資源來實現(xiàn)不同樣式信號的解調(diào),同時保持其他部分電路功能正常運行,,從而提高了系統(tǒng)的適應(yīng)能力,。

本系統(tǒng)可以存通信系統(tǒng)中得到應(yīng)用,對航天,、電力等領(lǐng)域的類似系統(tǒng)也有參考價值,,可以提高相應(yīng)系統(tǒng)的靈活性和擴展性,減低系統(tǒng)功耗,,縮短系統(tǒng)開發(fā)時間,。