1前言

慣性導(dǎo)航系統(tǒng)、各種導(dǎo)引頭及空間飛行器等測(cè)試和記錄應(yīng)用系統(tǒng),都需要自主、實(shí)時(shí)、可靠存儲(chǔ)大量的關(guān)鍵信息,并保證即使整個(gè)系統(tǒng)掉電,所采集到的數(shù)據(jù)仍能長(zhǎng)時(shí)間保持不丟失,實(shí)現(xiàn)歷史數(shù)據(jù)查詢,便于數(shù)據(jù)分析。NAND Flash閃速存儲(chǔ)器(簡(jiǎn)稱閃存)以其掉電非易失、功耗低、壽命長(zhǎng)、容量大、升級(jí)容易等獨(dú)有的特點(diǎn)迅速成為數(shù)據(jù)存儲(chǔ)的最佳選擇。

某型激光陀螺慣導(dǎo)單元需要在湖試和海試試驗(yàn)過程中記錄大量導(dǎo)航參數(shù),為了便于在試驗(yàn)結(jié)束后有效分析數(shù)據(jù)。這里提出一種基于大容量閃存器件K9KAG08UOM與DSP的接口設(shè)計(jì)方案。在激光慣導(dǎo)的計(jì)算機(jī)板上集成了一片NAND Flash閃速存儲(chǔ)器,根據(jù)試驗(yàn)的次數(shù)和每個(gè)航次存儲(chǔ)數(shù)據(jù)量的大小,選用SAMSUNG公司的K9KAG08UOM存儲(chǔ)器;為滿足導(dǎo)航控制的周期和算法的復(fù)雜程度,選用TI公司的浮點(diǎn)DSPTMS320C6713B作為主控處理器。TMS320C6713B的主頻可達(dá)300 MHz,浮點(diǎn)運(yùn)算速度可達(dá)1.8 GFLO/S,是目前運(yùn)算速度最快的浮點(diǎn)器件之一,已成為嵌入式系統(tǒng)設(shè)計(jì)中的主流處理器。其中NAND Flash與DSP的接口設(shè)計(jì)是整個(gè)計(jì)算機(jī)板設(shè)計(jì)的關(guān)鍵部分,這里詳細(xì)介紹大容量NAND Flash與DSP接口設(shè)計(jì)的硬件接口電路和軟件實(shí)現(xiàn)方法。

2 大容量閃存K9KAG08UOM簡(jiǎn)介

K9KAG08UOM是大容量、高可靠性的NAND Flash存儲(chǔ)器。其存儲(chǔ)容量為2 G字節(jié)(2 Gx8 bit);可將數(shù)據(jù)線與地址線復(fù)用為8條I/O線。并分別提供命令控制信號(hào)線;命令、地址和數(shù)據(jù)信息均通過8條I/O線傳輸,不會(huì)因存儲(chǔ)容量的增加而增加引腳數(shù),從而極大方便系統(tǒng)設(shè)計(jì)和產(chǎn)品升級(jí),而無需更改外部硬件連接,因此成為嵌入式系統(tǒng)中實(shí)時(shí)存儲(chǔ)大容量數(shù)據(jù)的最佳選擇。

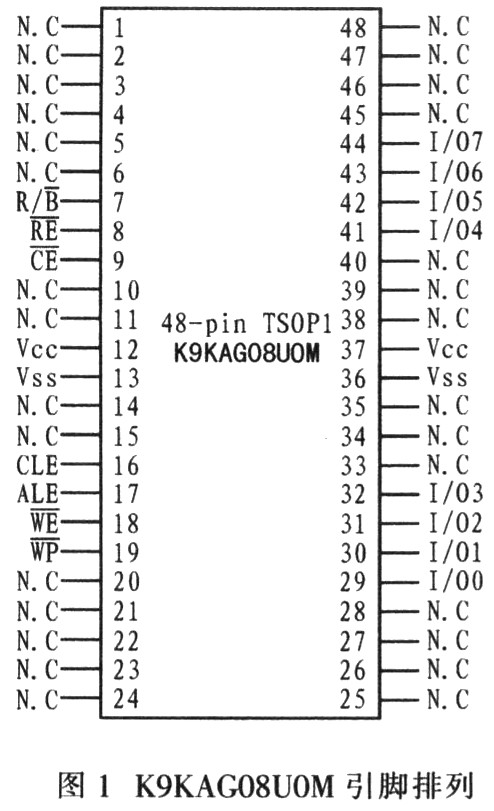

K9KAG08UOM引腳排列如圖1所示,其引腳功能如下:

I/O0~I(xiàn)/O7:8根地址、數(shù)據(jù)和命令復(fù)用信號(hào)。用于輸入命令、數(shù)據(jù)、地址及輸出數(shù)據(jù)。

CE:片選信號(hào)。用于選擇控制器件。

WE:寫使能信號(hào)。通過該端口可在寫脈沖的上升沿鎖存指令、地址和數(shù)據(jù)。

RE:讀使能信號(hào)。在讀信號(hào)的下降沿,輸出數(shù)據(jù)有效,并可累加其內(nèi)部數(shù)據(jù)地址。

CLE:命令鎖存使能信號(hào)。CLE為高電平時(shí),命令通過I/O端口線在寫信號(hào)的上升沿被鎖存入命令寄存器。

ALE:地址鎖存信號(hào)。在寫信號(hào)的上升沿且地址鎖存信號(hào)為高電平時(shí),地址被鎖存。

WP:寫保護(hù)信號(hào)。WP為低電平時(shí),禁止寫或擦除操作。

R/B:準(zhǔn)備就緒或忙輸出顯示信號(hào),當(dāng)R/B為低電平時(shí),表示有編程、擦除或隨機(jī)讀操作正在進(jìn)行,操作完成后.R/B信號(hào)自動(dòng)返回至高電平。

3 硬件接口設(shè)計(jì)

3.1 計(jì)算機(jī)板設(shè)計(jì)方案

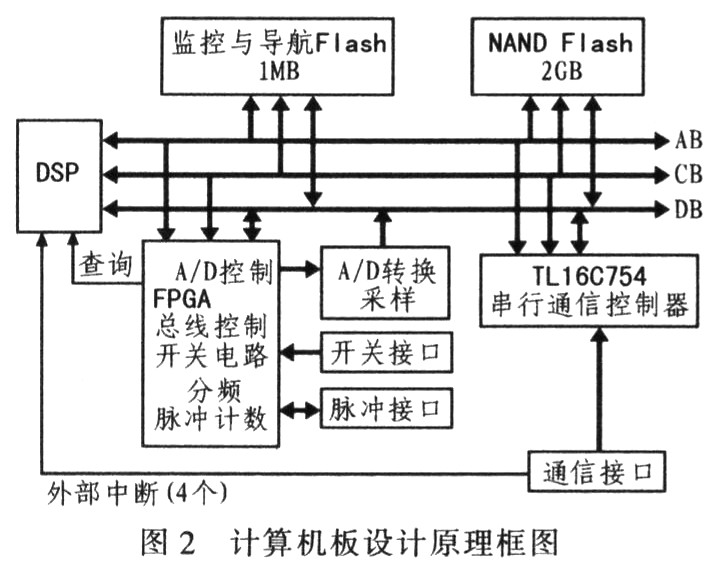

激光陀螺慣導(dǎo)計(jì)算機(jī)板以CPU為核心,完成數(shù)據(jù)的采集、運(yùn)算、通信、數(shù)據(jù)存儲(chǔ)等任務(wù)。計(jì)算機(jī)板的設(shè)計(jì)原理如圖2所示。

計(jì)算機(jī)板主要包括:核心CPU完成導(dǎo)航計(jì)算及對(duì)外圍接口的管理與控制等:監(jiān)控與導(dǎo)航Flash完成程序的自主加載引導(dǎo);NAND Flash完成試驗(yàn)數(shù)據(jù)的記錄與下載;FPGA輔助完成A/D轉(zhuǎn)換時(shí)序控制、總線譯碼控制、開關(guān)電路控制、分頻及脈沖計(jì)數(shù)等功能:4通道串行控制器 TL16C754控制4個(gè)通道串口。

主機(jī)CPU選用DSP器件 TMS320C6713B,其內(nèi)含浮點(diǎn)數(shù)值處理器,支持64位浮點(diǎn)運(yùn)算,內(nèi)部RAM容量為256 K字節(jié),主頻最高可達(dá)300 MHz,帶有的鎖相環(huán)電路使其能夠通過軟件編程設(shè)置實(shí)際工作頻率。

根據(jù)系統(tǒng)時(shí)序控制和計(jì)數(shù)等功能需要邏輯門的大小.FPGA選用ACTEL公司的APA300。該器件內(nèi)部自帶ROM,上電后自主運(yùn)行,無需外部ROM引導(dǎo),可靠性高。

串行通信控制器選用,TI公司的TL16C754B。該器件采用3.3 V供電,功耗低,內(nèi)部有4個(gè)并行的串行通信控制器,內(nèi)部白帶FIFO模式,與DSP無縫接口,使用靈活方便,滿足系統(tǒng)設(shè)計(jì)需要。

3.2 NAND Flash與DSP硬件接口設(shè)計(jì)

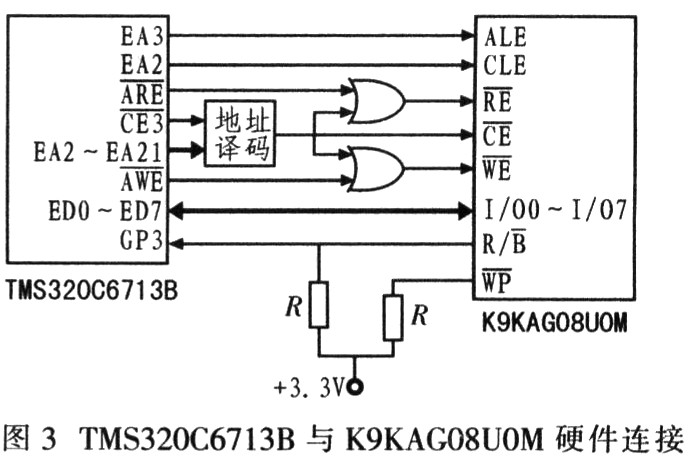

大容量閃存NAND Flash與DSP之間的接口設(shè)計(jì)是CPU板設(shè)計(jì)的關(guān)鍵。DSP主要通過EMIF外部存儲(chǔ)器接口訪問片外存儲(chǔ)器,TMS320C6713B可與大多數(shù)的同步存儲(chǔ)器和異步存儲(chǔ)器靈活配置,使用簡(jiǎn)單方便。TMS320C6713B與K9KAG08UOM的硬件接口電路如圖3所示。

TMS320C6713B的外部存儲(chǔ)器接口包括:20位地址線、32位數(shù)據(jù)線、4個(gè)片選控制線及讀寫控制信號(hào)線。4個(gè)片選信號(hào)分別對(duì)應(yīng)4個(gè)存儲(chǔ)空間,CE3對(duì)應(yīng)的地址空間為OxB0000000-OxBFFFFFFF,設(shè)計(jì)中通過地址譯碼實(shí)現(xiàn)地址空間的分隔,其中大容量閃存器件K9KAG08UOM的片選面對(duì)應(yīng)的地址為OxB0400000。

K9KAG08UOM無地址線,命令、地址和數(shù)據(jù)信息均通過I/00~I(xiàn)/07傳輸。雖然K9KAG08UOM的容量達(dá)到2 G字節(jié),遠(yuǎn)遠(yuǎn)超出TMS320C6713B存儲(chǔ)區(qū)域CE3的可尋址容量256 M字節(jié),但由于訪問NAND Flash的地址是通過I/O端口輸入,無需通過地址線尋址,因此不用考慮邏輯存儲(chǔ)空間與實(shí)際物理空間的映射問題,簡(jiǎn)化了DSP與NAND Flash的硬件接口。

TMS320C6713B和K9KAG08UOM的工作電壓均是3.3 V,因此兩者引腳可直接連接,無需電平轉(zhuǎn)換。設(shè)計(jì)中K9KAG-08UOM的ALE和CLE兩個(gè)信號(hào)分別由DSP的最低兩位地址EA3和EA2控制。DSP的低8位數(shù)據(jù)線直接與NAND Flash的I/00~I(xiàn)/07相連。DSP的通用輸人輸出端口GP3接R/B,用于監(jiān)測(cè)NAND Flash的工作狀態(tài)。當(dāng)R/B處于低電平時(shí),表示有編程、擦除或隨機(jī)讀操作正在進(jìn)行;當(dāng)R/B處于高電平時(shí),表示操作已經(jīng)完成。K9KAG08UOM的讀寫控制信號(hào)RE和WE由DSP的讀寫控制信號(hào)ARE和AWE和譯碼產(chǎn)生的片選信號(hào)CE通過邏輯或得到,只有當(dāng)DSP的讀寫控制信號(hào)和片選同時(shí)有效即為低電平時(shí)才能對(duì)K9KAG08UOM進(jìn)行讀寫操作。

該硬件接口設(shè)計(jì)利用DSP的地址線EA3、EA2分別控制NAND Flash的命令鎖存ALE和地址鎖存CLE信號(hào),此時(shí)對(duì)K9KAG08UOM的訪問相當(dāng)于訪問地址分別為OxB0400002、OxB0400001和OxB0400000的3個(gè)端口.分別對(duì)應(yīng)K9KAG08UOM的地址端口、命令端口和數(shù)據(jù)端口。DSP對(duì)K9KAG08UOM的命令、地址和數(shù)據(jù)操作可通過不同端口進(jìn)行。簡(jiǎn)化了對(duì)K9KAG08UOM讀寫控制和軟件編程設(shè)計(jì)的難度。

4 軟件設(shè)計(jì)

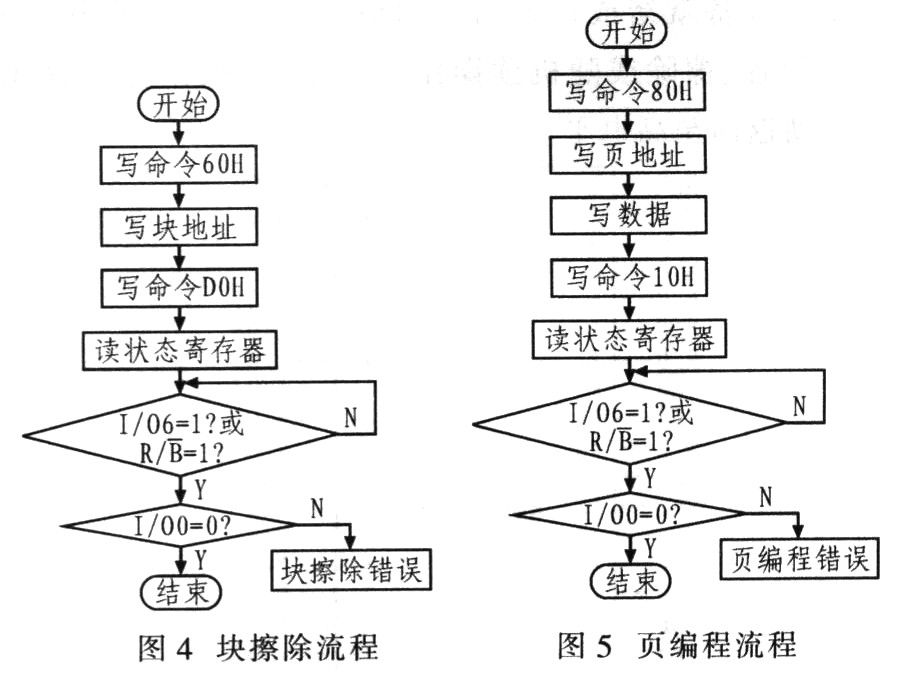

NAND Flash的基本操作主要包括:讀數(shù)據(jù),編程(寫)數(shù)據(jù),擦除、讀器件ID號(hào)等。NAND Flash的軟件設(shè)計(jì)主要關(guān)注以下幾個(gè)方面:

(1)讀、寫操作以頁(yè)為單位;

(2)擦除操作以塊為單位;

(3)對(duì)NAND Flash寫數(shù)據(jù)時(shí),位數(shù)據(jù)只能由1變?yōu)?,因此對(duì)Flash寫操作前必須把寫單元所在塊擦除;

(4)NAND Flash同其他固體存儲(chǔ)器一樣會(huì)產(chǎn)生壞塊,如果將數(shù)據(jù)存儲(chǔ)在壞塊區(qū)域?qū)?dǎo)致無法正常恢復(fù)。壞塊區(qū)域一般不超過器件總?cè)萘康?‰,如果系統(tǒng)的工作狀態(tài)允許存儲(chǔ)的數(shù)據(jù)可以出現(xiàn)少量錯(cuò)誤,比如圖像記錄功能,軟件設(shè)計(jì)時(shí)可不用標(biāo)記為壞區(qū);如果系統(tǒng)的工作狀態(tài)不允許存儲(chǔ)的數(shù)據(jù)出錯(cuò),則需根據(jù)器件出廠時(shí)自帶的壞塊信息表標(biāo)記壞塊區(qū)域,以保證數(shù)據(jù)不被寫到壞塊區(qū)域。

(5)在對(duì)NAND Flash進(jìn)行擦除、編程或者讀取操作流程時(shí),不允許有中斷信號(hào)打斷CPU的工作,否則會(huì)讀寫錯(cuò)誤。在軟件設(shè)計(jì)時(shí),如果對(duì)NAND Flash進(jìn)行存取操作,需先屏蔽中斷,讀寫操作完成后再把中斷重新打開。

NAND Flash最基本的塊擦除、頁(yè)編程時(shí)序流程如圖4和圖5所示。

5 結(jié)束語(yǔ)

由于NAND Flash具有非易失性、大容量、低成本、接口簡(jiǎn)單等優(yōu)點(diǎn)。在組合導(dǎo)航數(shù)據(jù)存儲(chǔ)設(shè)備,激光慣導(dǎo)單元及紅外導(dǎo)引頭的圖像采集等智能儀器中得到廣泛應(yīng)用。詳細(xì)介紹了大容量閃存K9KAG08UOM與TMS320C6713B的硬件接口電路和軟件程序設(shè)計(jì),所采用的接口技術(shù)靈活、簡(jiǎn)單、可靠,在激光慣導(dǎo)單元進(jìn)行的湖試和海試試驗(yàn)中成功地實(shí)現(xiàn)了數(shù)據(jù)的存儲(chǔ)。該接口設(shè)計(jì)方法可推廣應(yīng)用于大容量閃存器件與單片機(jī)、ARM及其他型號(hào)的DSP設(shè)計(jì)中。