引言

DSP芯片具有高速的信息處理能力、較好的系統(tǒng)支持、硬件配置強(qiáng)等優(yōu)良技術(shù)和較低的價(jià)格特性。嵌入式系統(tǒng)的實(shí)時(shí)性好、占用資源少、功能強(qiáng)、可靠性高、模塊化結(jié)構(gòu)、便于移植和定制的特點(diǎn)。基于 DSP平臺(tái)的嵌入式系統(tǒng)具備上述兩者的優(yōu)點(diǎn),特別適用于一些帶各種便攜式系統(tǒng)終端 LCD且需要大量數(shù)據(jù)要處理的系統(tǒng)。

近年來(lái),DSP已經(jīng)越來(lái)越多地被應(yīng)用于數(shù)據(jù)采集、語(yǔ)音處理、圖像分析與處理等領(lǐng)域中,并且日益顯示出巨大的優(yōu)越性。而液晶顯示屏更以其顯示直觀、功耗低、便于操作的特點(diǎn)被用作各種便攜式的顯示前端。本文介紹了一種基于DSP 和 CPLD的液晶模塊的設(shè)計(jì)與實(shí)現(xiàn)方法,解決快速處理器與慢速外設(shè)的匹配問(wèn)題。 1系統(tǒng)總體設(shè)計(jì)

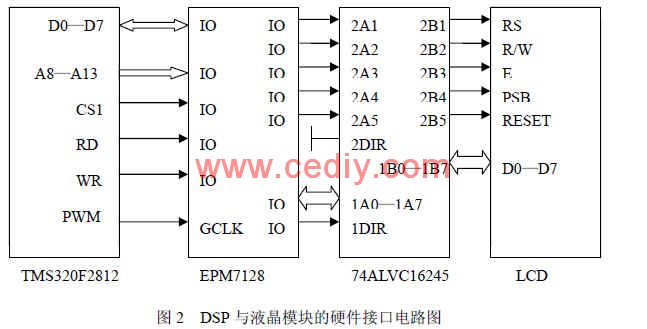

該顯示系統(tǒng)主要由DSP、CPLD、電平轉(zhuǎn)換和 LCD模塊四部分組成,如圖 1所示,

該系統(tǒng)中,DSP采用 TI公司的 TMS320F2812處理器。采用高性能靜態(tài)的 CMOS技術(shù),使得供電電壓降為 3.3V,降低了控制器的功耗;150MIPS的執(zhí)行速度使得指令周期縮短為6.67ns,從而提高了控制器的實(shí)時(shí)控制能力;可以進(jìn)行 16×16和 32×32的乘加操作,可以方便的進(jìn)行FFT、FIR濾波等數(shù)字信號(hào)處理算法;具有多達(dá) 56個(gè)通用、雙向數(shù)字 I/O引腳,能方便的實(shí)現(xiàn)各種 I/O操作。

CPLD 采用 Altera公司 MAX7000系列的 EPM7128SQC100,3.3V供電,不存在 DSP及 LCD電平兼容的問(wèn)題,采用 CMOS E2PROM工藝,傳輸延遲僅為5ns;具有 68個(gè)用戶可編程的 IO 口,為系統(tǒng)定義輸入、輸出和雙向口提供了極大的方便; EPM7128同時(shí)還提供了 JTAG接口,可進(jìn)行 ISP編程,極大地方便了用戶。本文采用CPLD 的主要目的是:對(duì)于 LCD顯示,將 DSP中的數(shù)據(jù)發(fā)送到CPLD,然后 DSP去做其它的事情,而后續(xù)的顯示任務(wù)由 CPLD完成,CPLD 將在 LCD允許的速度下對(duì)其進(jìn)行操作即可達(dá)到顯示的目的。

LCD 模塊采用成都飛宇達(dá)的 FYD12864-0402B,內(nèi)置 ST7920液晶控制器。它是一種具有 4位/8位并行、 2線或 3線串行多種接口方式,內(nèi)含中文字庫(kù)的點(diǎn)陣圖形液晶顯示模塊。其顯示分辨率為 128*64,內(nèi)置 8192個(gè) 16*16點(diǎn)漢字和 128個(gè) 16*8點(diǎn) ASCII字符集,強(qiáng)大的字庫(kù)省去了很多自行編碼的麻煩;可以顯示中文字型、數(shù)字符號(hào)、英文字母以及圖形等,利用該模塊靈活的接口方式和簡(jiǎn)單方便的操作指令,可構(gòu)成友好的中文人機(jī)交互界面。

硬件接口設(shè)計(jì)

由于 DSP屬于高速器件, LCD為慢速外設(shè),DSP對(duì)讀寫周期較慢的 LCD進(jìn)行訪問(wèn),可采用以下兩種方式來(lái)解決 DSP與 LCD的時(shí)序匹配問(wèn)題:直接訪問(wèn)和間接訪問(wèn)。直接訪問(wèn)是將 DSP的讀寫信號(hào)與 LCD接口的讀寫信號(hào)直接相連,將 LCD的 8位數(shù)據(jù)線與 DSP的低 8位數(shù)據(jù)線相連(在 CPLD內(nèi)部硬件編程完成),時(shí)序由 DSP內(nèi)部讀寫邏輯控制。由于 LCD的讀寫周期較 DSP慢,要使兩者的時(shí)序匹配,還必須進(jìn)行一些時(shí)序方面的處理。間接訪問(wèn)用 DSP的 I/O口間接控制慢速設(shè)備,可以通過(guò)軟件控制 DSP的 I/O口來(lái)實(shí)現(xiàn)與慢速外設(shè)的時(shí)序匹配。該方法無(wú)需通過(guò)硬件擴(kuò)展即可實(shí)現(xiàn)與任意慢速外設(shè)的時(shí)序匹配。在該顯示系統(tǒng)中,由于 CPLD的可在線硬件編程能力,這 2 種方法均可實(shí)現(xiàn)。這里采用第一種接法。 DSP與 LCD的硬件接口電路圖如圖 2所示。

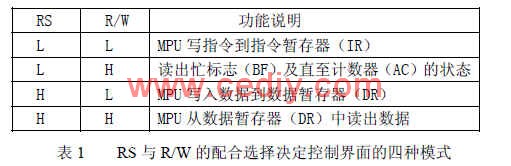

LCD 各引腳說(shuō)明如下:RS為高電平時(shí),DB7—DB0顯示數(shù)據(jù);RS為低電平時(shí),DB7—DB0顯示指令數(shù)。R/W為高電平時(shí),數(shù)據(jù)被讀到DB7—DB0; R/W為低電平時(shí),DB7—DB0的數(shù)據(jù)被寫到IR或 DR。E為使能信號(hào)線。當(dāng) E為高電平時(shí),配合 R進(jìn)行讀數(shù)據(jù)或指令,當(dāng) E為低電平時(shí),配合/W進(jìn)行寫數(shù)據(jù)或指令。PSB為高電平時(shí),表示 8位或四位并口方式;PSB為低電平時(shí),表示串口方式。RESET為復(fù)位信號(hào)輸入端,低電平有效。DB7—DB0為三態(tài)數(shù)據(jù)線。 其中 RS與 R/W配合決定控制界面的四種模式:

另外,由于 FYD12864用 5V供電,所以液晶的 8位數(shù)據(jù)線不能直接與 DSP的外部擴(kuò)展數(shù)據(jù)總線相連。本系統(tǒng)中采用 74ALVC16245來(lái)進(jìn)行電平轉(zhuǎn)換, 74ALVC16245是 16位的電源 轉(zhuǎn)換芯片,采用 3.3V供電,該芯片有兩個(gè)方向控制引腳( DIR1和 DIR2),DIR1由 CPLD的 I/O引腳供給,當(dāng) DSP從液晶讀取數(shù)據(jù)時(shí),DIR1為低電平,數(shù)據(jù)的傳輸方向是從液晶到 DSP;當(dāng) DSP往液晶寫數(shù)據(jù)時(shí),DIR1為高電平,數(shù)據(jù)傳輸方向是從 DSP到液晶。DIR2與 VCC相連,由 CPLD的 I/O引腳控制 LCD。 3 軟件編程及實(shí)例

本系統(tǒng)中,CPLD部分采用 VHDL進(jìn)行編程,主程序采用 C語(yǔ)言進(jìn)行編程,便于程序的移植,并使其具有較高的可讀性。首先解決 DSP與 LCD的時(shí)序匹配問(wèn)題,時(shí)序匹配是 DSP控制 LCD最關(guān)鍵的問(wèn)題,其實(shí)質(zhì)是如何編寫程序?qū)?LCD的指令寄存器和數(shù)據(jù)寄存器進(jìn)行讀寫操作,接口時(shí)序如圖 3和圖 4所示,

使用該顯示模塊時(shí)應(yīng)注意以下幾點(diǎn):(1)欲在某一個(gè)位置顯示中文字符時(shí),應(yīng)先設(shè)定顯示字符位置,即先設(shè)定顯示地址,再寫入中文字母編碼。(2)顯示 ASCII字符過(guò)程與顯示中文字符過(guò)程相同。不過(guò)在顯示連續(xù)字符時(shí),只須設(shè)定一次顯示地址,由模塊自動(dòng)對(duì)地址加 1指向下一個(gè)字符位置,否則,顯示的字符中將會(huì)有一個(gè)空 ASCII字符位置。(3)當(dāng)字符編碼為兩字節(jié)時(shí),應(yīng)先寫入高位字節(jié),再寫入低位字節(jié)。(4)模塊在接收指令前,處理器必須先確認(rèn)模塊內(nèi)部處于非忙狀態(tài),則讀取BF標(biāo)志,BF需為“0”,方可接收新的指令。如果在送出一個(gè)指令前不檢查 BF標(biāo)志,則在前一個(gè)指令和這個(gè)指令中間必須延遲一段較長(zhǎng)的時(shí)間,即等待前一個(gè)指令確定執(zhí)行完成。

通過(guò)初始化液晶顯示屏以及調(diào)用字庫(kù)顯示漢字和字符來(lái)具體說(shuō)明 DSP控制液晶顯示屏的設(shè)計(jì)思想。系統(tǒng)硬件上電復(fù)位后,首先完成 DSP的初始化,然后根據(jù)用戶系統(tǒng)的需要對(duì)控制器的各項(xiàng)指令代碼及其參數(shù)進(jìn)行設(shè)置,以完成液晶模塊的參數(shù)以及顯示方式等一系列過(guò)程的初始化。液晶模塊具體編程如下:

#include "DSP28_Device.h"

unsigned int * LcdComL = (unsigned int *) 0x5100;//命令寄存器低地址

unsigned int * LcdComH = (unsigned int *) 0x5200;//命令寄存器高地址

unsigned int * LcdDatL = (unsigned int *) 0x5300;//數(shù)據(jù)寄存器低地址

unsigned int * LcdDatH = (unsigned int *) 0x5400;//數(shù)據(jù)寄存器高地址

void WriteLcdCom(unsigned char c);//寫命令

void WriteLcdDat(unsigned char d);//寫數(shù)據(jù)

void delay(unsigned int t);//延時(shí)

void main(void)//主程序

{ InitSysCtrl();//初始化系統(tǒng)

DINT;// 關(guān)中斷

IER = 0x0000;

IFR = 0x0000;

InitPieCtrl();//初始化

PIE InitPieVectTable(); //初始化

PIE中斷矢量表

InitPeripherals();//初始化外設(shè)

LcdComL = 0x00;//初始化命令寄存器

LcdDatL = 0x00;//初始化數(shù)據(jù)寄存器

WriteLcdCom(0x01);//清除顯示屏

WriteLcdCom(0x0e);//顯示狀態(tài)打開(kāi)

WriteLcdCom(0x30);//LCD選擇為 8位并行數(shù)據(jù)傳輸方式

比如要在顯示屏第一行顯示“檢測(cè)物質(zhì):Theanol”

WriteLcdCom(0x80); //寫第一個(gè)字符的地址

WriteLcdDat(0xbc); //第一個(gè)漢字“檢”的高字節(jié)

WriteLcdDat(0xec);//“檢”的低字節(jié)

WriteLcdDat(0xb2);//漢字“測(cè)”高字節(jié)

WriteLcdDat(0xe2);//“測(cè)”低字節(jié)

WriteLcdDat(0xce);//漢字“物”高字節(jié)

WriteLcdDat(0xef);//漢字“物”低字節(jié)

WriteLcdDat(0xd6);//漢字“質(zhì)”高字節(jié)

WriteLcdDat(0xca);“質(zhì)”低字節(jié)

WriteLcdDat(0x3a);//冒號(hào)“: ”

WriteLcdDat(0x45);//字符“ T”

WriteLcdDat(0x74);//字符“ h”

… for(;;);

} void WriteLcdCom(unsigned char c) { * LcdComH = c;

* LcdComL=c;

delay(5000); } void WriteLcdDat(unsigned char d) { * LcdDatH = d;

* LcdDatL = d;

delay(5000); } void delay(unsigned int t) { while(t>0)

t--; }

以上程序均在 DSP集成開(kāi)發(fā)環(huán)境 CCS中調(diào)試通過(guò),LCD顯示屏上可以正常顯示連續(xù)的漢字、字符以及圖形等,在實(shí)際的嵌入式數(shù)據(jù)采集系統(tǒng)中得以應(yīng)用。通過(guò)移植本文的程序,修改其中一些命令,可以完成更加復(fù)雜的功能,并且具有縮短產(chǎn)品開(kāi)發(fā)周期,加快產(chǎn)品上市等優(yōu)點(diǎn),因此非常適合便攜式設(shè)備的界面顯示系統(tǒng)。

結(jié)論

本文作者創(chuàng)新點(diǎn):以 DSP為核心處理器,利用 CPLD來(lái)進(jìn)行邏輯轉(zhuǎn)換和控制,實(shí)現(xiàn)高速CPU處理器和低速外設(shè)接口的時(shí)序匹配,同時(shí)采用了移植性能和可讀性能高的 C程序設(shè)計(jì),無(wú)需插入等待周期,在實(shí)際的嵌入式系統(tǒng)中成功運(yùn)行,為快速處理器與慢速外設(shè)的接口設(shè)計(jì)提供了一種借鑒的方法。