隨著系統(tǒng)性能、功能和帶寬的日益增長,總線技術(shù)也在迅速的發(fā)展。海量存儲,衛(wèi)星通訊,高速數(shù)據(jù)采集與記錄以及其他數(shù)據(jù)處理的數(shù)據(jù)吞吐量現(xiàn)以KMbp s為量級,未來計算機系統(tǒng)對帶寬和擴展性的要求已經(jīng)超越了第二代總線技術(shù)。由英特爾提出的第三代高性能I/O總線技術(shù)—PCIE總線解決了PCI總線的不足,它的發(fā)展將取代PCI成為新型的數(shù)據(jù)總線,其提供了更加完善的性能,更多的功能,更強的可擴展性和更低的成本。

本文研究了采用NXP公司的PC I Exp ress接口協(xié)議芯片PX1011A和Xilinx公司Spartan - 3 FPGA實現(xiàn)PC IE接口的硬件電路設計以及使用Xilinx公司提供的PC I Exp ress LogiCORE IP核的軟件設計。

2 PCIE總線和PX1011A的介紹

2. 1 PCIE總線的介紹

PC I Exp ress是用來互連諸如計算和通信平臺應用中外圍設備的第三代I/O總線技術(shù),第一代總線包括ISA、E ISA、VESA和微通道(Micro Channel)總線,而第二代總線則包括了PCI、PC I - X和AGP。PCI Exp ress是一種能夠應用于一種設備、臺式電腦、工作站、服務器、嵌入式計算機和通信平臺等所有周邊I/O設備互連的總線。

PC IE最初由Intel發(fā)展,并于1992年在市場發(fā)布。PC IE的體系結(jié)構(gòu)繼承了第二代總線體系結(jié)構(gòu)最有用的特點,并且采用了計算機體系結(jié)構(gòu)中新的開發(fā)成果。它保留了原先的通訊模型和下載配置機制,但拋棄了共享總線的方式,采用點到點的總線連接方式。由于它提供了更高的性能特點和越來越大的帶寬,從而解決了PC I、PCI - X和AGP的許多缺點,是以后PC發(fā)展必然采用的接口總線,其必將取代PCI, PC I - X以及圖形加速器(AGP) 。

PC IE總線保留了對于PCI局部總線協(xié)議全部軟件的向下兼容性,即只要是PC IE的卡都可以插到帶有PCI的操作系統(tǒng)使用;在硬件上,兩者不兼容, PCIE取代PC I、PCI - X的并行多路總線結(jié)構(gòu),采用了一種串行、點到點的總線連接結(jié)構(gòu),需要的接口更少。

2. 2 單通道物理層收發(fā)器PX1011A

NXP公司的PX1011A 是一款與低成本FPGA一起使用而優(yōu)化的單通道2. 5Gbp s的PC I Exp ressPHY器件。它具有很小的封裝,可提供卓越的發(fā)射和接收性能,符合PCI Exp ress規(guī)范v1. 0a和v1. 1。它通過采用用于傳輸和接收數(shù)據(jù)的同步時鐘源來提高片外應用的性能。

數(shù)據(jù)由接收器的差分輸入接口進入PX1011A,在被傳送到解串化電路之前,這些數(shù)據(jù)將小振幅的差分信號變?yōu)檐墝壍臄?shù)字信號。一個載波檢測電路將檢測線路上是否有數(shù)據(jù)并將這些信息傳送到SERDES和PCS上。SERDES將這些數(shù)據(jù)串行為10位并行數(shù)據(jù)。然后PCS采用8位/10位解碼器來恢復成8位數(shù)據(jù)格式。

在發(fā)送過程中,來自P IPE接口的8位數(shù)據(jù)通過一個8位/10位編碼算法進行編碼。8 位/10 位編碼確保串行數(shù)據(jù)被直流平衡以避免交流耦合系統(tǒng)中的基帶漂移,它同時確保足夠的數(shù)據(jù)轉(zhuǎn)換以避免接收端的時鐘恢復。

PX1011A的MAC接口采用獨立的時鐘,由片內(nèi)100MHz的基準時鐘的鎖相環(huán)來產(chǎn)生。鎖相環(huán)有一個相對較高的帶寬來實現(xiàn)可選的擴頻并減少EM I。8bit 數(shù)據(jù)接口在250MHz 上運行并進行SSTL2信號發(fā)送,這種模式與流行的FPGA I/O接口兼容。

3 基于PX1011A收發(fā)器芯片的硬件電路設計

3. 1 PX1011A收發(fā)器芯片硬件電路設計

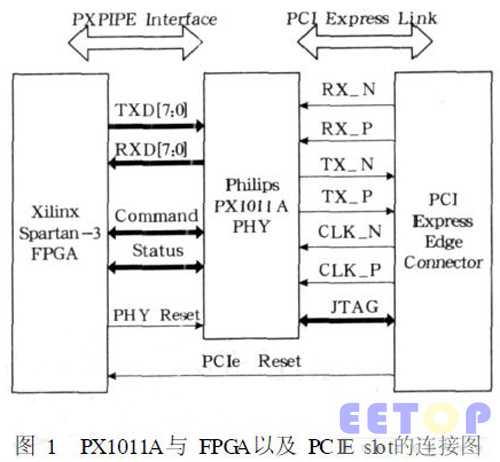

PC IE接口硬件電路如圖1 所示,包括三個部分:第一部分是PX1011A 與FPGA 的連接信號線,包括8位的接收發(fā)送信號TXD [ 7: 0 ]和RXD [ 7: 0 ] ,控制信號RX_DATAK、RX_VAL ID、RX_CLK、RX_E IDLE、RX_POLAR、RX_PHY_STAT、TX_DATAK、TX_CLK、TX_EIDLE、TX_COMP、TX_DET_LOOP、TX_PWRDN0、TX_PWRDN1,狀態(tài)信號STAT0、STAT1、STAT2和復位信號RESET。第二部分是PX1011A與PCIE接口的連接信號線,包括差分接收信號,差分發(fā)送信號, 差分時鐘信號。第三部分是PCIExp ress的配置接口,包括PCIE _ TMS、PCIE _ TCK、PCIE_TDO、PCIE_TD I和PCIE_TRST。

FPGA 選用Xilinx 公司的Spartan - 3 系列XC3S1000,采用90nm 材料生產(chǎn),容量高、成本低。具有業(yè)界一流的區(qū)塊和分布,具有多達784個I/O、MicroB laze 32位R ISC軟處理器和支持乘法累加器(MAC)功能(專用18x18乘法器提供高達3300 億

次MAC /秒)的嵌入XtremeDSP功能。

Xilinx Spartan - 3 PCI Exp ress設計包括一個PCI Exp ress P IPE Endpoint LogiCore。Xilinx低成本Spartan - 3系列提供PCI Exp ress協(xié)議層核。PC IE P IPE Endpoint LogiCORE整合了分立的PCIE PHY,提供了全面的、完全符合PC I Exp ress基礎規(guī)范( PCIExp ressBase Specification) v1. 1的PCIE端點解決方案。

3. 2 PCB布線

PCB布線時有以下注意點:終端阻抗布線盡量降低容性;一組信號,避免在參考層斷續(xù);高速信號盡量在一層布線,不要打孔,否則要在過孔處打一個U形的地孔;微波傳輸帶,差分信號布線線寬5mil,間距7mil;帶狀傳輸線,差分信號布線線寬5mil,間

距5mil。信號之間的間距在5 ×4 = 20mil以上,高壓和邊緣尖銳的信號盡量遠離差分線,避免干擾。

接口上數(shù)據(jù)采用SSTL2信號發(fā)送,傳送速率達到250MB / s。每組數(shù)據(jù)發(fā)送端需串行一個25歐姆電阻,數(shù)據(jù)接收端上拉50歐姆電阻,提高信號的阻抗匹配。TD和RX每組為8位250MB / s信號,為了減少信號間的延時誤差,每組信號布線時盡量等長。

4 P IPE Core實現(xiàn)PC IE總線協(xié)議

4. 1 Xilinx PC I Exp ress P IPE Core

Xilinx PCI Exp ress P IPE Core符合PC I Exp ress Base Specification v1. 1 規(guī)范的協(xié)議和電特性兼容,提供完整的端點解決方案,包括物理鏈接與處理和配置管理模塊。支持同步點對點通信,上行和下行流程控制,與PCI Exp ress處理排序規(guī)則完全兼容。有效的鏈接帶寬利用率,誤差檢測和恢復。支持最大為512字節(jié)的有效負載,經(jīng)過Xilinx專有的測試平臺驗證的設計,通過PC I - SIG的認證大會( com2p liance workshop) 。

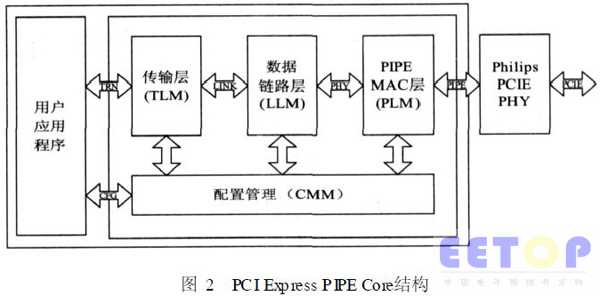

P IPE Core包括傳輸層,數(shù)據(jù)鏈路層,物理層,配置管理層四個模塊。這些模塊包括產(chǎn)生和進行傳輸包、數(shù)據(jù)流的控制管理,初始化,電源管理,數(shù)據(jù)保護,誤碼檢測,物理接口初始化,并串轉(zhuǎn)換以及其他的接口操作。各個模塊的具體連接關系如圖2 所

示。

4. 2 數(shù)據(jù)接收和發(fā)送的時序分析

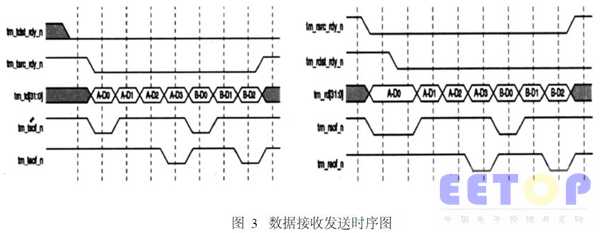

數(shù)據(jù)的接收和發(fā)送都包含以下接口信號:傳輸時鐘trn_clk,利用PCIE端口的100MHz差分時鐘輸入,通過Core的內(nèi)部DCM產(chǎn)生62. 50MHz時鐘,傳輸和配置模塊的操作都在trn_clk的上升沿變化;傳輸復位信號trn_reset_n,低有效;傳輸鏈路掛起信號

trn_lnk_up_n,在Core與連接方取消通信時產(chǎn)生,所有存在端口的傳輸包都會丟失。

發(fā)送數(shù)據(jù)端口包括P IPE Core準備接收32位數(shù)據(jù)的trn_ tdst_ rdy_n信號,用戶有效數(shù)據(jù)trn _ tsrc _rdy_n,發(fā)送32 位數(shù)據(jù)trn _ td [ 31: 0 ] ,幀開始信號trn_tsof_n和幀結(jié)束信號trn_tesof_n。接收端口第一個包的長度是其它包的兩倍,其余時序與發(fā)送信號類似,具體如圖3所示。

4. 3 FPGA設計

選用Xilinx公司的ISE軟件并采用Verilog硬件描述語言可對該IP核進行行為級描述和邏輯綜合,同時可將生成的網(wǎng)表文件設計實現(xiàn),包括邏輯綜合及布局布線。具體設計過程中,需要先加載P IPE Core,這要求ISE為8. 1 以上版本,同時要取得IP

Core的使用授權(quán)。

配置P IPE Core, 需要確定設備的生產(chǎn)廠商Vendor ID,設備編號Device ID,類型Class Code, I/O方式的地址存儲器空間BAR,有效載荷大小等信息。

在Core Generation之后,根據(jù)P IPE Core提供的文件加載各模塊的源文件。至此,帶PCIE總線協(xié)議的接口已經(jīng)建立好,用戶應用程序在模塊中添加。

5 結(jié)束語

實驗結(jié)果表明,以PX1011A 和Xilinx公司的Spartan - 3 FPGA搭建的×1 PCIE平臺最高傳輸速率可達150MB / s,能夠滿足高速信號傳輸?shù)男阅芤蟆kS著器件的發(fā)展和IP 核的開發(fā), 多通道的PCIE總線技術(shù)將會迅速發(fā)展。PCI Exp ress總線取代捉襟見肘的PCI總線已是大勢所趨,它能給電腦硬件的發(fā)展提供一種高性能的總線平臺,充分發(fā)揮各硬件子系統(tǒng)的性能,并為這些子系統(tǒng)今后的性能提升開辟更廣闊的空間。