目前,隨著多媒體應(yīng)用的普及,千兆位以太網(wǎng)已經(jīng)發(fā)展成為主流網(wǎng)絡(luò)技術(shù)。大到成千上萬人的大型企業(yè),小到幾十人的中小型企業(yè),在建設(shè)企業(yè)局域網(wǎng)時(shí)都會(huì)把千兆位以太網(wǎng)技術(shù)作為首選的高速網(wǎng)絡(luò)技術(shù)。千兆位以太網(wǎng)技術(shù)甚至正在取代ATM技術(shù),成為城域網(wǎng)建設(shè)的主力軍。

E1 接口采用PCM 編碼方式。符合G.703標(biāo)準(zhǔn),通過75Ω同軸電纜或120Ω雙絞線進(jìn)行非對(duì)稱或?qū)ΨQ傳輸。在電信網(wǎng)中有著廣泛應(yīng)用。

將高速的千兆位以太網(wǎng)信號(hào)與低速的E1信號(hào)結(jié)合起來,實(shí)現(xiàn)以太網(wǎng)與E1信號(hào)的復(fù)用。既滿足了用戶對(duì)大帶寬、高容量數(shù)據(jù)的傳輸要求,又提供了E1信號(hào)接入功能,實(shí)現(xiàn)電話業(yè)務(wù)及其他專用通信系統(tǒng)的接入功能。

系統(tǒng)構(gòu)成

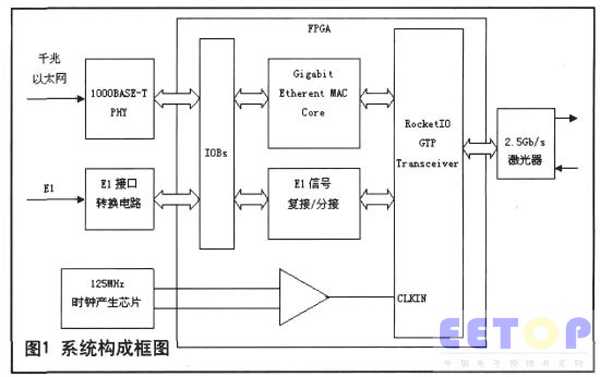

整個(gè)系統(tǒng)主要由E1接口單元、以太網(wǎng)接口單元、FPGA單元以及光接口單元構(gòu)成。E1接口單元主要完成E1信號(hào)的接口轉(zhuǎn)換,以太網(wǎng)接口單元主要通過外部PHY芯片實(shí)現(xiàn)物理層功能,再通過GMII接口實(shí)現(xiàn)與FPGA以太網(wǎng)媒體接入控制器對(duì)接。吉比特收發(fā)器通過用戶接口將以太網(wǎng)數(shù)據(jù)和經(jīng)過碼速調(diào)整后的E1信號(hào)形成16b并行數(shù)據(jù),再經(jīng)過16b/20b編碼形成2.5G b/s的數(shù)據(jù)流送入到光接口單元,光接口單元完成光/電轉(zhuǎn)化,實(shí)現(xiàn)信號(hào)的光纖傳輸。系統(tǒng)框圖如圖1所示。

E1接口單元的設(shè)計(jì)

在E1信道中,一般每8位組成一個(gè)時(shí)隙,32個(gè)時(shí)隙組成一個(gè)幀,16個(gè)幀組成一個(gè)復(fù)幀。在一個(gè)幀中,TS0主要用于傳送幀定位信號(hào)(FAS)、CRC - 4 ( 循環(huán)冗余校驗(yàn)) 和對(duì)端告警指示,TS16主要傳送隨路信令( CAS)、復(fù)幀定位信號(hào)和復(fù)幀對(duì)端告警指示,TS1 ~ T S15 和T S17 ~T S31共30個(gè)時(shí)隙則用來傳送話音或數(shù)據(jù)等信息。如果采用公共信道信令(CCS)模式,T S16就失去了傳送信令等信號(hào)的用途,TS1~TS31共31個(gè)時(shí)隙可傳送話音或數(shù)據(jù)等信息。如果采用無幀模式,E1信道將不成幀,而作為一個(gè)透明的話音或數(shù)據(jù)等信息傳輸通道。一個(gè)E1信道可傳送N個(gè)

64K b/s的話音或數(shù)據(jù)等信息通道。在隨路信令(CAS)模式,N為1~30;在公共信道信令(CCS)模式,N為1~31,而在無幀模式時(shí),N為32。

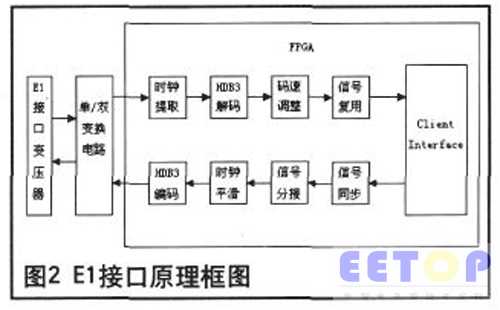

發(fā)送方向:E1信號(hào)首先經(jīng)過接口變壓器,然后送入單/雙變換電路,完成單雙變換后送入FPGA芯片。FPGA將E1線路接口單元送來的HDB3數(shù)據(jù)送入時(shí)鐘提取模塊,提取出E1時(shí)鐘,并且將HDB3數(shù)據(jù)轉(zhuǎn)換成NRZ數(shù)據(jù),NRZ數(shù)據(jù)經(jīng)碼速調(diào)整后復(fù)用成一路125M b/s數(shù)據(jù)流,然后送入RocketIO GTP Transceiver 發(fā)送接口單元中,和千兆位以太網(wǎng)信號(hào)一起進(jìn)行線路編碼,最后形成2.5G b/s的數(shù)據(jù)流送入到激光器進(jìn)行光線路編碼進(jìn)行傳輸。

接收方向:信號(hào)經(jīng)光纖傳輸后到達(dá)接收端,首先恢復(fù)成電信號(hào)送入到RocketIO GTP Transceiver接收單元中,經(jīng)時(shí)鐘提取、信號(hào)同步、解碼、信號(hào)分接,時(shí)鐘平滑后分接出E1數(shù)據(jù)流,再經(jīng)HDB3編碼后送入到單雙變換電路完成雙/單變化,經(jīng)接口變壓器后進(jìn)行傳輸。原理框圖如圖2所示。

千兆位以太網(wǎng)接口單元設(shè)計(jì)

千兆位以太網(wǎng)利用原以太網(wǎng)標(biāo)準(zhǔn)所規(guī)定的全部技術(shù)規(guī)范,其中包括CSMA/CD 協(xié)議、以太網(wǎng)幀、全雙工、流量控制以及IEEE802.3標(biāo)準(zhǔn)中所定義的管理對(duì)象。千兆位以太網(wǎng)的關(guān)鍵技術(shù)是千兆位以太網(wǎng)的MAC層和以太網(wǎng)接口的實(shí)現(xiàn)。

1 GMII (Gigabit MII)

GMII采用8位接口數(shù)據(jù),工作時(shí)鐘1 2 5 M H z , 因此傳輸速率可達(dá)1000Mb/s。同時(shí)兼容MII所規(guī)定的10/100M b/s工作方式。接口信號(hào)定義如表1所示。

2 Virtex-5以太網(wǎng)媒體接入控制器

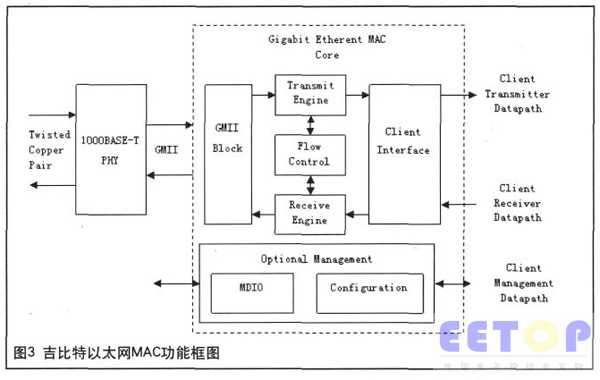

在V i r t e x-5 FPGA中,以太網(wǎng)媒體接入控制器(以太網(wǎng)MAC)模塊提供了專用的以太網(wǎng)功能,它和Virtex-5

RocketIO GTP收發(fā)器以及SelectIO技術(shù)相結(jié)合,能夠讓用戶與各種網(wǎng)絡(luò)設(shè)備進(jìn)行連接。在Virtex-5器件中,以太網(wǎng)MAC模塊作為一個(gè)硬件塊集成在FPGA內(nèi)部。吉比特以太網(wǎng)MAC功能框圖如圖3所示。

(1)客戶端接口

發(fā)送器的客戶端接口將幀傳送給以太網(wǎng)MAC。當(dāng)接收到的數(shù)據(jù)小于最短的以太網(wǎng)幀長(zhǎng)度時(shí),發(fā)送器將該數(shù)據(jù)加長(zhǎng),并且保持最小的幀間距;可以增加間隔的長(zhǎng)度,還可以通過配置發(fā)送器在幀中添加一個(gè)幀檢驗(yàn)序列。一個(gè)單獨(dú)的流控制接口允許你生成暫停幀。在半雙工模式下,信號(hào)發(fā)送之間存在沖突,在有效沖突情況下,需要進(jìn)行幀重發(fā)。

接收器接口檢驗(yàn)傳入幀和信號(hào)幀誤差。這里分別提供了好幀信號(hào)和壞幀信號(hào)。還可以通過配置以太網(wǎng)MAC以便在檢測(cè)到有效的暫停幀之后,暫停和重新啟動(dòng)幀傳輸。

客戶端接口的數(shù)據(jù)的寬度通常是8位或者16位。8位接口主要針對(duì)標(biāo)準(zhǔn)的以太網(wǎng)應(yīng)用,它利用一個(gè)125MHz的時(shí)鐘產(chǎn)生1000M b/s的數(shù)據(jù)傳輸速率。當(dāng)使用16位模式時(shí),可以在不提高客戶端接口時(shí)鐘頻率的條件下將數(shù)據(jù)傳輸速率提高到2000Mb/s。

(2)控制接口

每個(gè)以太網(wǎng)MAC有一個(gè)可選的管理數(shù)據(jù)I/O(MDIO)接口。它允許對(duì)外部PHY的管理寄存器和以太網(wǎng)MAC中PCS /PMA內(nèi)部的物理接口管理寄存器進(jìn)行訪問。

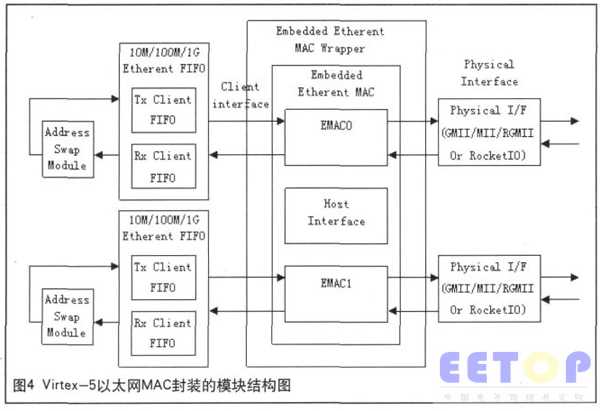

3 Virtex-5以太網(wǎng)MAC封裝

圖4 顯示了一個(gè)HDL 封裝的模塊結(jié)構(gòu)圖,它可以從Xilinx的COR EGenerator工具中獲得。

以太網(wǎng)MAC是一個(gè)具有162個(gè)端口和79個(gè)參數(shù)的復(fù)雜組件。封裝文件讓你可以僅對(duì)特定應(yīng)用所需端口的參數(shù)和接口輕松進(jìn)行設(shè)置。它們的另外一個(gè)優(yōu)勢(shì)是簡(jiǎn)化了時(shí)鐘和物理I/O資源的使用。

以太網(wǎng)MAC 封裝。在最低級(jí)別,實(shí)體化一個(gè)單獨(dú)的或者雙以太網(wǎng)MAC,同時(shí)在CORE Generator GUI中將它的屬性設(shè)置成你偏好的選項(xiàng)。所有未使用的輸入端口接地,未使用的輸出端口保持開路狀態(tài)。

模塊級(jí)別的封裝。在下一層級(jí),對(duì)物理接口以及所要求的時(shí)鐘資源進(jìn)行實(shí)體化。這包括用于串行接口的RocketIO GTP收發(fā)器。同時(shí)針對(duì)你的配置對(duì)時(shí)鐘進(jìn)行優(yōu)化,并且利用時(shí)鐘將輸出同步到你的設(shè)計(jì)。

Local Link級(jí)別的封裝。在該級(jí)別,將FIFO添加到客戶端發(fā)送器和接收器接口。FIFO能夠處理接收時(shí)壞幀的丟失并且以半雙工模式對(duì)幀重新傳輸。Local Link可以作為后端接口使用。

RocketIO GTP Transceiver

RocketIO是一種高速的串行收發(fā)器,采用兩對(duì)差分對(duì)來進(jìn)行數(shù)據(jù)的發(fā)送和接收,可以實(shí)現(xiàn)兩個(gè)單工或一對(duì)全雙工的數(shù)據(jù)傳輸。RocketIO支持622Mb/s ~3.75G b/s的全雙工傳輸速率,還具有8b/10b編解碼(平衡編碼)、時(shí)鐘生成及恢復(fù)等功能。Aurora協(xié)議是為專有上層協(xié)議或行業(yè)標(biāo)準(zhǔn)的上層協(xié)議提供透明接口的第一款串行互連協(xié)議,可用于高速線性通路之間的點(diǎn)到點(diǎn)串行數(shù)據(jù)傳輸,同時(shí)其可擴(kuò)展的帶寬,為系統(tǒng)設(shè)計(jì)人員提供了所需要的靈活性。

1 PMA和PCS層

RocketIO包括PMA(物理媒介適配層)和PCS(物理編碼子層)兩個(gè)子層,其內(nèi)部結(jié)構(gòu)如圖5所示。其中PMA子層主要用于串行化和解串,PCS主要包括線路編碼和CRC校驗(yàn)編碼。

PMA 子層中集成了SERDES,發(fā)送和接收緩沖,時(shí)鐘發(fā)生器及時(shí)鐘恢復(fù)電路。SERDES是一個(gè)串并轉(zhuǎn)換器,負(fù)責(zé)FPGA中本地的32位并行數(shù)據(jù)(也可以是16位或8位)與RocketIO接口的串行數(shù)據(jù)之間的轉(zhuǎn)換。采用串行數(shù)據(jù)收發(fā),可以在高頻條件下很好地避免數(shù)據(jù)間的串?dāng)_。時(shí)鐘發(fā)生器及時(shí)鐘恢復(fù)電路用于將時(shí)鐘與數(shù)據(jù)綁定發(fā)送,以及將時(shí)鐘從接收到的數(shù)據(jù)流中恢復(fù)出來,從而避免了在高速傳輸條件下時(shí)鐘與數(shù)據(jù)分開傳輸所帶來的時(shí)鐘抖動(dòng)等問題。

PCS子層負(fù)責(zé)8b/10b編碼解碼和CRC校驗(yàn),并集成了負(fù)責(zé)channel綁定和時(shí)鐘修正的彈性緩沖。8b/10b編碼可以避免數(shù)據(jù)流中出現(xiàn)連0連1的情況,便于時(shí)鐘的恢復(fù)。channel綁定通過在發(fā)送數(shù)據(jù)流中加入P字符來將幾個(gè)RocketIO通道綁定成一個(gè)一致的并行通道,從而來提高數(shù)據(jù)的吞吐率。最多支持24個(gè)通道的綁定。彈性緩沖可以解決恢復(fù)時(shí)鐘與本地時(shí)鐘的不一致問題,并進(jìn)行數(shù)據(jù)率的匹配,從而使得channel綁定成為可能。對(duì)RocketIO模塊的配置,可以通過下面兩種方式進(jìn)行:靜態(tài)特性可以通過HDL代碼設(shè)置;動(dòng)態(tài)特性可以通過RocketIO的原語(yǔ)端口進(jìn)行配置。

2 時(shí)鐘合成器

在實(shí)際設(shè)計(jì)中,高性能的通信質(zhì)量要求有高穩(wěn)定性和高精度的時(shí)鐘源,而抖動(dòng)和頻偏是衡量時(shí)鐘源的兩個(gè)重要指標(biāo)。RocketIO內(nèi)部的工作時(shí)鐘需要將輸入時(shí)鐘經(jīng)過數(shù)十倍的倍頻,但其可容忍的時(shí)鐘偏差為40ps,因此建議選擇高精度的差分時(shí)鐘。當(dāng)RocketIO在2.5Gb/s以上時(shí),參考時(shí)鐘應(yīng)采用差分輸入方式(例如LVDS、LVP ECL),由專用差分時(shí)鐘引腳輸入,然后引到相同或相鄰?fù)ǖ乐蠷ocketIO的參考時(shí)鐘輸入端;當(dāng)RocketIO在2.5Gb/s以下時(shí),不要使用FPGA內(nèi)部的DCM模塊來產(chǎn)生參考時(shí)鐘,因?yàn)榻?jīng)過DCM倍頻的時(shí)鐘會(huì)引入較大的抖動(dòng),使RocketIO的接收鎖相環(huán)無法穩(wěn)定地鎖定發(fā)送時(shí)鐘。

當(dāng)高精度時(shí)鐘輸入到FPGA中后,吉比特發(fā)送器對(duì)參考時(shí)鐘輸入管腳REFCLK的信號(hào)完成20倍倍頻操作后,來作為自己的工作時(shí)鐘。同樣,該倍頻器已集成在芯片中,不需要額外的組件。RXRECCLK和REFCLK二者之間沒有固定的相位關(guān)系,且都為專用時(shí)鐘信號(hào),不能連接到其他管腳上作為他用。當(dāng)使用4字節(jié)或1字節(jié)數(shù)據(jù)接收路徑時(shí),RXUSRCLK和RX U SRCLK2具有不同的頻率,但是頻率低的時(shí)鐘下降沿要和頻率高的時(shí)鐘下降沿對(duì)齊。同樣的關(guān)系也適用于TXUSRCLK和TXUSRCLK2信號(hào)。

RocketIO采集數(shù)據(jù)的同步時(shí)鐘則是通過時(shí)鐘/數(shù)據(jù)恢復(fù)電路來提取的,該電路由一個(gè)單片的PLL集成塊實(shí)現(xiàn),不需要任何外部組件。恢復(fù)電路從接收的數(shù)據(jù)流中提取出時(shí)鐘的頻率和相位,并通過20倍分頻后送到輸出管腳RXRECCLK上。

時(shí)鐘和數(shù)據(jù)恢復(fù)器:如果沒有數(shù)據(jù)存在,時(shí)鐘/數(shù)據(jù)恢復(fù)器(CDR)電路會(huì)自動(dòng)鎖相到參考時(shí)鐘上。為了使操作達(dá)到最優(yōu)性能,參考時(shí)鐘的精度必須在100×10-6之內(nèi)。同時(shí)要滿足供電系統(tǒng)的低噪聲。如果有數(shù)據(jù),則恢復(fù)電路會(huì)自動(dòng)同步鎖相到輸入數(shù)據(jù)上。

發(fā)送器:發(fā)送器模塊包括發(fā)送接口、8b/10b編碼器、不均勻控制、發(fā)送FIFO、串行器、發(fā)送終端以及預(yù)加重電路。

接收器:接收器模塊主要包括解串器、接收終端和8b/10b解碼器。

光接口單元

光接口單元主要包括光發(fā)射模塊和數(shù)字光接收放大器模塊。它們的功能分別是將電脈沖信號(hào)變換成光脈沖信號(hào)和將接收到的衰減變形的微弱光脈沖信號(hào)通過光/電轉(zhuǎn)換成電脈沖信號(hào)。光發(fā)射模塊把符合數(shù)字光纖通信系統(tǒng)傳輸性能要求的光脈沖波形從光源組件的尾纖發(fā)射出去。光接收放大器模塊由PIN+FET和放大電路組成。它將微弱光脈沖信號(hào)經(jīng)O/E轉(zhuǎn)換,并給予足夠的放大,還原成原來的數(shù)字脈沖信號(hào)。

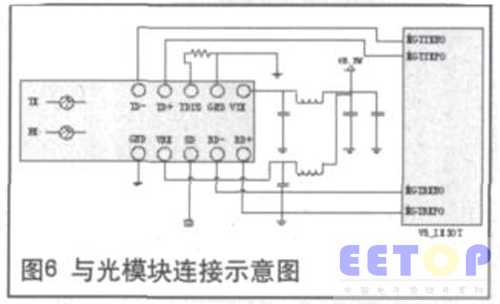

本設(shè)計(jì)選用飛通2 . 5 Gb/s 光模塊,中心波長(zhǎng)1550n m。傳輸距離可達(dá)40km。參考電路如圖6所示。

結(jié)束語(yǔ)

本文設(shè)計(jì)的基于Xilinx FPGA的千兆位以太網(wǎng)及E1信號(hào)的光纖傳輸系統(tǒng)采用Xilinx X C5VLX30T芯片,通過以太網(wǎng)測(cè)試儀和數(shù)據(jù)誤碼儀對(duì)本系統(tǒng)分別進(jìn)行性能測(cè)試,測(cè)試結(jié)果滿足設(shè)計(jì)要求,系統(tǒng)工作穩(wěn)定。從而實(shí)現(xiàn)了千兆位以太網(wǎng)信號(hào)和E1信號(hào)的接入功能,為用戶搭建了一個(gè)大容量、多業(yè)務(wù)的傳輸平臺(tái)。