賽靈思中國(guó)SystemIO專家FAE 楊寧

FPGA SERDES的應(yīng)用需要考慮到板級(jí)硬件,,SERDES參數(shù)和使用,,應(yīng)用協(xié)議等方面。由于這種復(fù)雜性,,SERDES的調(diào)試工作對(duì)很多工程師來(lái)說(shuō)是一個(gè)挑戰(zhàn),。本文將描述SERDES的一般調(diào)試方法,便于工程師準(zhǔn)確快速定位和解決問(wèn)題,。

1. 硬件檢測(cè)

硬件檢測(cè)可以分為原理圖/PCB檢查和板上硬件檢查,。這一部分的工作相對(duì)簡(jiǎn)單,但是很多時(shí)候問(wèn)題是由這些看起來(lái)很不起眼的地方導(dǎo)致的,。

a) 原理圖/PCB檢查

根據(jù)SERDES應(yīng)用手冊(cè)要求檢查原理圖和PCB設(shè)計(jì)。例如對(duì)于Xilinx 7系列GTX/GTH SERDES,,可以參考UG476的Board Design Guidelines檢查原理圖和PCB設(shè)計(jì),。

b) 板上硬件檢查

使用示波器/萬(wàn)用表等儀器設(shè)備實(shí)際測(cè)量板上硬件,確認(rèn)提供給SERDES的工作環(huán)境正常,。

i. 檢查電源的電壓/精度/紋波/上電順序是否符合數(shù)據(jù)手冊(cè)的要求,。例如對(duì)于Xilinx 7系列GTX SERDES,需要對(duì)照DS182檢查。

ii. 檢查SERDES參考時(shí)鐘頻率/擺幅是否符合數(shù)據(jù)手冊(cè)的要求,,以及參考時(shí)鐘的管腳位置是否正確,。

iii. 物理通道的檢查,例如確認(rèn)AC耦合電容的容值是否正確,,光模塊是否兼容,,焊接是否正常。

2. 使用IBERT

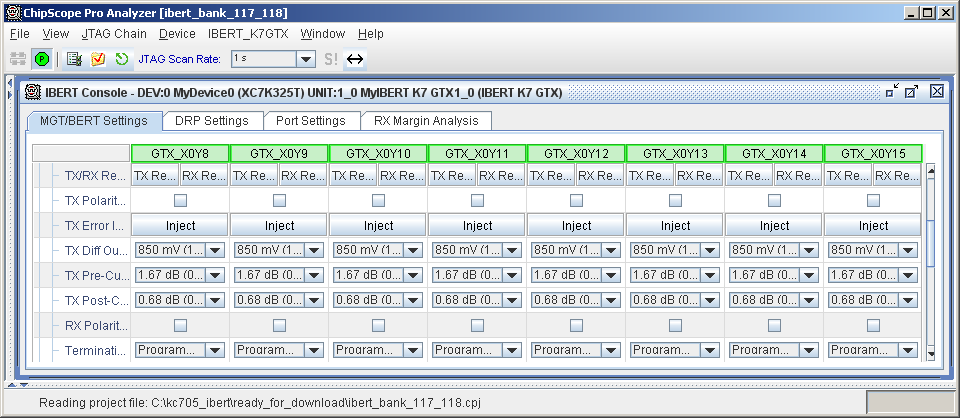

IBERT是一個(gè)強(qiáng)有力的調(diào)試工具,,可以用于調(diào)整參數(shù)設(shè)置和確認(rèn)系統(tǒng)余量,,也可以用于故障現(xiàn)象判斷。IBERT在CORE generator里產(chǎn)生工程和BIT文件,。將BIT文件下載到FPGA后,,使用ChipScope Analyzer連接到FPGA上,就會(huì)出現(xiàn)IBERT的GUI調(diào)試界面,。

a) 檢查PLL是否LOCK,,如果沒(méi)有,,需要檢查時(shí)鐘和電源,。比如時(shí)鐘頻率是否正確,SERDES是否選擇了正確的時(shí)鐘源,。

b) 將SERDES的TX和RX設(shè)為相同的數(shù)據(jù)pattern,,例如PRBS-31。設(shè)置SERDES為Near-end PMA模式,。如果這一步不能工作,,檢查TX/RX極性是否反轉(zhuǎn);檢查TXUSRCLK/TXUSRCLK2/RXUSRCLK/RXUSRCLK2上的時(shí)鐘頻率是否正常,。通過(guò)這一步保證SERDES內(nèi)部工作正常,。

c) 將SERDES設(shè)置為Far-end PMA和Far-end PCS模式,確認(rèn)遠(yuǎn)端設(shè)備的SERDES是否收發(fā)正常,。通過(guò)這一步排除和時(shí)鐘OFFSET相關(guān)的問(wèn)題,。

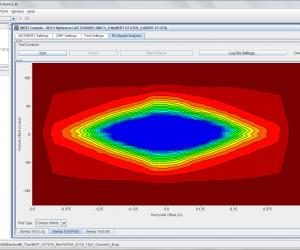

d) 如果這些步驟工作正常,但是誤碼率很高,,有可能是參數(shù)設(shè)置有問(wèn)題,。需要通過(guò)調(diào)整TX/RX的參數(shù)設(shè)置來(lái)解決。也可以通過(guò)EYE SCAN功能來(lái)得到最佳設(shè)置和判斷系統(tǒng)余量,。

3. 通用的調(diào)試步驟

通常會(huì)使用一定的調(diào)試步驟來(lái)定位問(wèn)題,,避免重復(fù)工作。一開(kāi)始,,一般不進(jìn)行整個(gè)工程的測(cè)試,,而是基于SERDES的Wrappers工程,以方便定位問(wèn)題。一般可以使用CORE generator里的Transceivers Wizard產(chǎn)生的Example Design,。在Core generator里產(chǎn)生Transceivers Wizard的Example Design后,,會(huì)輸出源文件和scripts。利用scripts可以直接產(chǎn)生運(yùn)行結(jié)果,。Example Design里的數(shù)據(jù)產(chǎn)生和檢測(cè)都是基于BRAM,,可以很方便的修改數(shù)據(jù)。在工程里面,,Chipscope VIOs and ILAs必須被加入到工程里面,,進(jìn)行控制和調(diào)試分析。

a) 進(jìn)行Near-end PCS測(cè)試,。

i. 啟動(dòng)SERDES復(fù)位(VIO),。

ii. 確認(rèn)復(fù)位結(jié)束(VIO)。

iii. 檢查SERDES狀態(tài)信號(hào)(VIO),。

iv. 使用計(jì)數(shù)器確認(rèn)時(shí)鐘頻率(VIO),。

b) 進(jìn)行Near-end PMA測(cè)試。

i. 確認(rèn)CDR工作正常,,檢測(cè)CDR產(chǎn)生的恢復(fù)時(shí)鐘(VIO),。

ii. Comma alignment和8B/10B狀態(tài)檢查(ILA)。

c) 正常操作檢測(cè)

i. 確認(rèn)clock correction電路狀態(tài)(ILA),。

ii. 確認(rèn)Channel bonding電路狀態(tài)(ILA),。

iii. 鏈路通訊檢查(ILA和VIO)。