引言

隨著嵌入式微處理器主頻的不斷提高,信號的傳輸處理速度越來越快,當(dāng)系統(tǒng)時鐘頻率達(dá)到100MHZ以上,傳統(tǒng)的電路設(shè)計方法和軟件已無法滿足高速電路設(shè)計的要求。在高速電路設(shè)計中,走線的等長、關(guān)鍵信號的阻抗控制、差分走線的設(shè)置等越來越重要。筆者所在的武漢華中科技大學(xué)與武漢中科院巖土力學(xué)所智能儀器室合作.以ARM9微處理器EP9315為核心的嵌入式系統(tǒng)完成工程檢測儀的開發(fā)。其中在該嵌入式系統(tǒng)硬件電路設(shè)計中的SDRAM和IDE等長走線、關(guān)鍵信號的阻抗控制和差分走線是本文的重點,同時以cirrus logic公司的網(wǎng)絡(luò)物理層接13芯片cs8952為例詳細(xì)介紹了網(wǎng)絡(luò)部分的硬件電路設(shè)計,為同類高速硬件電路設(shè)計提供了一種可借鑒的方法。

硬件平臺

2.1主要芯片

本設(shè)計采用的嵌入式微處理器是Cirrus Logic公司2004年7月推出的EP93XX系列中的高端產(chǎn)品EP9315。該微處理器是高度集成的片上系統(tǒng)處理器,擁有200兆赫工作頻率的 ARM920T內(nèi)核,它具有ARM920T內(nèi)核所有的優(yōu)異性能,其中豐富的集成外設(shè)接口包括PCMCIA、接口圖形加速器、可接兩組設(shè)備的EIDE、 1/10/100Mbps以太網(wǎng)MAC、3個2.0全速HOST USB、專用SDRAM通道的LCD接口、觸摸屏接口、SPI串行外設(shè)接口、AC97接口、6通道I2S接口和8*8鍵盤掃描接口.并且支持4組32位 SDRAM的無縫連接等。

主芯片豐富的外設(shè)接口大大簡化了系統(tǒng)硬件電路.除了網(wǎng)絡(luò)控制部分配合使用Cirrus Logic公司的100Base—X/10Base-T物理層(PHY)接口芯片CS8952外,其他功能模塊無需增加額外的控制芯片。

2.2系統(tǒng)主體結(jié)構(gòu)

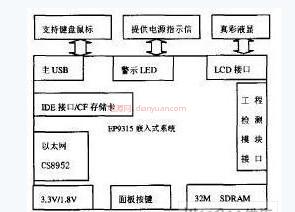

由圖1可見.系統(tǒng)以微處理器EP9315為核心,具有完備的外設(shè)接口功能,同時控制工程檢測儀。IDE/CF卡接口為工程檢測數(shù)據(jù)提供大容量移動存儲設(shè)備;擴(kuò)展32M的SDRAM作為外部數(shù)據(jù)存儲空間;3個主動USB接口支持USB鍵盤鼠標(biāo);LCD接口支持STN/TFT液晶和觸摸屏.為用戶提供友好的交互界面;1/10/100 Mbps以太網(wǎng)為調(diào)試操作系統(tǒng)時下載內(nèi)核及工程檢測時遠(yuǎn)程監(jiān)控提供途徑;面板按鍵為工程人員野外作業(yè)無法使用鍵盤鼠標(biāo)時提供人機(jī)交互接口。

EP9315在操作系統(tǒng)下主頻達(dá)到200M,總線頻率100M,外設(shè)時鐘為50M,數(shù)據(jù)線和地址線的布線密度大,速度高,網(wǎng)絡(luò)部分對差分線和微帶線控制有特殊要求。以往使用Protel設(shè)計主要依照經(jīng)驗進(jìn)行PCB布局布線,顯然這種方法無法滿足當(dāng)前的高速電路設(shè)計。CADENCE公司作為EDA領(lǐng)域最大的公司之一,其PCB設(shè)計工具性能上的優(yōu)勢在高速電路設(shè)計中越來越明顯,故筆者使用CADENCE公司的PCB設(shè)計布局軟件Allegro完成高速電路設(shè)計。

設(shè)計實現(xiàn)

3.1 SDRAM的布線規(guī)則

該嵌入式系統(tǒng)使用64M字節(jié)的SDRAM擴(kuò)展數(shù)據(jù)存儲區(qū),由兩片K4S561632組成工作在32位模式下。最高頻率可達(dá)100M以上,對于SDRAM的數(shù)據(jù)線、時鐘線、片選及其它控制信號需要進(jìn)行線長匹配,由此提出以下布線要求:

1. SDRAM 時鐘信號:時鐘信號頻率較高,為避免傳輸線效應(yīng),按照工作頻率達(dá)到或超過75MHz時布線長度應(yīng)在1000mil以內(nèi)的原則及為避免與相鄰信號產(chǎn)生串?dāng)_。走線長度不超過1000mil,線寬10mil,內(nèi)部間距5mil,外部間距30mil,要求差分布線,精確匹配差分對走線。誤差允許在20mil以內(nèi)。

2. 地址,片選及其它控制信號:線寬5mil,外部間距12mil,內(nèi)部間距10mil。盡量走成菊花鏈拓補(bǔ)。可有效控制高次諧波干擾,可比時鐘線長,但不能短。

3. SDRAM數(shù)據(jù)線:線寬5mil,內(nèi)部間距5mil,外部間距8mil,盡量在同一層布線,數(shù)據(jù)線與時鐘線的線長差控制在50mil內(nèi)。

根據(jù)布線要求,在Allegro中設(shè)置不同的約束:針對線寬設(shè)置3 個約束SDRAM_CLK,SDRAM_ADDDR,SDRAM_DATA,設(shè)置完約束后將約束添加到對應(yīng)的net上。使得各個net都具有線寬、線距約束屬性。最后為不同的信號組選擇合適的約束即可。但是設(shè)置的約束在系統(tǒng)CPU內(nèi)部是無法達(dá)到的。因為EP9315為BGA封裝。pin間距1.27毫米,顯然在CPU內(nèi)部,線寬線距無法達(dá)到上述要求,利用Allegro設(shè)置CPU特殊走線區(qū)域cpu_area。并加上area屬性,在此區(qū)域中另設(shè)置適合 BGA內(nèi)部走線的約束。

3.2 Xnet在IDE總線等長布線中的應(yīng)用

3.2.1系統(tǒng)中的IDE接口設(shè)計

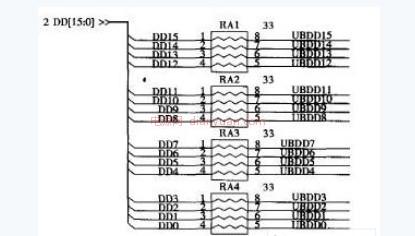

EP9315強(qiáng)大的外設(shè)接口能力能夠直接驅(qū)動IDE硬盤 ,布線時需要注意IDE總線的等長設(shè)置,但是IDE總線這類高速線需要端接匹配,可以防止信號反射和回流。如圖2所示其中的排阻起到了端接匹配的作用,但使得整個走線被分為好幾個NET,而Allegro中常用的走線長度設(shè)置 propagation_delay和relative_propagation_delay只能針對同一NET設(shè)置.IDE總線信號由EP9315扇出,要求EP9315到IDE接口走線DD*+UBDD*(如圖2中NET)等長,誤差為+/-20mil,最簡單的方法是分別設(shè)置DD*等長和 UBDD*等長,誤差各位+/-10mil,就可以達(dá)到要求,但是增加了布線難度,特別當(dāng)DD*有較大繞線空間。而UBDD*沒有足夠繞線空間時。這樣設(shè)置等長不可行。Allegro提供了一種方法,將DD*和UBDD*走線相加再進(jìn)行等長比對,這就要用到Xnet。

3.2.2 Xnet概念和Xnet等長設(shè)置

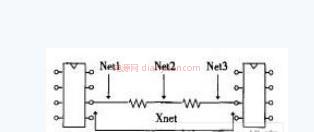

通常把連續(xù)的幾段由無源元件(電阻,電容或電感)連接的NET合稱為Xnet,如圖3所示。

Xnet示例

圖2中將DD*和UBDD*設(shè)置為同一個Xnet。對屬于該Xnet的所有信號等長控制。Xnet等長設(shè)置分為以下步驟:

1.設(shè)置Xnet

選擇要設(shè)置Xnet的器件(圖2中為排阻RA1-RA4),創(chuàng)建ESpiceDevice model,Allegro將自動填入模型名稱,電路類型-Resistor,PIN連接順序:1,8,2,7,3,*,5,表示1和8是一個電阻 (見圖2)。至此,查看排阻兩邊NET都添加了同一Xnet屬性。

2.Xnet的等長設(shè)置

(1)建立Xnet的pin pair:在Allegro中打開constraint manager,選擇relative_propagation_delay屬性。已設(shè)置的Xnet自動顯示,選擇Xnet建立pin pair,Allegro提供整個項目中Xnet關(guān)聯(lián)的起始pin和結(jié)束pin。選擇需要等長設(shè)置的起始pin和結(jié)束pin。

(2)建立等長 group:選中所有需要設(shè)置等長的pin pair,創(chuàng)建名為R_IDE_DATA的MATCH GROUP,在與relative_ propagation_delay對應(yīng)的工作窗體選擇區(qū)中出現(xiàn)了剛創(chuàng)建的R_IDE_DATA,其內(nèi)含建立的pin pair,按照IDE總線走線等長要求設(shè)置走線誤差10mil以內(nèi),一般選擇最長走線為基準(zhǔn)線(target)。

(3)走線完成后,重新打開constrait manager對實際走線進(jìn)行分析,Allergo自動顯示分析結(jié)果,綠色表示走線以基準(zhǔn)線為標(biāo)準(zhǔn)。走線誤差在10mil以內(nèi)。紅色表示走線誤差超過 10mil,如果分析結(jié)果,大部分走線都為紅色,可以適當(dāng)調(diào)整基準(zhǔn)線的選擇。

此外,Allegro在等長走線時。會實時顯示走線長度是否在誤差范圍內(nèi),可以使用蛇型線調(diào)整走線長度。這些都極大的確保了布線可靠性。

3.3差分線和阻抗控制在網(wǎng)絡(luò)布線中的應(yīng)用

3.2.1物理層接口芯片cs8952布線準(zhǔn)則

CS8952使用CMOS技術(shù)。提供一個高性能的100Base-X/10Base-T物理層(PHY)線路接口。它使自適應(yīng)均衡器達(dá)到最優(yōu)化的抗擾性和抗近端串?dāng)_(NEXT)性。可將接收器的應(yīng)用擴(kuò)展至超過160米的電纜,它結(jié)合了一個標(biāo)準(zhǔn)介質(zhì)無關(guān)端口(MII),可簡便地連接微處理器 EP9315的介質(zhì)訪問控制器(MAC)。

以下一些PCB布線規(guī)則,將使得CS8952工作更加穩(wěn)定并得到良好的EMC性能:

1. 使用多層電路板,至少有一個電源層,一個地層,疊層設(shè)置為:top,gnd,VCC,bottom。使用底層pcb走信號線只作為第二選擇。把所有的元件都放在頂層。然而,旁路電容優(yōu)選越靠近芯片越好,最好放置在CS8952下方的底層pcb上。RJ45終端元件和光纖元件可以選擇放在底層。

2.4.99k的參考電阻應(yīng)該越靠近RES管腳越好,把電阻另外一端使用一個過孔接到地平面。鄰近的vss(85和87腳)接在電阻接地端,形成一個屏蔽。

3.對關(guān)鍵信號Tx+/-,RX+/-,RX_NRz+/-控制阻抗,作為微帶傳輸線(差分對100歐,單線60歐),MII信號作為68歐微帶傳輸線。

4.差分傳輸線布線應(yīng)靠近(線寬間距6-8mil),與其他走線、元件保證2個線寬的距離。TX和RX差分對布線遠(yuǎn)離彼此。必要時使用pcb的相對面。

3.2.2網(wǎng)絡(luò)部分關(guān)鍵信號差分走線和阻抗控制的設(shè)置

網(wǎng)絡(luò)部分差分線及其阻抗控制以信號Tx+/-為例。步驟如下:

1.在Allegr o的assign diff pair菜單中選擇建立差分對的信號Tx+/-,命名為TX_Pair。

2.按照對信號TX+/-阻抗控制要求計算差分對線寬、線距,如圖4所示,選擇走線層面top層,填入差分對阻抗100歐,單線阻抗60歐,得到線寬10.1mil,主要線間距8.1mil。

3.定義差分對TX_PAIR電氣約束條件:

主要線寬,線間距:10mil/8mil;

次要線寬/線間距:10mil/8mi;

線最小間距:6mil;

兩條線無法走到一起時允許的線長:100mil;

兩條線可允許的誤差值:25mil。

4.分配差分對TX_PAIR到電氣約束集,打開差分對DRC模式。

以上實現(xiàn)差分對走線和阻抗控制的方法在涉及到大量差分對的通信系統(tǒng)電路中非常簡單實用。

結(jié)語

筆者利用強(qiáng)大的PCB設(shè)計軟件Allegro實現(xiàn)了基于EP9315嵌入式系統(tǒng)的硬件電路設(shè)計。該板采用6層PCB布線,完全滿足高速電路設(shè)計中對等長、差分、阻抗控制的要求。 基于該電路設(shè)計的嵌入式系統(tǒng)與武漢中科院巖土力學(xué)所設(shè)計的SY5聲波工程檢測儀實現(xiàn)了良好接口,與由51單片機(jī)搭建的原 SY5 聲波儀相比,改系統(tǒng)功耗降低,體積變小,穩(wěn)定性增強(qiáng),成本降低,更適合工業(yè)控制中的運用。