摘要:對(duì)二維信號(hào)實(shí)時(shí)處理涉及大量的復(fù)數(shù)運(yùn)算且對(duì)運(yùn)算速度要求很高,因此二維有限長單位脈沖響應(yīng)濾波器(2D—FIR)的結(jié)構(gòu)比一維濾波器要復(fù)雜得多。通過對(duì)二維濾波器重要運(yùn)算單元復(fù)數(shù)乘法的分析、優(yōu)化減小了其所需實(shí)數(shù)乘法器的個(gè)數(shù)。采用Quartus II軟件綜合可以得到算法優(yōu)化后的二維濾波器占用邏輯資源減少了16%,工作速度提高了13%。

關(guān)鍵詞:現(xiàn)場(chǎng)可編程門陣列;二維有限長單位脈沖響應(yīng)濾波器:復(fù)數(shù)乘法;信號(hào)處理

二維有限長單位脈沖響應(yīng)濾波器(2D—FIR)用于對(duì)二維信號(hào)的處理,如在通信領(lǐng)域中廣泛采用2D-FIR完成對(duì)I、Q兩支路基帶信號(hào)的濾波[1]。由于涉及大量復(fù)數(shù)運(yùn)算并且實(shí)時(shí)性要求高,如果不對(duì)算法作優(yōu)化在技術(shù)上很難實(shí)現(xiàn)。目前主要設(shè)計(jì)方案是利用FPGA廠商提供的一維FIR知識(shí)產(chǎn)權(quán)核(IP),組成二維濾波器[2]。這種方案沒有考濾復(fù)數(shù)運(yùn)算的特點(diǎn),不可能在算法上優(yōu)化,而且IP核的內(nèi)部代碼是不可修改的,因此在不同廠商的器件上不可移植。2D_FIR的復(fù)數(shù)運(yùn)算都需轉(zhuǎn)成實(shí)數(shù)運(yùn)算來實(shí)現(xiàn)的,而其中實(shí)數(shù)乘法運(yùn)算占用邏輯資源遠(yuǎn)比實(shí)數(shù)加法多。通過分析復(fù)數(shù)乘法特點(diǎn),減小其所需實(shí)數(shù)乘法器個(gè)數(shù)就可以減小邏輯資源占用率并提高運(yùn)算速度。這種方案優(yōu)點(diǎn)在于直接優(yōu)化算法,不會(huì)受IP核限制可移植性很強(qiáng)。

1 2D—FlR的設(shè)計(jì)

采用FPGA設(shè)計(jì)復(fù)數(shù)FIR濾波器常見的方案[2]為:用FPGA廠商提供的4個(gè)實(shí)數(shù)FIR濾波器IP核組合成2D—FIR濾波器。很明顯這種設(shè)計(jì)沒有考慮復(fù)數(shù)運(yùn)算的特點(diǎn),2D—FIR濾波器占用資源至少4倍于實(shí)數(shù)FIR濾波器,硬件資源耗費(fèi)過大,性能也會(huì)受到不小的影響。因此從算法上分析并優(yōu)化濾波器的結(jié)構(gòu)非常必要。

1.1 算法優(yōu)化

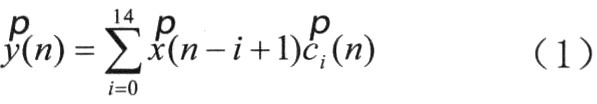

2D—FIR濾波器結(jié)構(gòu)采用卷積型,它對(duì)輸入數(shù)據(jù)的處理就是進(jìn)行卷積運(yùn)算[3],如(1)式所示:

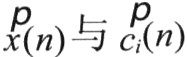

(1)式中各量全為復(fù)數(shù):xρ(n)為輸入數(shù)據(jù) 為濾波器抽頭系數(shù)。由(1)式可以看出其運(yùn)算過程是

為濾波器抽頭系數(shù)。由(1)式可以看出其運(yùn)算過程是 先作復(fù)數(shù)乘法運(yùn)算,再將乘積結(jié)果作復(fù)數(shù)加法得到

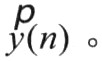

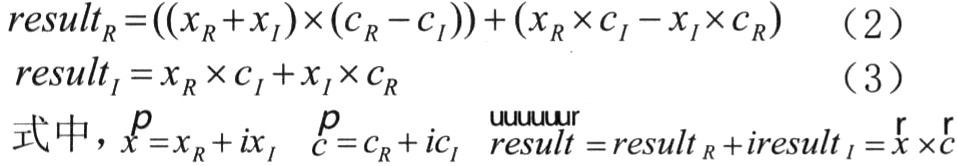

先作復(fù)數(shù)乘法運(yùn)算,再將乘積結(jié)果作復(fù)數(shù)加法得到 一個(gè)復(fù)數(shù)乘法由4個(gè)實(shí)數(shù)乘法和2個(gè)實(shí)數(shù)加法構(gòu)成。而相同位數(shù)的實(shí)數(shù)乘法器與實(shí)數(shù)加法器相比會(huì)占更多的硬件資源,也會(huì)對(duì)電路性能產(chǎn)生更多的負(fù)面影響。通過優(yōu)化后的復(fù)數(shù)乘法如下:

一個(gè)復(fù)數(shù)乘法由4個(gè)實(shí)數(shù)乘法和2個(gè)實(shí)數(shù)加法構(gòu)成。而相同位數(shù)的實(shí)數(shù)乘法器與實(shí)數(shù)加法器相比會(huì)占更多的硬件資源,也會(huì)對(duì)電路性能產(chǎn)生更多的負(fù)面影響。通過優(yōu)化后的復(fù)數(shù)乘法如下:

比較(2)式和(3)式可以得到兩個(gè)式子中xR×CI、xI×CR是共有項(xiàng),故優(yōu)化后的復(fù)乘法器需3個(gè)實(shí)數(shù)乘法器和5個(gè)實(shí)數(shù)加法器。如果抽頭系數(shù)為常數(shù)cR-cI,可以事先計(jì)算,還可以省一個(gè)加法器。通過Quartus II編譯、分析可以看到復(fù)乘法器性能提升了近14%,同時(shí)器件資源占用卻下降了17%。因?yàn)闉V波器共需15個(gè)復(fù)乘法器所以總體上減小的邏輯單元非常可觀。

1.2 FPGA實(shí)現(xiàn)

考慮到2D—FIR濾波器的運(yùn)用背景,除HDTV信道中要求抽頭數(shù)大于100以外抽頭數(shù)定為15已能滿足一般通信系統(tǒng)的要求,輸入數(shù)據(jù)和抽頭系統(tǒng)數(shù)據(jù)寬度都為16位。其中,輸入數(shù)據(jù)整數(shù)位(含符號(hào)位)為4位,小數(shù)位為12位,抽頭系數(shù)整數(shù)位為(含符號(hào)位)3位,小數(shù)位為13位,輸出數(shù)據(jù)與輸入數(shù)據(jù)位寬選取一樣。FPGA實(shí)現(xiàn)浮點(diǎn)小數(shù)運(yùn)算代價(jià)太大,解決小數(shù)運(yùn)算的方法是將小數(shù)表示為帶符號(hào)的整數(shù)[2],運(yùn)算后再對(duì)結(jié)果進(jìn)行截尾處理。

由于2D—FIR濾波器中有很多乘法和加法器,它們都是大型組合邏輯電路,所以需要在電路上進(jìn)一步優(yōu)化。引入多級(jí)流水線是提升電路工作速度很有效的方法[4],文獻(xiàn)[2]所采用的轉(zhuǎn)置卷積型濾波器結(jié)構(gòu)實(shí)質(zhì)是在乘法器之間加入了一級(jí)流水線,但相對(duì)于多級(jí)流水線其對(duì)電路性能提升并不大。本文加流水線具體的做法是用寄存器將組合電路分成若干延時(shí)相近的小型組合電路,同時(shí)將乘法和加法器分別設(shè)置為3級(jí)和2級(jí)流水線以滿足流水線配平原則。FPGA選用Altera公司專用于數(shù)字信號(hào)處理的EPlS20芯片,經(jīng)過Quartus II編譯后從報(bào)告中看到濾波器工作頻率為146MHz,占用芯片54%的邏輯資源。

2 仿真及結(jié)論

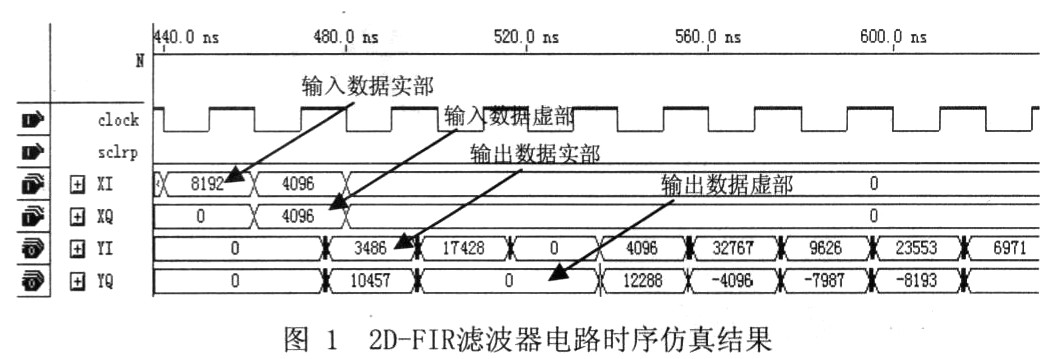

電路仿真結(jié)果如圖1所示,輸入數(shù)據(jù)為[1+3*i,5,0,0,0 0,0,2,3.5,1+2*i,0,0…],抽頭系數(shù)在模塊中設(shè)為[0.851*i,0,0,1,-i,1.15-0.4.i,0,0,0,i, 0, 0, 0, 0,圖1 2D—FIR濾波器電路時(shí)序仿真結(jié)果

0.1*i]。為了方便驗(yàn)證仿真結(jié)果,事先計(jì)算出輸出數(shù)據(jù)并轉(zhuǎn)化為帶符號(hào)位的整數(shù)[-10457+3486i,0+17428i,0,4096+12288i,32768—4096i,9626—7987i…]。從圖3中的仿真結(jié)果可以看到,經(jīng)過十幾個(gè)時(shí)鐘周期的延時(shí)后復(fù)數(shù)FIR濾波器的輸出為[3486+10457 i,17428,0,4096+12288i,32767-4096i,9626-7987i…],前面兩個(gè)數(shù)據(jù)與計(jì)算結(jié)果不一致是因?yàn)椋簭?fù)濾波器剛開始工作時(shí)內(nèi)部移位寄存器默認(rèn)的數(shù)據(jù)是0而不是外部輸入的數(shù)據(jù),當(dāng)數(shù)據(jù)全部裝載入濾波器后,計(jì)算結(jié)果完全滿足設(shè)計(jì)要求。

通過對(duì)算法與電路的優(yōu)化使2D—FIR濾波器的性能提高了13%,邏輯資源的占用減小了16%。文中所提出的方案比常規(guī)方法更有效,而且具有更強(qiáng)的可移植性。