隨著單電源運(yùn)放的廣泛的運(yùn)用,運(yùn)放的軌至軌輸入(rail to rail input)成為一個(gè)時(shí)髦的詞。現(xiàn)在大部分低電壓單電源供電的運(yùn)放都是軌至軌輸入的。TI在軌至軌輸入的運(yùn)放產(chǎn)品方面具有十分領(lǐng)先的優(yōu)勢(shì)。本文介紹運(yùn)放的rail to rail輸入的實(shí)現(xiàn)以及TI在實(shí)現(xiàn)運(yùn)放的rail to rail 輸入方面的領(lǐng)先技術(shù)。

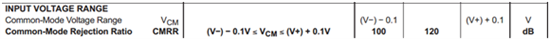

先說兩句廢話,解釋一下軌至軌,這里的軌指的是電源軌,運(yùn)放的兩個(gè)電源供電電壓如+/-15V。這兩個(gè)電源電壓就像兩條平行的距離為30V的“軌道”一樣限制了運(yùn)放的輸入輸出信號(hào)。運(yùn)放的軌至軌輸入是指運(yùn)放的輸入端信號(hào)電壓能夠達(dá)到電源的兩個(gè)軌,并保持不失真,如上例輸入信號(hào)電壓可達(dá)到+/-15V。運(yùn)放的輸入電壓范圍可在運(yùn)放的datasheet中找到。就是共模電壓范圍Vcm(Common-Mode Voltage Range)。如下表即為OPA365的輸入電壓范圍,可見它是典型的軌至軌輸入運(yùn)放。

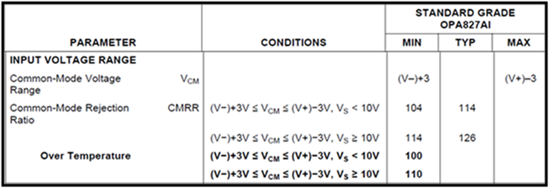

一般的BJT和JFET是非軌至軌輸入的運(yùn)放。如下表所示為OPA827共模輸入電壓范圍為(V-)+3V至(V+)-3V,典型的非軌至軌運(yùn)放。

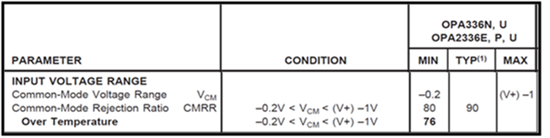

單電源(我們暫且稱之為“單電源”)運(yùn)放的輸入級(jí)通常有三種結(jié)構(gòu),第一種是采用PMOS做差分輸入級(jí)。這樣的運(yùn)入輸入級(jí)電壓可以低于負(fù)電源軌0.2甚至0.3V,但達(dá)不到正電源軌,如OPA336。下表是datasheet中標(biāo)出的OPA336輸入電壓范圍。

它的輸入級(jí)原理框圖如下圖,典型的PMOS差分輸入級(jí)。

既然PMOS差分輸入級(jí)輸入電壓不能達(dá)到正電源軌,那NMOS呢,對(duì)頭,NMOS差分輸入級(jí)的輸入電壓可以達(dá)到正電源軌,但是達(dá)不到負(fù)電源軌,一般會(huì)在負(fù)電源軌的1.2V之上。

此時(shí)有人想到了,把PMOS和NMOS差分輸入級(jí)并聯(lián)起來。在接近電源負(fù)電壓軌時(shí)使PMOS差分輸入級(jí)工作,在接近電源正電源軌時(shí)使NMOS差分輸入級(jí)工作。這樣不就可以實(shí)現(xiàn)運(yùn)放的軌至軌輸入了嘛。太巧妙了。的確早先的軌至軌輸入運(yùn)放就是這樣設(shè)計(jì)的。并且現(xiàn)在也在大量使用這種技術(shù)。如下圖是OPA703的輸入級(jí),就是典型的PMOS與NMOS相并聯(lián)的運(yùn)放輸入級(jí)。當(dāng)輸入共模電壓在(Vss-)-0.3V

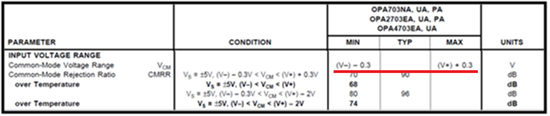

下表是OPA703的datasheet中給出的共模電壓輸入范圍(V-)-0.3V至(V+)+0.3V.

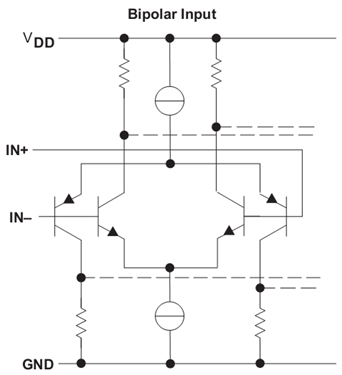

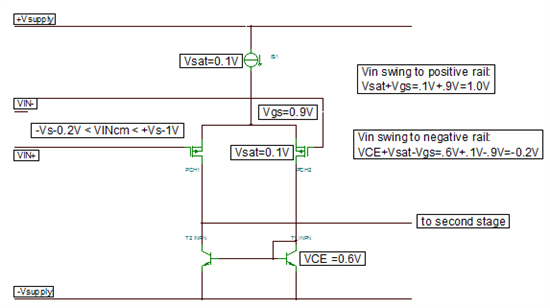

Bipolar輸入級(jí)運(yùn)入同樣也有這樣的結(jié)構(gòu),如下圖是典型PNP與NPN型三級(jí)管并聯(lián)形成的差分輸入級(jí)。