此前,我已經(jīng)發(fā)表了有關(guān)如何測(cè)試電源設(shè)計(jì)的三篇文章中的前兩篇,即效率測(cè)量(第 1 篇)和噪聲測(cè)量(第 2 篇)。文章主要涵蓋各種噪聲源以及如何使用示波器正確測(cè)量噪聲。此外,我還討論了由線路及負(fù)載瞬態(tài)產(chǎn)生的輸出錯(cuò)誤問題。

今天,我要談?wù)勲娫礈y(cè)試的第三個(gè)也是最后一個(gè)指標(biāo):穩(wěn)定性測(cè)量。

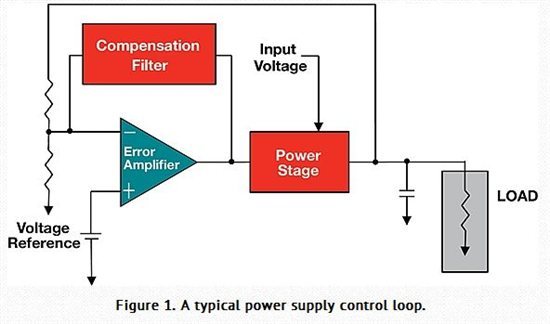

電源屬于閉環(huán)放大器,負(fù)責(zé)吸收電能并將其轉(zhuǎn)換成具有特定穩(wěn)壓和/或電流的另一種電能形式。電源的穩(wěn)壓原理是傳感輸出并將輸出的一部分與參考電壓相比較。將傳感信號(hào)與參考信號(hào)的差值進(jìn)行放大,然后用于控制穩(wěn)壓器的功率級(jí),以保持電壓(或電流)恒定。(圖 1)。

電源采用從輸出回到誤差放大器的負(fù)反饋確保其在各種工作條件下(負(fù)載變化、溫度變化以及輸入電壓變化等)的正確穩(wěn)壓。與任何穩(wěn)定閉環(huán)系統(tǒng)一樣,電源也必須確保在工作頻率或風(fēng)險(xiǎn)振蕩和/或其它不適應(yīng)特性下閉環(huán)增益小于 1。電源負(fù)反饋條件必須與輸入完全呈異相性或者構(gòu)建小于 1 的增益,才能確保正確的工作。

典型的穩(wěn)壓器 IC 可在設(shè)備內(nèi)提供必要的相位裕度,以確保穩(wěn)定的工作。與所有工程師一樣,IC 設(shè)計(jì)人員也需要進(jìn)行工作極限假設(shè),并經(jīng)常提供用于調(diào)整內(nèi)部相位延遲的控制機(jī)制,才能適應(yīng)各種負(fù)載極限。可設(shè)計(jì)一款穩(wěn)壓器來(lái)提供具有額定輸出阻抗的 90 度相位裕度。但如果該阻抗電容性比預(yù)期的要強(qiáng),相位延遲就可能增加到與內(nèi)部反饋點(diǎn)相同的相位點(diǎn)(也是從電源輸出返回的相位點(diǎn))。這種相位反轉(zhuǎn)會(huì)產(chǎn)生增益大于 1 的正反饋(振蕩器公式)。我們都很清楚這在穩(wěn)壓器電路中是不合適的。

許多穩(wěn)壓器都提供用于調(diào)整內(nèi)部相位延遲的機(jī)制,通常通過具有幾個(gè)無(wú)源組件的外部補(bǔ)償網(wǎng)絡(luò)來(lái)實(shí)現(xiàn)。但在某些情況下,穩(wěn)壓器并不提供這種機(jī)制,必須在特定工作極限內(nèi)使用(各種負(fù)載極限下的最小/最大輸出阻抗)。無(wú)論哪種情況,都必須對(duì)電路進(jìn)行正確分析,才能確定是否有必要進(jìn)行設(shè)計(jì)調(diào)整。雖然可對(duì)環(huán)路特性進(jìn)行仿真,但卻很難實(shí)現(xiàn)對(duì) PCB 與連接器阻抗等實(shí)際系統(tǒng)級(jí)特性進(jìn)行精確建模,尤其是使用較低成本的仿真工具。因此必須進(jìn)行實(shí)際穩(wěn)定性測(cè)量,才能了解環(huán)路的實(shí)際穩(wěn)定性。

誠(chéng)然,我已經(jīng)了解了系統(tǒng)投入生產(chǎn)的許多情況,其在生產(chǎn)后期因環(huán)境變化和/或工作極限條件而變得不穩(wěn)定。在這些情況下,原型設(shè)計(jì)可能運(yùn)行良好,但電源內(nèi)的相位和增益裕度卻沒在原型測(cè)試中得到測(cè)試。如果設(shè)計(jì)人員能夠?qū)﹄娫吹姆€(wěn)定性進(jìn)行測(cè)試,就可在其造成更大生產(chǎn)成本問題之前找到并糾正該問題。