基于FPGA的超聲波氣體流量計中AGC的實現(xiàn)

河北工業(yè)大學(xué) 劉艷萍 楊玉芝 崔朋朋

摘要: 對于多聲路超聲波流量計,發(fā)射和接收電路是公用的,通過傳感器切換電路測量轉(zhuǎn)換各個聲路順流和逆流傳播時間,但由于各個聲路的長度不同,傳感器的特性存在差異,每次測量的接收信號大小也不同,并且強度也不穩(wěn)定。因此,要實現(xiàn)超聲波信號的精確測量,必須根據(jù)接收信號的強度自動調(diào)節(jié)接收電路增益,而且要單獨控制每個方向上的增益。為實現(xiàn)高精度的測量,在信號到達(dá)檢測電路之前必須使信號穩(wěn)定可靠。為此,信號處理要采用自動增益控制放大器。

Abstract:

Key words :

1 引言

超聲波流量計是一種新興的工業(yè)產(chǎn)品,具有無阻擋體,無可動件,無壓損,無示值漂移,適用于大口徑管道測量,測量精確度高,重復(fù)性強,量程比寬,可承受工作壓力高,可測多相流,不受氣體溫度、壓力、組成等變化的影響、易于實現(xiàn)數(shù)字通信等優(yōu)點。為減小甚至避免流速分布對流量計精度帶來的影響,超聲波流量計采用多聲道超聲波的測量方式。

對于多聲路超聲波流量計,發(fā)射和接收電路是公用的,通過傳感器切換電路測量轉(zhuǎn)換各個聲路順流和逆流傳播時間,但由于各個聲路的長度不同,傳感器的特性存在差異,每次測量的接收信號大小也不同,并且強度也不穩(wěn)定。因此,要實現(xiàn)超聲波信號的精確測量,必須根據(jù)接收信號的強度自動調(diào)節(jié)接收電路增益,而且要單獨控制每個方向上的增益。為實現(xiàn)高精度的測量,在信號到達(dá)檢測電路之前必須使信號穩(wěn)定可靠。為此,信號處理要采用自動增益控制放大器。

2 自動增益控制AGC

自動增益控制AGC(Automatic Gain Control)是一種在輸入信號幅度變化很大的情況下,使輸出信號幅度保持恒定或僅在較小的范圍內(nèi)變化的自動增益控制環(huán)路,即當(dāng)輸入信號很弱時,自動增益控制電路的增益較大,自動增益控制電路不起作用;當(dāng)輸入信號很強時,自動增益控制電路進(jìn)行控制使增益減小。這樣,當(dāng)輸入信號強度變化時,輸出端的信號電壓或功率基本不變或保持恒定。

信號傳輸過程中,隨著傳輸距離的變化及其他因素的影響,信號在空間傳播過程中存在明顯衰落,在接收機輸入端的信號強度有很大變化。因此在接收機前端必須加一個幅度控制系統(tǒng),自動增益控制環(huán)路是信號傳輸中必不可少的。

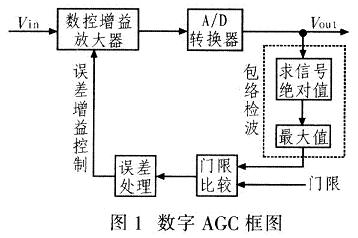

數(shù)字AGC精度高、適應(yīng)性好、體積小、可靠性高,因此受到廣大設(shè)計人員的關(guān)注。圖1為數(shù)字AGC框圖。

3 數(shù)字AGC的設(shè)計

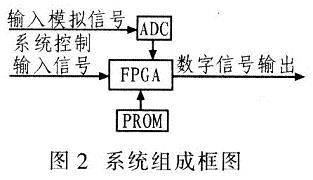

數(shù)字AGC系統(tǒng)組成包括A/D轉(zhuǎn)換器(ADC)、現(xiàn)場可編程門陣列(FPGA)、可編程只讀存儲器(PROM),如圖2所示。

3.1 FPGA選型簡介

該設(shè)計采用Altera公司的ACEX系列FPGA器件EPlK30TCl44-3作為核心控制器,其特點是:高密集型;適合大容量應(yīng)用的低成本可編程結(jié)構(gòu);多電平標(biāo)準(zhǔn)系統(tǒng),其I/O接口可驅(qū)動2.5 V和3.3 v器件或被5 V器件驅(qū)動;靈活的內(nèi)部連接;強大的I/0接口.對于每個I/0接口有獨立的三態(tài)輸出控制使能,對于每個I/O接口都有開漏輸出選擇。

EPIK30TCl44-3型FPGA滿足該系統(tǒng)設(shè)計要求,30 000個邏輯門適合于數(shù)字系統(tǒng)設(shè)計所需的邏輯門數(shù)量;多電平標(biāo)準(zhǔn)簡化了FPGA與外部電路的接口;102個功能強大的I/0接口方便了FPGA外嗣電路設(shè)計;JATG邊界掃描功能為系統(tǒng)開發(fā)與完善提供了很大的方便。

3.2 FPGA內(nèi)部設(shè)計

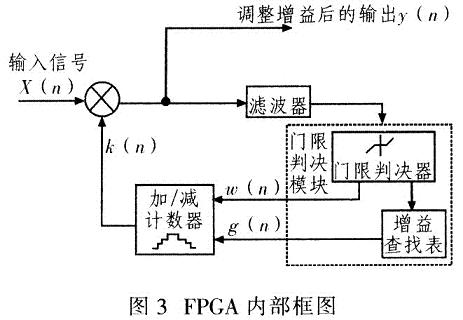

該設(shè)計主要由乘法器、門限判決、寄存器、加/減計數(shù)器4個模塊組成,實現(xiàn)40 dB動態(tài)范圍的控制。FPGA內(nèi)部框圖如圖3所示。

經(jīng)A/D采樣后的信號x(n)進(jìn)入FPGA進(jìn)行處理。x(n)首先進(jìn)入乘法器模塊與可控增益因子k(n)相乘,然后分成兩路。一路作為調(diào)整增益后的AGC輸出y(n);另一路送入門限判決模塊。門限判別模塊包括門限判決器和增益查找表,門限判決器內(nèi)設(shè)有高低2個門限,當(dāng)輸入包絡(luò)信號電平大于高門限時,則認(rèn)為輸入信號過大,應(yīng)調(diào)整增益控制因子k(n)減小:當(dāng)輸入包絡(luò)信號電平小于低門限時,則認(rèn)為輸入信號過小,應(yīng)調(diào)整增益控制因子k(n)增加。對于增加或減少的步進(jìn)量g(n)則從增益查找表中得到。加/減計數(shù)器模塊根據(jù)查找表得到的步進(jìn)因子g(n)及門限判決模塊提供的計數(shù)方向w(n)來調(diào)整增益控制因子的。

3.2.1 門限判決模塊

門限判決模塊用于限制加/減計數(shù)器控制號的波動,防止環(huán)路振蕩,其內(nèi)設(shè)高低2個門之間的范圍即為AGC輸出信號的波動范圍。防止AGC發(fā)生振蕩,該范圍應(yīng)該在滿足解調(diào)器要求的動態(tài)范圍條件下足夠?qū)挘皇呛愣ú蛔兊碾娖街怠H绻笥诟唛T限,則認(rèn)為信號過大,首先送給加/減計數(shù)器一個向下計數(shù)的信號,然后根據(jù)信號的范同從查找表中確定加/減計數(shù)器的步進(jìn)量;如果小于低門限,則認(rèn)為信號過小,首先送給加/減計數(shù)器一個向上計數(shù)的信號,然后根據(jù)信號的范圍從查找表中確定加/減計數(shù)器的步進(jìn)量;如果在兩門限之間,則加/減計數(shù)器的步進(jìn)量為零。

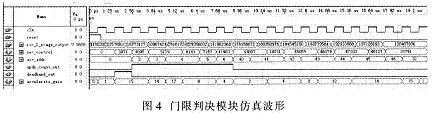

圖4是門限判決模塊的仿真波形。其中,clk為時鐘信號,reset為復(fù)位信號,iir_2_stage_output為濾波器的輸出信號,set_control為與門限進(jìn)行比較的信號,acc_addr為查找表地址,updn_count_out為控制加/減計數(shù)器的計數(shù)方向,dead_band_out為控制加/減計數(shù)器的計數(shù)控制信號,accelerate_gain為控制加/減計數(shù)器的計數(shù)步進(jìn)量。

從圖4中可以看出,當(dāng)信號小于低門限7500時,dead_band_out=‘0’,updn_count_out=‘1’,控制加/減計數(shù)器向上計數(shù),set_control遠(yuǎn)離低門限,計數(shù)步進(jìn)量增大;當(dāng)信號大于高門限10 500時,deadband_out=‘0’,updn_count_out=‘0’,控制加/減計數(shù)器向下計數(shù),set_control遠(yuǎn)離高門限,計數(shù)步進(jìn)量增大。

3.2.2 加/減計數(shù)器模塊

加/減計數(shù)器模塊根據(jù)輸入信號與最佳的接收信號之間的差值,對輸入信號進(jìn)行反向補償。假設(shè)輸入信號經(jīng)過一定衰減,AGC環(huán)路經(jīng)過比較可確定接收信號電平低于最佳電平。這個差值將導(dǎo)致計數(shù)器向上計數(shù),增加環(huán)路增益,直到環(huán)路濾波器的輸出重新回到門限判決模塊的兩個門限之間。如果信號乘以增益后、環(huán)路濾波器的輸出信號大于門限判決模塊的高門限時,計數(shù)器向下計數(shù),降低環(huán)路增益,直到信號重新回到可以準(zhǔn)確解調(diào)所需的接收信號范圍。

圖5是加/減計數(shù)器模塊的仿真波形。gain_counter_out為截位前的增益值,gain_control_out為截位后實際輸出的增益值。從圖5看出,當(dāng)reset=‘1’時,計數(shù)器復(fù)位,設(shè)增益初始值gain_control_out=‘32’。而當(dāng)deadband_in=‘O’,updn_count_in=‘1’,加/減計數(shù)器按步進(jìn)量accelerate_gain_in向上計數(shù);而當(dāng)deadband_in=‘O’,updn_count_in=‘0’,加/減計數(shù)器按步進(jìn)量accelerate_gainjn向下計數(shù)。計數(shù)所得的值即為輸出的增益控制因子。

4 結(jié)論

本文實現(xiàn)了一種全數(shù)字AGC的設(shè)計方案。此方案可實現(xiàn)40 dB動態(tài)范圍的控制,并且具有控制精度高,調(diào)節(jié)速度快,調(diào)試簡單,受環(huán)境影響小,穩(wěn)定性和可靠性高等優(yōu)點。隨著集成器件的發(fā)展,有望實現(xiàn)高動態(tài)范圍的全數(shù)字AGC,以便應(yīng)用到更廣闊的領(lǐng)域中。

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。