概覽

多功能智能DAQ設(shè)備配有自定義式板載處理功能,最大限度地為系統(tǒng)定時(shí)及觸發(fā)提供靈活性能。 與控制設(shè)備功能的固定ASIC不同,智能DAQ采用基于FPGA的系統(tǒng)定時(shí)控制器,令所有模擬和數(shù)字I/O能夠根據(jù)特定應(yīng)用操作接受相應(yīng)的配置。 本指南展示了:如何使用R系列智能DAQ板卡和NI LabVIEW FPGA,靈活自如地執(zhí)行數(shù)據(jù)采集任務(wù)

入門(mén)

NI LabVIEW FPGA模塊幫助DAQ系統(tǒng)的開(kāi)發(fā)者靈活自如地進(jìn)行應(yīng)用程序編程以實(shí)現(xiàn)各類(lèi)輸入/輸出操作。 用戶(hù)無(wú)需預(yù)先了解VHDL等硬件設(shè)計(jì)工具,便可將LabVIEW代碼嵌入FPGA芯片并獲得硬件定時(shí)的速度和可靠性。

讓我們先從數(shù)據(jù)采集硬件的常用組件切入論題。 假設(shè)您擁有了模數(shù)轉(zhuǎn)換器(ADC)、數(shù)模轉(zhuǎn)換器(DAC)和數(shù)字輸入/輸出線(xiàn),則所有I/O便要根據(jù)實(shí)際操作接受某種方式的定時(shí)和控制。 典型的多功能數(shù)據(jù)采集設(shè)備采用功能齊全的ASIC,滿(mǎn)足了大多數(shù)的功能性需求。

比如:M系列DAQ設(shè)備通過(guò)DAQ-STC2,控制著各類(lèi)硬件組件的定時(shí)和觸發(fā)。 智能DAQ硬件(如:R系列DAQ設(shè)備)區(qū)別于市面上的其他任何數(shù)據(jù)采集設(shè)備,因?yàn)樵诳刂圃O(shè)備功能方面智能DAQ用基于FPGA的系統(tǒng)定時(shí)控制器取代了傳統(tǒng)ASIC,從而使得所有模擬和數(shù)字I/O都能根據(jù)特定應(yīng)用操作接受相應(yīng)的配置。 可重配置FPGA芯片通過(guò)NI LabVIEW FPGA模塊進(jìn)行編程,此時(shí)NI LabVIEW的數(shù)據(jù)流模式仍舊適用,不過(guò)采用了一組新函數(shù)控制最底層的設(shè)備I/O。

LabVIEW FPGA I/O節(jié)點(diǎn)并不通過(guò)NI-DAQmx函數(shù)負(fù)責(zé)實(shí)現(xiàn)常見(jiàn)的任務(wù)和功能,而是靈活自如地在各個(gè)通道最底層上運(yùn)行。 通過(guò)以下各部分的內(nèi)容,我們將了解NI-DAQmx的特定實(shí)例,并學(xué)習(xí)如何通過(guò)智能DAQ定制各類(lèi)數(shù)據(jù)采集任務(wù)。

定時(shí)和觸發(fā)

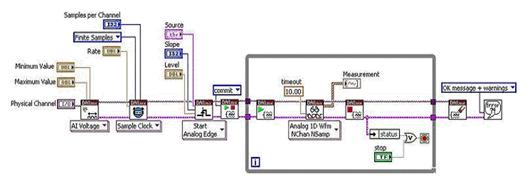

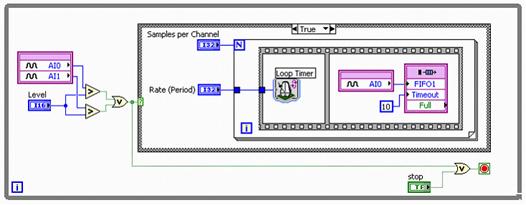

實(shí)現(xiàn)高級(jí)數(shù)據(jù)采集的智能DAQ主要用于定制定時(shí)和觸發(fā)。 下方的范例程序框圖展現(xiàn)了:NI-DAQmx幫助實(shí)現(xiàn)的觸發(fā)式模擬輸入任務(wù)。

圖1. 通過(guò)NI-DAQmx實(shí)現(xiàn)的觸發(fā)式模擬輸入

如圖1所示,智能DAQ并未使用不同函數(shù)配置通道,而是通過(guò)名為I/O節(jié)點(diǎn)的函數(shù)讀寫(xiě)各路模擬和數(shù)字通道。 讓我們看看使用NI LabVIEW FPGA中I/O節(jié)點(diǎn)所獲得的相同功能。

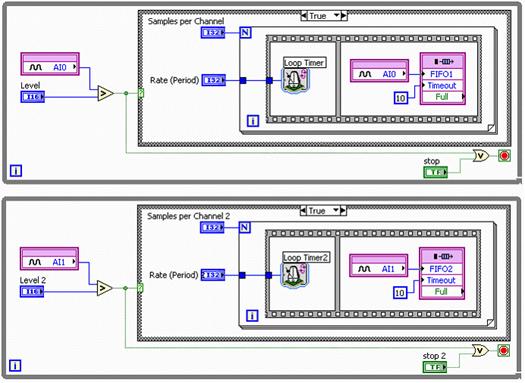

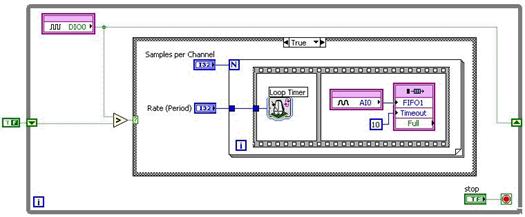

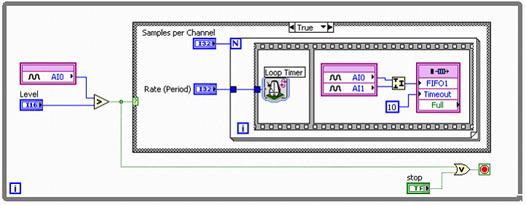

圖2. 通過(guò)智能DAQ和NI LabVIEW FPGA實(shí)現(xiàn)的觸發(fā)式模擬輸入

上圖既沒(méi)有針對(duì)全局通道、采樣時(shí)鐘、觸發(fā)的配置函數(shù),也沒(méi)有開(kāi)始、停止和清除等任務(wù)。 所有內(nèi)容都被1個(gè)簡(jiǎn)單的模擬I/O讀取所取代;全部定時(shí)都為本地LabVIEW結(jié)構(gòu)(如:While循環(huán)和條件結(jié)構(gòu))所控制。由于整個(gè)程序框圖均在FPGA硬件內(nèi)執(zhí)行,LabVIEW代碼的運(yùn)行便體現(xiàn)出硬件定時(shí)的速度和可靠性。

讓我們更深入地了解一下該程序框圖的運(yùn)行方式。 模擬I/O節(jié)點(diǎn)并不指定某個(gè)采樣速率,而使用For循環(huán)采集各個(gè)樣本。 與之對(duì)應(yīng)的ADC在I/O節(jié)點(diǎn)被調(diào)用時(shí),負(fù)責(zé)對(duì)輸入信號(hào)進(jìn)行實(shí)際數(shù)字化,因而通過(guò)For循環(huán)接受定時(shí)。 若想在100 kHz的頻率下進(jìn)行信號(hào)采樣,針對(duì)循環(huán)的延遲就必須設(shè)定為10 µs。 循環(huán)的定時(shí)器函數(shù)從第2輪循環(huán)迭代開(kāi)始便確保著特定的時(shí)間延遲,用戶(hù)因而能夠通過(guò)順序結(jié)構(gòu)保證樣本之間存在著指定的時(shí)間間隔。 NI LabVIEW FPGA中功能強(qiáng)大的條件結(jié)構(gòu),實(shí)際代表了用于封裝各類(lèi)代碼的硬件觸發(fā)。 由于所有的函數(shù)和結(jié)構(gòu)都通過(guò)邏輯單元在硬件內(nèi)運(yùn)行,所以條件結(jié)構(gòu)確保開(kāi)始具有實(shí)時(shí)10 µs時(shí)間精度的采樣。 最后需指出的是,由于操作位于硬件層,只涉及幾個(gè)層次的抽象處理,因此用戶(hù)無(wú)需清除任務(wù)ID或釋放內(nèi)存。

就基于FPGA的智能DAQ硬件而言,其真正的優(yōu)勢(shì)是能夠定制各類(lèi)定時(shí)和觸發(fā),并在硬件中進(jìn)行信號(hào)處理和決策。 現(xiàn)在讓我們了解一下:針對(duì)某類(lèi)自定義應(yīng)用,需對(duì)模擬輸入觸發(fā)做出哪些修改。 若我們希望在2路模擬輸入通道的某路電壓超過(guò)指定范圍時(shí)便觸發(fā)采集,又該如何修改呢? 借助NI LabVIEW FPGA,此類(lèi)任務(wù)的執(zhí)行易如反掌。

圖 3. 通過(guò)智能DAQ和NI LabVIEW FPGA實(shí)現(xiàn)的自定義觸發(fā)式模擬輸入

這里,我們已經(jīng)為程序框圖添加了第2個(gè)I/O節(jié)點(diǎn)和第2個(gè)比較函數(shù),以及1個(gè)布爾“或”函數(shù)。 智能DAQ硬件為所有的模擬輸入通道提供專(zhuān)用ADC,因而2路通道能夠接受同步采樣;同時(shí),只要任何1路通道的電壓超過(guò)了指定范圍,條件結(jié)構(gòu)便會(huì)執(zhí)行“真”條件,并開(kāi)始以10 µs時(shí)間精度進(jìn)行采樣。 請(qǐng)記住:缺少智能DAQ便不可能生成類(lèi)似的觸發(fā);在其他DAQ硬件上應(yīng)用時(shí),觸發(fā)需要具有更高延遲的軟件定時(shí)來(lái)實(shí)現(xiàn)。 如果此后我們希望通過(guò)擴(kuò)展將監(jiān)控范圍從2路通道延伸至全部8路通道,甚至希望添加數(shù)字觸發(fā),就需要簡(jiǎn)化自定義代碼。 添加預(yù)觸發(fā)掃描后,用戶(hù)便可對(duì)輸入通道不斷進(jìn)行采樣并將數(shù)據(jù)傳送至FIFO緩沖器。 觸發(fā)器一旦接受讀取,F(xiàn)IFO緩沖器和此后的采樣便可經(jīng)由DMA通道,被傳送至主機(jī)。

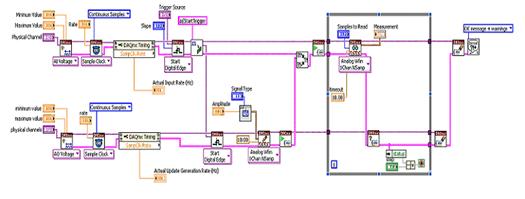

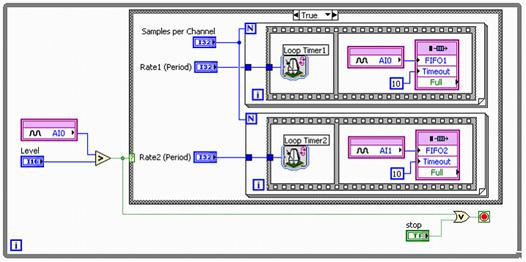

如果我們希望借助NI-DAQmx驅(qū)動(dòng),對(duì)第2模擬輸入通道進(jìn)行采樣,則該程序框圖與圖1所示的內(nèi)容相差無(wú)幾。然而限制依然存在,因?yàn)?路通道均被迫引用相同的觸發(fā)器并以相同的時(shí)鐘頻率進(jìn)行采樣。 現(xiàn)在我們來(lái)看看:智能DAQ和NI LabVIEW FPGA幫助實(shí)現(xiàn)的各類(lèi)多通道采樣。

圖4. 通過(guò)智能DAQ實(shí)現(xiàn)的觸發(fā)式同步模擬輸入

圖4(上圖)展現(xiàn)了:如何基于模擬輸入通道0中的模擬觸發(fā)器,對(duì)2路不同的模擬輸入通道進(jìn)行同步采樣。由于智能DAQ設(shè)備均配有獨(dú)立的ADC,在同一I/O節(jié)點(diǎn)中的2路通道可在完全相同的時(shí)刻接受采樣。 典型的多功能DAQ設(shè)備可通過(guò)一個(gè)ADC多路復(fù)用所有通道,因此,各路通道必須共享相同的采樣時(shí)鐘和觸發(fā)線(xiàn)。 圖5(下圖)展現(xiàn)了:智能DAQ硬件其實(shí)能夠以獨(dú)立的速率,對(duì)不同的模擬輸入通道進(jìn)行采樣。 在獨(dú)立回路中放置模擬輸入I/O節(jié)點(diǎn)后,每路通道會(huì)以完全不同的速率進(jìn)行采樣,然后各自通過(guò)2條DMA通道讀寫(xiě)硬盤(pán)。

圖5. 通過(guò)智能DAQ實(shí)現(xiàn)的觸發(fā)式多速率模擬輸入

最后需指出的是,我們?nèi)羰窍M?路通道具有相互獨(dú)立的采樣率和開(kāi)始觸發(fā),則可參照?qǐng)D6,將所有I/O節(jié)點(diǎn)都部署在并行循環(huán)結(jié)構(gòu)中。該方式充分利用了FPGA的并行性,確保了各項(xiàng)任務(wù)能夠使用專(zhuān)用資源并在執(zhí)行時(shí)完全獨(dú)立于其他采集任務(wù)。

圖6. 通過(guò)智能DAQ實(shí)現(xiàn)的獨(dú)立觸發(fā)式多速率模擬輸入

同步

DAQmx驅(qū)動(dòng)程序提供多種同步選擇,幫助建立輸入和輸出的時(shí)間相關(guān)性。 在下方的程序框圖中,模擬輸入通道和模擬輸出通道借助數(shù)字觸發(fā)實(shí)現(xiàn)同步;過(guò)程中,需對(duì)模擬輸入指定數(shù)字觸發(fā),并使用模擬輸入的觸發(fā)器信號(hào)觸發(fā)產(chǎn)生模擬輸出。

圖7. 通過(guò)NI-DAQmx實(shí)現(xiàn)的同步模擬輸入和輸出

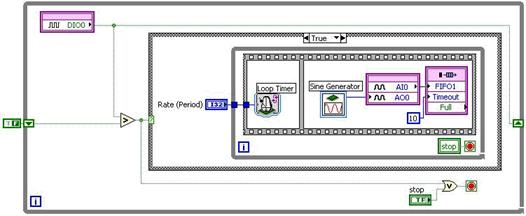

用戶(hù)可通過(guò)智能DAQ硬件輕而易舉地執(zhí)行同步任務(wù),而無(wú)需借助任務(wù)ID和板載信號(hào)路由。 本處即顯示了NI LabVIEW FPGA中的內(nèi)容。

圖8. 通過(guò)智能DAQ實(shí)現(xiàn)的同步模擬輸入和輸出

此處,我們?cè)俅瓮ㄟ^(guò)條件結(jié)構(gòu)在FPGA芯片上執(zhí)行硬件觸發(fā),而數(shù)字通道0上的上升沿則啟用了真條件中的代碼。 在順序結(jié)構(gòu)中,模擬輸入與輸出的節(jié)點(diǎn)在同時(shí)接受調(diào)用的過(guò)程中,幾乎沒(méi)有任何抖動(dòng);而我們只要簡(jiǎn)單地在各個(gè)獨(dú)立的While循環(huán)內(nèi)嵌入模擬I/O節(jié)點(diǎn),即可令其擁有獨(dú)立的采樣速率。 另外值得注意的是: 程序框圖中顯示的正弦發(fā)生器函數(shù)是1個(gè)Express VI,可幫助用戶(hù)在查找表(LUT)中交互式地配置正弦值。

圖8中的智能DAQ程序框圖與圖7中的DAQmx VI皆具有相同的功能,而唯有智能DAQ才能為自定義任務(wù)提供相應(yīng)的靈活性。 舉例為證:如需添加1個(gè)暫停觸發(fā),我們只消在內(nèi)部While循環(huán)中添加1個(gè)條件結(jié)構(gòu),并通過(guò)另一個(gè)數(shù)字I/O節(jié)點(diǎn)選擇真條件或假條件,即可輕松完成任務(wù)。 對(duì)硬件進(jìn)行編程的強(qiáng)大功能,實(shí)現(xiàn)了各類(lèi)I/O的定時(shí)與同步。

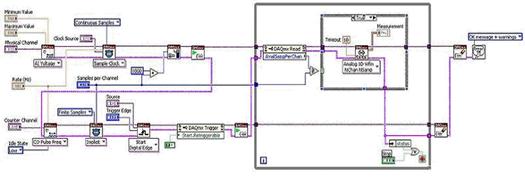

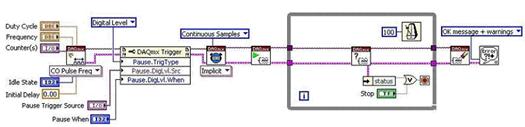

多功能同步的另一例證體現(xiàn)為:通過(guò)板載計(jì)數(shù)器產(chǎn)生有限脈沖并將計(jì)數(shù)器輸出用作模擬輸入的采樣時(shí)鐘。 該過(guò)程是進(jìn)行可重觸發(fā)式有限采樣的常用手段。 下圖顯示了開(kāi)展此類(lèi)采集所必需的DAQmx代碼。

圖9. 通過(guò)NI-DAQmx實(shí)現(xiàn)的可重觸發(fā)式有限模擬輸入

現(xiàn)在,讓我們對(duì)下圖內(nèi)容和呈現(xiàn)相同功能的NI LabVIEW FPGA程序框圖,加以比較。

圖10. 通過(guò)智能DAQ和NI LabVIEW FPGA實(shí)現(xiàn)的可重觸發(fā)式有限模擬輸入

由于NI LabVIEW代碼在硬件層運(yùn)行,圖10中的驅(qū)動(dòng)配置步驟顯然得到了極大精減。 我們已經(jīng)借助簡(jiǎn)單的數(shù)字輸入線(xiàn)和For循環(huán)結(jié)構(gòu),創(chuàng)建了硬件可重觸發(fā)式有限采集。 圖9中的程序框圖使用2個(gè)板載計(jì)數(shù)器,創(chuàng)建出可重觸發(fā)的有限脈沖序列;典型的多功能DAQ設(shè)備只有2個(gè)計(jì)數(shù)器。 而借助NI LabVIEW FPGA,智能DAQ硬件卻能夠?qū)⑷我庖粭l數(shù)字線(xiàn)配置成計(jì)數(shù)器。 我們將在之后的段落里,涉及更多“通過(guò)智能DAQ運(yùn)行計(jì)數(shù)器/定時(shí)器”的內(nèi)容。

我們能夠借助由頻率觸發(fā)的采集,進(jìn)一步地推進(jìn)智能DAQ在硬件定時(shí)方面的靈活性特性。 用戶(hù)可通過(guò)高速板載決策計(jì)算輸入信號(hào)的頻率,而后選擇條件結(jié)構(gòu)中所需的代碼;這一點(diǎn)是使用典型多功能DAQ設(shè)備所無(wú)法企及的。 在多設(shè)備的同步進(jìn)程中,智能DAQ還可提供用于PCI板卡的RTSI總線(xiàn)或是用于PXI模塊的PXI觸發(fā)總線(xiàn)。 這些外部定時(shí)和同步線(xiàn)還可通過(guò)程序框圖上的I/O節(jié)點(diǎn)接受訪(fǎng)問(wèn)。

模擬波形的生成

不少多功能DAQ設(shè)備都配有模擬輸出通道,能夠?yàn)榱松蛇B續(xù)的模擬波形而需要用到FIFO緩沖。 生成的波形可將FIFO用作循環(huán)緩沖區(qū),且無(wú)需從主機(jī)處接受任何更新數(shù)據(jù),即可連續(xù)不斷地重新生成一系列的模擬值。 通信總線(xiàn)的有無(wú)對(duì)此影響不大,因?yàn)椴](méi)有針對(duì)設(shè)備的頻繁數(shù)據(jù)讀寫(xiě)。 而如果波形需要修改,就必須重新啟動(dòng)輸出任務(wù)并向FIFO寫(xiě)入新數(shù)據(jù)。 另一個(gè)辦法是向硬件FIFO設(shè)備連續(xù)讀寫(xiě)數(shù)據(jù),而這又會(huì)導(dǎo)致輸出任務(wù)出現(xiàn)時(shí)滯。 借助智能DAQ,用戶(hù)能夠?qū)⒉ㄐ屋敵鼋Y(jié)果存儲(chǔ)于硬件,甚至能夠通過(guò)硬件觸發(fā)改變波形,進(jìn)而創(chuàng)建任意波形發(fā)生器。

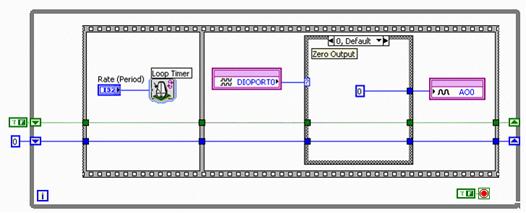

下方的函數(shù)發(fā)生器范例通過(guò)數(shù)字輸入線(xiàn),觸發(fā)了輸出波形中的改動(dòng)。 通過(guò)組合數(shù)字I/O線(xiàn)0與1,我們?nèi)〉昧藨?yīng)用于模擬輸出的4種不同狀態(tài)或稱(chēng)條件。

圖11a. 配有智能DAQ條件0的函數(shù)發(fā)生器 – 零輸出

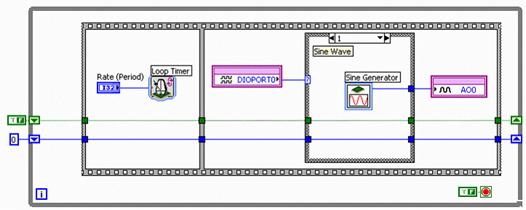

圖11b. 配有智能DAQ條件1的函數(shù)發(fā)生器 – 正弦波

當(dāng)兩線(xiàn)皆呈現(xiàn)低電平時(shí),執(zhí)行條件0;如圖11a所示,輸出值為0 V常量。而當(dāng)DIO線(xiàn)0呈現(xiàn)高電平而DIO線(xiàn)1呈現(xiàn)低電平時(shí),條件1將在模擬輸出0上執(zhí)行并生成一個(gè)正弦波。用戶(hù)可通過(guò)該正弦生成結(jié)構(gòu)(圖11b)中的正弦發(fā)生器Express VI,配置NI LabVIEW FPGA必需的參數(shù),交互地配置正弦波。

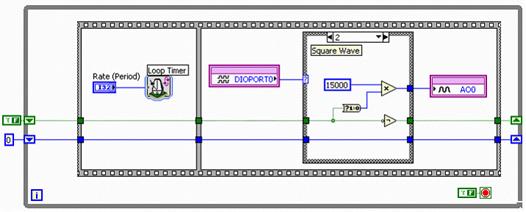

圖11c. 配有智能DAQ條件2的函數(shù)發(fā)生器 – 方波

條件2(圖11c)能夠在While循環(huán)的每輪迭代中,輕松切換布爾值。 數(shù)值較低時(shí),整數(shù)15000便被寫(xiě)入模擬輸出AO0,以對(duì)應(yīng)16位DAC內(nèi)由輸出寄存器存放的數(shù)值:15000。 16位有符號(hào)整數(shù)可以包含-32768到32767之間的數(shù)值。當(dāng)輸出電壓范圍介于-10 V和10 V時(shí),向模擬輸出AO0寫(xiě)入-32768會(huì)生成-10 V電壓,而寫(xiě)入32767則生成10 V電壓。該例中,因我們的寫(xiě)入值為15000,則生成的電壓將低于5 V。(數(shù)學(xué)公式為: 15000/32767 * 10 V = 4.5778 V) 通常,條件2會(huì)輸出一個(gè)在0 V和4.578 V之間變換的方波。

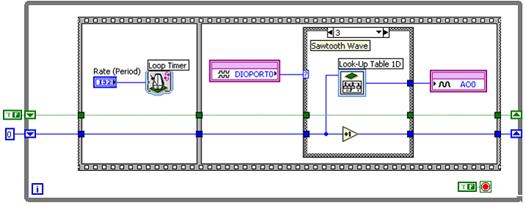

圖11d. 配有智能DAQ條件3的函數(shù)發(fā)生器 – 鋸齒波

當(dāng)DIO 0和DIO 1均呈現(xiàn)高電平時(shí),便執(zhí)行最后一個(gè)條件(圖11d);其間,須借助查找表(LUT)連續(xù)生成一個(gè)鋸齒波。 作為另一類(lèi)Express VI的查表VI,既能存儲(chǔ)任意波形值,也能通過(guò)編程建立波形值的索引。 該例中,接受配置的鋸齒波可在模擬輸出通道0上生成。

通過(guò)將所有的值都存儲(chǔ)在FPGA上,用戶(hù)在降低總線(xiàn)依賴(lài)性的同時(shí),也確保了波形更新時(shí)硬件定時(shí)的速度和可靠性。 之前各部分中所描述的模擬輸入的觸發(fā)和同步靈活性同樣適用于模擬輸出;借助智能DAQ,用戶(hù)能夠以不同速率,完全獨(dú)立地更新各路模擬輸出通道。 這意味著:用戶(hù)可在不影響其他通道輸出結(jié)果的前提下,修改單個(gè)周期性波形的頻率。 請(qǐng)注意:大多數(shù)數(shù)據(jù)采集硬件均不具備此項(xiàng)功能。

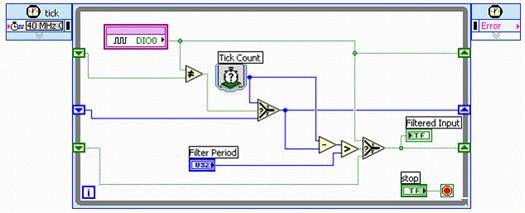

計(jì)數(shù)器/定時(shí)器的操作

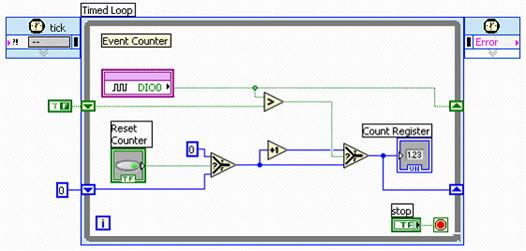

如前所述,典型的多功能DAQ設(shè)備只有2個(gè)板載計(jì)數(shù)器,而智能DAQ則能在各條數(shù)字線(xiàn)上運(yùn)行計(jì)數(shù)器功能。 數(shù)字I/O節(jié)點(diǎn)能夠在NI LabVIEW FPGA中利用名為單周期定時(shí)循環(huán)的專(zhuān)業(yè)結(jié)構(gòu),幫助用戶(hù)在2.5 MHz至200 MHz的特定頻率范圍內(nèi)執(zhí)行代碼。 例如,借助40 MHz的時(shí)鐘,用戶(hù)可使用單周期定時(shí)循環(huán),在各條數(shù)字線(xiàn)上創(chuàng)建40 MHz計(jì)數(shù)器。 圖12(下圖)展現(xiàn)了程序框圖的樣式。

圖12. 配有智能DAQ的簡(jiǎn)單事件計(jì)數(shù)器

由于計(jì)算值基于U32(32位整數(shù))的數(shù)據(jù)類(lèi)型被發(fā)送至顯示控件,該代碼便在FPGA芯片上生成了1個(gè)40 MHz的32位計(jì)數(shù)器。 用戶(hù)可對(duì)其進(jìn)行數(shù)次復(fù)制與粘貼,令不同數(shù)字線(xiàn)上的多個(gè)計(jì)數(shù)器都能夠彼此完全并行地運(yùn)行。 通過(guò)對(duì)智能DAQ中參數(shù)的設(shè)置可以實(shí)現(xiàn)定時(shí)器操作的自定義。 通過(guò)選擇,用戶(hù)能夠每隔2個(gè)上升沿便進(jìn)行1次計(jì)數(shù)器遞增,甚至能基于計(jì)數(shù)寄存器的值觸發(fā)模擬采集。 許多復(fù)雜的計(jì)數(shù)器操作(如:有限脈沖序列生成和級(jí)聯(lián)式事件計(jì)數(shù))均需要使用2個(gè)計(jì)數(shù)器,這意味著使用典型多功能設(shè)備中的所有板載計(jì)數(shù)器。 在總共160條數(shù)字線(xiàn)的幫助下,智能DAQ硬件上定時(shí)器的最大數(shù)量很少受到I/O可用性的影響,而往往取決于FPGA芯片的大小。 由于NI LabVIEW代碼運(yùn)行于硅芯片中,因而用戶(hù)無(wú)需“裝備”或“重新裝備”通用計(jì)數(shù)器,即能全面控制計(jì)數(shù)器的運(yùn)行。

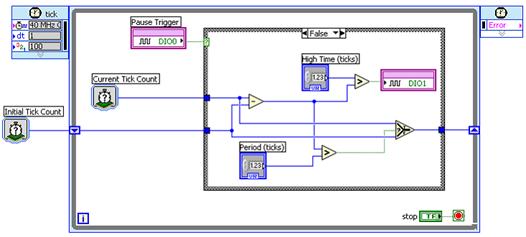

圖13(下圖)中的范例使用計(jì)數(shù)器,生成了一個(gè)連續(xù)脈沖序列并將暫停觸發(fā)器置于NI-DAQmx中。

圖13. 連續(xù)脈沖序列的生成和配有NI-DAQmx的暫停觸發(fā)器

在NI LabVIEW FPGA中,暫停觸發(fā)器無(wú)需接受配置,因?yàn)橹恍韬?jiǎn)單的條件結(jié)構(gòu)便能在硅芯片中實(shí)現(xiàn)相同的功能。 此處是通過(guò)智能DAQ運(yùn)行時(shí)所展現(xiàn)的相同功能(圖14)。

圖14. 連續(xù)脈沖序列的生成和配有智能DAQ的暫停觸發(fā)器

在這種情況下,數(shù)字I/O線(xiàn)DIO0用作暫停觸發(fā),而脈沖將在數(shù)字I/O線(xiàn)DIO1上生成并輸出。使用單周期定時(shí)循環(huán)可令各個(gè)脈沖獲得25 ns的分辨率,因?yàn)檫@將成為單個(gè)計(jì)時(shí)在使用40 MHz定時(shí)源時(shí)的值。

數(shù)字I/O應(yīng)用

智能DAQ硬件提供多達(dá)160條硬件定時(shí)數(shù)字線(xiàn),令諸多數(shù)字應(yīng)用成為可能。 我們已經(jīng)學(xué)習(xí)了如何使用數(shù)字I/O實(shí)現(xiàn)觸發(fā)、同步及計(jì)數(shù)器/定時(shí)器的運(yùn)行,而智能DAQ還可用于誤碼率測(cè)試、數(shù)字模式匹配、脈沖寬度調(diào)制、正交編碼器和數(shù)字通信協(xié)議。 自定義或標(biāo)準(zhǔn)形式的串行接口均能直接通過(guò)數(shù)字定時(shí)框圖編程來(lái)實(shí)現(xiàn)。 舉例說(shuō)明,SPI便是一款與硬件組件(如:微控制器或ADC)進(jìn)行通信時(shí)最常用的串口協(xié)議。 圖15(下圖)展現(xiàn)了在進(jìn)行16位SPI通信時(shí),3條必要數(shù)字線(xiàn)所對(duì)應(yīng)的定時(shí)框圖。

圖15. SPI通信輸入定時(shí)框圖

如定時(shí)框圖所示,所有16位數(shù)據(jù)均在每個(gè)時(shí)鐘周期上順次傳遞,而片選控制線(xiàn)(chip select line)則呈現(xiàn)低電平。 現(xiàn)在,我們來(lái)看看在NI LabVIEW FPGA中,如何通過(guò)智能DAQ硬件上的3條數(shù)字線(xiàn)進(jìn)行此類(lèi)編程。

圖16中,外部While循環(huán)確保了所有代碼均能連續(xù)執(zhí)行,而寫(xiě)入布爾輸入控件則通過(guò)條件結(jié)構(gòu)啟動(dòng)著數(shù)據(jù)傳遞。 順序結(jié)構(gòu)中的第一框架將片選控制線(xiàn)(chip select line)設(shè)置為低電平,之后由中間框架寫(xiě)入數(shù)據(jù)位并將時(shí)鐘線(xiàn)切換16次。 最終,第三順序框?qū)⑵x控制線(xiàn)(chip select line)設(shè)置回TRUE狀態(tài),并將數(shù)據(jù)線(xiàn)重置為默認(rèn)的FALSE狀態(tài)。 這一簡(jiǎn)單范例只是借助智能DAQ進(jìn)行數(shù)字通信時(shí)的一項(xiàng)內(nèi)容。 用戶(hù)若想應(yīng)用數(shù)字握手,便需為ACK(備用)和REQ(暫停)線(xiàn)準(zhǔn)備2路通道,其中一路通道面向并行運(yùn)作的時(shí)鐘信號(hào)和數(shù)據(jù)線(xiàn)。

數(shù)字線(xiàn)會(huì)時(shí)常抖動(dòng),在使用機(jī)電接觸時(shí)更是如此,然而用戶(hù)可通過(guò)NI LabVIEW FPGA,選擇不同方式,在數(shù)字輸入線(xiàn)上添加去抖動(dòng)濾波器。 在消除狀態(tài)的錯(cuò)誤改動(dòng)時(shí),數(shù)字去抖動(dòng)濾波器確保數(shù)值的變化能夠保持一段最短的時(shí)間,因而規(guī)避了因抖動(dòng)引發(fā)的錯(cuò)誤讀取。 圖17展現(xiàn)了如何通過(guò)智能DAQ實(shí)現(xiàn)此項(xiàng)功能的內(nèi)容。

圖17. 智能DAQ硬件上的數(shù)字濾波器程序框圖

數(shù)據(jù)傳輸方式

配備N(xiāo)I-DAQmx驅(qū)動(dòng)程序的傳統(tǒng)多功能DAQ和智能DAQ之間的最大差異在于:數(shù)據(jù)傳輸?shù)膱?zhí)行方式。 NI-DAQmx驅(qū)動(dòng)程序?qū)⒊袚?dān)由設(shè)備至主機(jī)的各項(xiàng)傳輸任務(wù),此項(xiàng)操作中NI LabVIWE FPGA會(huì)對(duì)基于FPGA的所有板載硬件進(jìn)行編程。 用戶(hù)可通過(guò)多種途徑緩沖設(shè)備上的板載數(shù)據(jù),并使用不同方式(如:DMA通道或中斷請(qǐng)求)傳輸數(shù)據(jù)。

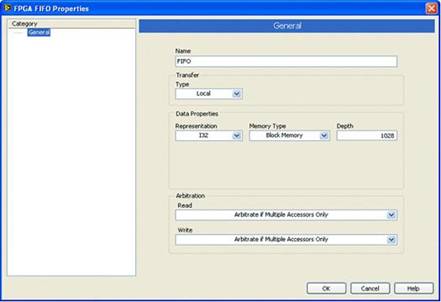

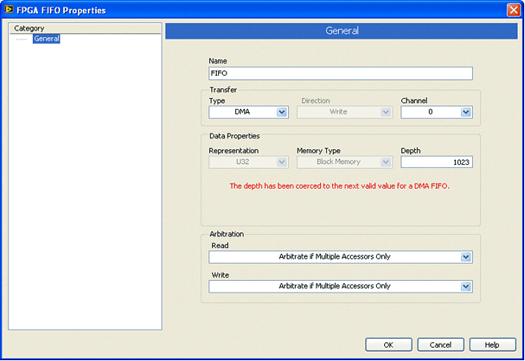

NI LabVIEW FPGA中的FIFO緩沖區(qū)在LabVIEW項(xiàng)目瀏覽器中接受配置,并能借助板載內(nèi)存或硬件邏輯獲得運(yùn)行。 圖18顯示了如何經(jīng)由項(xiàng)目瀏覽器,在板載塊存儲(chǔ)器中配置整數(shù)的FIFO緩沖區(qū)。

圖18. NI LabVIEW FPGA中的FIFO配置

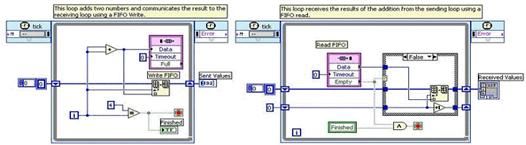

FIFO一經(jīng)創(chuàng)建,便能用于NI LabVIEW FPGA程序框圖上多個(gè)循環(huán)之間的數(shù)據(jù)傳遞。 圖19中的范例顯示:數(shù)據(jù)先被寫(xiě)入左側(cè)循環(huán)中的FIFO,并隨即從右側(cè)循環(huán)中的FIFO被讀出。

圖19. 通過(guò)FIFO和多循環(huán)實(shí)現(xiàn)的NI LabVIEW FPGA程序框圖

同樣通過(guò)LabVIEW FPGA FIFO獲得應(yīng)用的直接存儲(chǔ)器訪(fǎng)問(wèn)(DMA)通道,在項(xiàng)目瀏覽器中接受了類(lèi)似的配置。

圖20. NI LabVIEW FPGA中的DMA FIFO配置

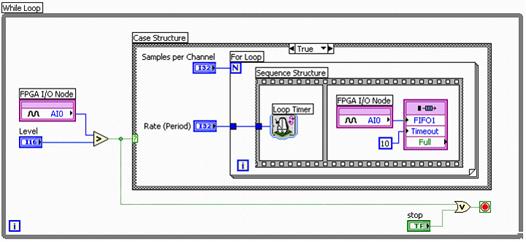

圖21. 通過(guò)DMA FIFO和位組裝實(shí)現(xiàn)的NI LabVIEW FPGA程序框圖

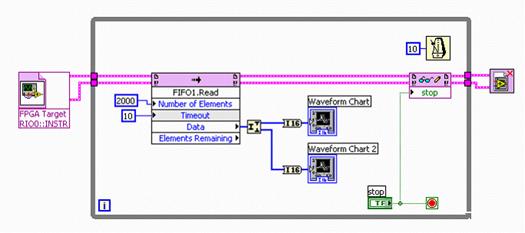

所有的DMA FIFO數(shù)據(jù)傳輸寬度均為32位;因此,當(dāng)其傳遞源自16位模擬輸入通道的數(shù)據(jù)時(shí),往往能夠合并2路通道或2個(gè)樣本上的數(shù)據(jù)再進(jìn)行傳輸,從而提高帶寬使用率。 這即是圖21所展現(xiàn)的位組裝。當(dāng)數(shù)據(jù)被直接傳遞到主控計(jì)算機(jī)的內(nèi)存后,便可通過(guò)在Windows環(huán)境下運(yùn)行的NI LabVIEW主接口函數(shù)接受讀取(圖22)。

圖22. 通過(guò)DMA FIFO讀取和位拆裝實(shí)現(xiàn)的主接口代碼

如圖22所示,主接口程序框圖引用FPGA終端VI,然后使用While循環(huán)連續(xù)讀取DMA FIFO。 32位的數(shù)據(jù)被分解為2路16位通道,在波形圖表上接受采樣和繪制。 主接口VI還能對(duì)FPGA VI前面板上的各類(lèi)顯示控件和輸入控件進(jìn)行讀寫(xiě)操作;在這種情況下,“停止按鈕”輸入控件也被寫(xiě)入。

結(jié)論

盡管DAQ-STC2等固定ASIC能夠滿(mǎn)足數(shù)據(jù)采集的大多數(shù)需求,然而,唯有借助智能DAQ中基于可重新配置FPGA的I/O定時(shí)和控制,方能實(shí)現(xiàn)高度靈活性和完全定制。 借助NI LabVIEW FPGA,觸發(fā)和同步任務(wù)獲得了簡(jiǎn)化,因?yàn)橥ㄟ^(guò)繪制圖形化程序框圖即可充分滿(mǎn)足用戶(hù)需求;借助獨(dú)立的模擬和數(shù)字I/O線(xiàn),智能DAQ可利用FPGA提供的實(shí)際并行。 R系列智能DAQ設(shè)備已經(jīng)針對(duì)多速率采樣、自定義計(jì)數(shù)器操作和頻率高達(dá)40 MHz的板載決策,為多功能數(shù)據(jù)采集進(jìn)行了各項(xiàng)可能的修繕。