隨著科學技術(shù)的發(fā)展和現(xiàn)代戰(zhàn)爭條件的變化,傳統(tǒng)圖像信號提供的單一服務已遠遠不能滿足現(xiàn)代戰(zhàn)爭的需要,。圖像信號由于包含有極其豐富的信息,,具有通信效率高,、便于記錄,、形象逼真,、臨場感強等特點,所傳送的信息量遠遠超過其他通信手段,,所以得到越來越多的重視,。在JPEG2000系統(tǒng)下,,視頻采集系統(tǒng)是視頻采集功能的FPGA(現(xiàn)場可編程門陣列)前端系統(tǒng),是視頻圖像處理,、應用的前項通道,。作為視頻采集系統(tǒng)的重要組成部分I2C(Inter Integrated Circuit)總線,早在20世紀80年代由荷蘭PHILIPS公司研制開發(fā)成功。它是一種簡單,、雙向二線制同步串行總線硬件接口。

l I2C總線的特點和協(xié)議

I2C總線協(xié)議作為一個串行總線標準,盡管沒有并行總線的數(shù)據(jù)吞吐能力,,但是它的特點和協(xié)議使其有著廣泛的應用,。其特點和協(xié)議主要有:

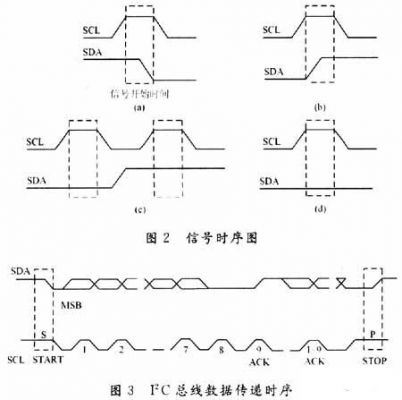

只需兩條總線即串行時鐘線(SCL)和串行數(shù)據(jù)線(SDA),,使得IC引腳數(shù)目降低,;且連接到總線的器件都是惟一地址,、從節(jié)點關(guān)系軟件設定地址,,主節(jié)點可以發(fā)送或者接收數(shù)據(jù)。是真正的多主總線,,當兩個或更多主節(jié)點同時初始化數(shù)據(jù)傳輸時,,可以通過沖突檢測和仲裁防止數(shù)據(jù)被破壞,。串行的8位雙向數(shù)據(jù)傳輸速率在標準模式下可達100Kb/s,,快速模式下達400 Kb/s,高速模式下達3.4 Mb/s,,連接到相同總線的IC數(shù)量只受到總線的最大電容(400pF)限制,。片上的濾波器可以濾去總線數(shù)據(jù)線上的毛刺波,,保證數(shù)據(jù)完整。

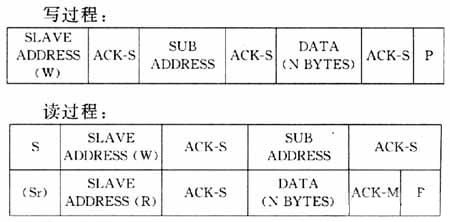

一般在總線不忙的情況下,,數(shù)據(jù)傳送才能開始,,在數(shù)據(jù)傳送期間,無論何時時鐘線為高,,數(shù)據(jù)線必須保持穩(wěn)定,,而且數(shù)據(jù)線和時鐘都必須保持為高電平。當時鐘線為高時,,數(shù)據(jù)線的變化將認為是傳送的開始或停止,,在這里,數(shù)據(jù)線由高到低的變化決定開始條件,。而且數(shù)據(jù)線由低到高的變化決定停止條件,。在滿足開始條件后,串行時鐘線(SCL)為低電平期間,,串行數(shù)據(jù)線(SDA)允許發(fā)生變化,但每位數(shù)據(jù)需一個時鐘脈沖,,當串行時鐘線(SCL)為高電平時,串行數(shù)據(jù)線(SDA)必須穩(wěn)定,,不能發(fā)生任何變化。主控器在應答時鐘脈沖高電平期間釋放串行數(shù)據(jù)線(SDA)線高,轉(zhuǎn)由接收器控制,。受控器在應答時鐘脈沖高電平期間必須拉低串行數(shù)據(jù)線(SDA)線,,使穩(wěn)定的低電平作為有效應答,。

2 系統(tǒng)結(jié)構(gòu)設計

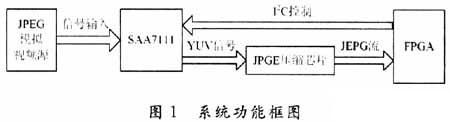

現(xiàn)有一些可編程視頻輸入處理芯片,如:SAA7111,,它的配置是通過I2C總線實現(xiàn)的,這種總線接口協(xié)議解決了設計數(shù)字控制電路時所遇到的許多接口問題,,大大降低了視頻輸入處理部分的設計難度。因此,,它被廣泛應用于視頻桌面系統(tǒng),、圖像多媒體、數(shù)字電視,、圖像處理,、視頻電話和音頻等領域。SAA7111芯片作為視頻的輸入處理部分,,用來實現(xiàn)模擬輸入視頻信號的數(shù)字化,。系統(tǒng)上電時,FPGA首先從外部配置芯片中讀取配置數(shù)據(jù),,進入工作模式狀態(tài),。隨后I2C配置模塊完成對SAA7111的初始化。初始化結(jié)束后,,F(xiàn)PGA等待采集圖像的命令,,F(xiàn)PGA收到采集命令后,視頻信號將進入視頻解碼器SAA7111進行A/D轉(zhuǎn)換,,以將模擬信息變成標準的YUV數(shù)字圖像信息,。系統(tǒng)功能框圖如圖1所示。

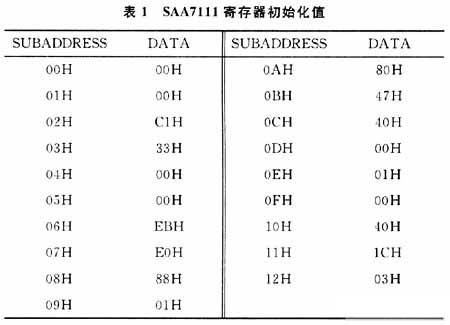

在對I2C總線設計中,,通過SAA7111上的I2C接口對其工作方式寄存器進行設置實現(xiàn)其功能。SAA7111是一款功能強大的模擬前端和數(shù)字視頻譯碼器,,常應用在嵌入式視頻應用的高度集成的電路中,。內(nèi)部包含兩路模擬處理通道,能實現(xiàn)視頻源的選擇,、抗混疊濾波,、A/D轉(zhuǎn)換、自動嵌位,、自動增益控制,、時鐘產(chǎn)生、多制式解碼以及亮度,、對比度和飽和度的控制,,從而將PAL,NTSC等不同制式的模擬復合視頻數(shù)據(jù)解碼成亮度,、色度和相關(guān)同步的數(shù)字信號,。SAA7111內(nèi)有32個寄存器(SLLbaddress00~1FH),其中22個是可編程的,。其中,,OOH,,1A~lCH,lFH是只讀寄存器,。00H描述的是芯片版本信息,;1A~1CH是文本信息檢測和解碼寄存器,一般很少用到,;lFH用來描述芯片的狀態(tài),。02H~12H是可讀/寫寄存器,其中:02H~05H是模擬輸入控制寄存器,,02H用于設置模擬視頻信號輸入方式(共8種),;03H~05H用于設置增益控制方式;06H~12H主要用于設置解碼方式,,通過配置這些寄存器可以設置行同步信號的開始和結(jié)束位置,,并可確定亮度、色度,、飽和度的大小以及輸出圖像數(shù)據(jù)信號的格式,。01H,13H~19H,,1DH~1EH寄存器保留使用,。

由于SAA7111加電復位之后,各寄存器處于不確定狀態(tài),,因此需要采用I2C總線協(xié)議由FPGA作為主方對SAA7111的相關(guān)寄存器進行設置,。從SAA7111的四個模擬輸入端AIll,AI12,,AI21,,AI22的某一引腳輸入的視頻圖像信號經(jīng)模擬處理后,一路可通過緩沖器輸出到AOUT端用于監(jiān)視,,另一路經(jīng)A/D轉(zhuǎn)換器后則產(chǎn)生數(shù)字色度信號和亮度信號,。在分別進行亮度信號處理和色度信號處理后,其亮度信號處理結(jié)果的一路將送到色度信號處理器進行綜合處理,,產(chǎn)生的Y和UV信號經(jīng)格式化后從VPO(16位)輸出,;另一路則進入同步分離器,并經(jīng)數(shù)字PLL產(chǎn)生相應的行和場同步信號HS和VS,。同時,,PLL將驅(qū)動時鐘發(fā)生器,以產(chǎn)生HS鎖定的時鐘信號LLC和LLC2,,SAA7111的所有功能均是在I2C總線控制下完成的,。SA-A7111相應的寄存器初始化值見表1。

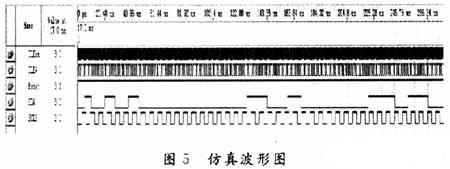

設計中利用QuartusⅡ集成環(huán)境采用VHDL語言實現(xiàn)了I2C總線對SAA7111中集成的symbol進行實驗仿真,。reset信號為外接復位信號,時鐘信號根據(jù)需要外接所需頻率時鐘信號(clk),,并根據(jù)要求對信號進行16分頻作為進程激勵信號(clkin)。對于上述初始化數(shù)據(jù),,仿真波形如圖5所示仿真結(jié)果輸出正確后,,配置與電路設計相符的入/輸出引腳。根據(jù)測試結(jié)果,,該設計可以穩(wěn)定可靠地對SAA7111進行參量控制,,如果需要修改只需更換程序中參量,再次編譯下載即可,。

該設計在視頻采集處理系統(tǒng)中已得到應用,,I2C總線接口數(shù)據(jù)采集正確、穩(wěn)定,,并且在實現(xiàn)過程中,,占用資源少,,僅為總資源的40 %。核心器件與圖像數(shù)據(jù)采集芯片配合使用,,節(jié)省核心處理芯片的通用I/O接口,,使系統(tǒng)整體電路十分簡潔、可靠性高,、集成度高,、接口方便等優(yōu)點。