ASIC、FPGA和DSP的應(yīng)用領(lǐng)域呈現(xiàn)相互覆蓋的趨勢,使設(shè)計人員必須在軟件無線電結(jié)構(gòu)設(shè)計中重新考慮器件選擇策略問題。本文從可編程性、集成度、開發(fā)周期、性能和功率五個方面論述了選擇ASIC、FPGA和DSP的重要準(zhǔn)則。

軟件無線電(SDR)結(jié)構(gòu)一直被認(rèn)為是基站開發(fā)的靈丹妙藥,而隨著其適應(yīng)新協(xié)議的能力不斷增強,軟件無線電結(jié)構(gòu)已被一些設(shè)計人員視為在單個基礎(chǔ)架構(gòu)設(shè)計中支持多種無線協(xié)議的重要解決方案。

直到最近,軟件無線電仍然只是大多數(shù)通信系統(tǒng)設(shè)計人員的規(guī)劃藍(lán)圖而已,但這一局面正迅速得到改觀。隨著3G無線業(yè)務(wù)的日趨臨近,設(shè)計人員又對在基礎(chǔ)架構(gòu)設(shè)計中實現(xiàn)軟件無線電結(jié)構(gòu)產(chǎn)生了濃厚的興趣。

實現(xiàn)軟件無線電

傳統(tǒng)的無線基礎(chǔ)架構(gòu)設(shè)計可采用ASIC、DSP和FPGA器件的組合加以實現(xiàn)。在這些設(shè)計中,ASIC和FPGA通常負(fù)責(zé)處理高級編碼機(jī)制,如Reed Solomon編碼、Viterbi編碼及Rake接收機(jī),而DSP則負(fù)責(zé)語音編碼及其他語音處理任務(wù)。

在由傳統(tǒng)的無線架構(gòu)設(shè)計轉(zhuǎn)向軟件無線電設(shè)計的過程中,DSP、FPGA和ASIC之間的功能劃分也在發(fā)生變化。ASIC逐漸提供更多的可編程功能,而DSP和FPGA則開始具備ASIC的傳統(tǒng)處理功能,三者之間的界限正變得日益模糊。因此,當(dāng)設(shè)計人員設(shè)計軟件無線電時,他們發(fā)現(xiàn)已很難劃分ASIC、DSP和FPGA三者之間的功能界限。

現(xiàn)在設(shè)計人員必須耗費相當(dāng)多的精力來權(quán)衡下面一些問題:傳統(tǒng)上由ASIC實現(xiàn)的功能能否由FPGA或DSP更好地加以實現(xiàn)?或者傳統(tǒng)上由DSP實現(xiàn)的功能是否由FPGA或ASIC實現(xiàn)更為合適?因此問題的核心是如何制訂出正確的選擇準(zhǔn)則并對每種處理方案進(jìn)行有效的評估。

準(zhǔn)則選取

在選擇任何準(zhǔn)則之前,有必要給出軟件無線電的精確定義。在底板各處,開發(fā)人員可為軟件無線電結(jié)構(gòu)的構(gòu)成給出許多不同的定義,但本文將采用軟件無線電論壇(www.sdRForum.org)的方法,將軟件無線電定義為“在較大頻率范圍內(nèi),能對目前已有的以及將來會出現(xiàn)的諸多調(diào)制技術(shù)、寬帶及窄帶操作、通信安全功能(如跳頻)和信號波形等的標(biāo)準(zhǔn)要求進(jìn)行軟件控制的無線電”。

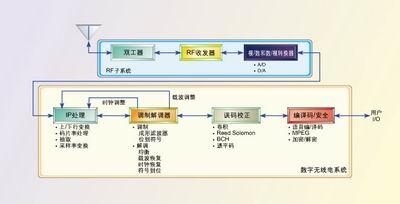

歷史上,采用單個空間接口標(biāo)準(zhǔn)設(shè)計的噴氣式飛機(jī)中已經(jīng)實現(xiàn)了數(shù)字無線系統(tǒng),該設(shè)計在考慮成本的基礎(chǔ)上(見圖1),使用了任意可編程器件對系統(tǒng)進(jìn)行評估。而在軟件無線電中,無線電的每個主要功能器件(包括射頻收發(fā)器)都具備在空中進(jìn)行重配置以支持多種空間接口標(biāo)準(zhǔn)的特性。

總之,當(dāng)選擇ASIC、FPGA或DSP時,設(shè)計人員應(yīng)當(dāng)考慮以下5個重要的選擇準(zhǔn)則。1. 可編程性:對于所有的目標(biāo)空間接口標(biāo)準(zhǔn),器件均能重新配置以執(zhí)行所期望的功能。2. 集成度:在單個器件上集成多項功能,由此減小數(shù)字無線子系統(tǒng)的規(guī)格并降低硬件復(fù)雜度的能力。3. 開發(fā)周期:開發(fā)、實現(xiàn)及測試指定器件的數(shù)字無線功能的時間。4. 性能:器件在要求的時間內(nèi)完成指定功能的能力。5. 功率:器件完成指定功能的功率利用率。

可編程性

DSP和FPGA可輕易地進(jìn)行重配置,以實現(xiàn)軟件無線電設(shè)計的各種功能。現(xiàn)有的通信ASIC雖然可以較低的成本提供更好的性能,但提供的可編程能力非常有限。

問題的關(guān)鍵是,在諸多的無線ASIC中是否有一種適合于特定要求的數(shù)字無線產(chǎn)品。在純軟件無線電結(jié)構(gòu)中,顯然沒有一種ASIC具有這樣的功能,但實際上也只有很少的數(shù)字無線設(shè)計需要這樣高的靈活性。因此軟件無線電產(chǎn)品開發(fā)的關(guān)鍵步驟就是確定系統(tǒng)每項功能所需的可編程特性,并確定現(xiàn)有的ASIC是否可以提供這項功能。

確定器件的處理功能可通過既支持W-CDMA也支持GSM的基站收發(fā)器結(jié)構(gòu)來說明。由于W-CDMA采用了擴(kuò)頻通信技術(shù),因此許多用戶可共享一條射頻(RF)信道。在上行鏈路1,920至1,980MHz之間和下行鏈路2,110至2,170 MHz之間,W-CDMA信號在每條信道中占據(jù)5MHz的帶寬。

另一方面,在GSM系統(tǒng)的每條射頻信道中,窄帶TDMA技術(shù)一般只支持8個用戶。在上行鏈路890至915MHz之間和下行鏈路935至960MHz之間,窄帶TDMA的每條信道占據(jù)200kHz帶寬。

為了在軟件無線電結(jié)構(gòu)中有效地兼顧上述標(biāo)準(zhǔn)間的差異,中頻(IF)處理器的數(shù)字上行轉(zhuǎn)換器和下行轉(zhuǎn)換器都必須提供可編程的信道選擇、濾波器配置和采樣比調(diào)節(jié)。Intersil、Graychip和Analog Devices公司的新型多標(biāo)準(zhǔn)數(shù)字收發(fā)器ASIC均可提供許多可編程特性。

然而,由于4G標(biāo)準(zhǔn)尚未定義,而且在該結(jié)構(gòu)中任何ASIC信號處理器件的使用都將給未來的升級帶來無法預(yù)料的風(fēng)險,因此中頻處理也必須使用FPGA或DSP器件。

隨著信號處理越來越多的來自數(shù)字中頻輸入,4G結(jié)構(gòu)中的處理算法也變得越來越專業(yè)化,這限制了單個ASIC器件滿足所需可編程要求的能力。

在3G/GSM無線應(yīng)用中,W-CDMA采用了由透平編碼和卷積編碼組合而成的糾錯機(jī)制,由此滿足所需的誤碼率(BER)性能要求。另一方面,GSM采用卷積編碼和Fire編碼的組合作為其糾錯機(jī)制,因此定位于特定糾錯算法的商用ASIC器件將不再適用于GSM平臺,而FPGA或DSP實現(xiàn)則是一種更好的選擇。

集成度

ASIC器件在軟件無線電結(jié)構(gòu)設(shè)計中的另一劣勢是集成度。隨著ASIC、DSP和FPGA開發(fā)技術(shù)的不斷進(jìn)步,在單個器件中集成的功能也急劇增加。但對于ASIC,靈活性將隨集成度的增加而降低。

例如,充當(dāng)數(shù)字收發(fā)器的ASIC芯片完全適用于多種空中接口標(biāo)準(zhǔn),包括GSM、IS-136、CDMA2000和UMTS W-CDMA。如果在ASIC中添加了CDMA碼片率處理器,那么該ASIC就不再適用于GSM和IS-136。如果在ASIC中添加一個支持QPSK、8PSK和16QAM調(diào)制方案的調(diào)制器或解調(diào)器,就能使其成為實現(xiàn)CDMA高速數(shù)據(jù)速率(HDR)規(guī)范的有效解決方案,但不再適用于任何其他標(biāo)準(zhǔn)。

在這一級集成度上,多個ASIC器件需要支持多個空間接口標(biāo)準(zhǔn),但這通常有些不切實際。

與ASIC器件相比,DSP或FPGA器件可輕松地集成多種數(shù)字無線功能,并且不會顯著降低器件的靈活性。

在上例中,CDMA2000 HDR ASIC提供的大多數(shù)功能均能在Xilinx公司的XCV1000E上實現(xiàn),如表1所示。這樣的集成度通常導(dǎo)致這些產(chǎn)品與基于ASIC的器件相比,具有更小的整體波形因數(shù)以及更高的靈活性。

ASIC器件的靈活性在軟件無線電產(chǎn)品的開發(fā)中也具有其優(yōu)勢:現(xiàn)有的ASIC算法開發(fā)已經(jīng)相當(dāng)完善,這有助于縮短產(chǎn)品的上市時間。硬件設(shè)計是基于ASIC功能的關(guān)鍵開發(fā)進(jìn)程,而軟件開發(fā)則受制于接入器件可編程特性的程序庫生成。

基于DSP或FPGA的設(shè)計開發(fā)周期則要復(fù)雜得多,因為軟件開發(fā)需要的資源通常比相應(yīng)的硬件開發(fā)多得多。現(xiàn)有的經(jīng)優(yōu)化通用算法程序庫有利于加速DSP和FPGA的軟件開發(fā),但這些算法必須集成在一起實現(xiàn)期望的數(shù)字無線功能,因此需要完整的軟件開發(fā)周期。

設(shè)計人員還必須注意DSP和FPGA軟件開發(fā)方法之間的主要差異。在DSP上編譯算法的時間通常以秒計算,而在FPGA上綜合處理并對類似算法進(jìn)行布線的時間則需要數(shù)小時。例如Xilinx公司的典型FPGA布線速率為每小時400,000個門電路,因此帶有2百萬個門電路的XCV2000E的編譯可能需要半天的時間才能完成。

這使得FPGA的設(shè)計調(diào)試成為一項昂貴的過程,因此FPGA的設(shè)計周期通常需要在對器件算法進(jìn)行布線之前,進(jìn)行更多的先期分析,包括多路仿真和模型測試。

性能

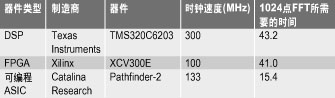

在軟件無線電結(jié)構(gòu)中,任何信號處理器件的鑒定必須包括衡量該器件是否能在指定的時間內(nèi)完成所需的功能。這類評估中一種最基本的基準(zhǔn)點測量就是1,024點快速傅立葉變換(FFT)處理時間的測量,參見表2中的突顯部分。

對DSP和FPGA功能實現(xiàn)的性能進(jìn)行比較相當(dāng)困難,因為這些器件的結(jié)構(gòu)分別用于處理不同類型的問題。DSP工作于非常高的速率條件下,但在某一時刻只能完成有限的處理任務(wù)。另一方面FPGA的工作速率通常低于DSP的速率,但對同時可完成的處理任務(wù)則幾乎沒有限制。

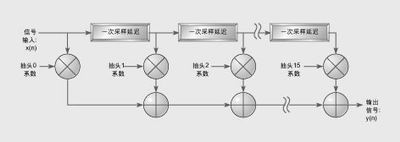

為了說明上述這些差異,考慮如圖2所示的具有16個抽頭的簡單FIR濾波器。該濾波器要求在每次采樣中完成16次乘積和累加(MAC)操作。德州儀器公司的TMS320C6203

DSP具有300MHz的時鐘頻率,在合理的優(yōu)化設(shè)計中,每秒可完成大約4億至5億次MAC操作。這意味著C6203系列器件的FIR濾波具有最大為每秒3,100萬次采樣的輸入速率。

附加功率

ASIC器件的設(shè)計通常經(jīng)過優(yōu)化以提供卓越的功率性能。但大多數(shù)可編程器件的功率將隨器件利用率和時鐘頻率的增加而急劇增長,因此在衡量整體設(shè)計的功率分配時,必須考慮這一因素。

例如,利用Altera公司的20K600可編程邏輯器件(PLD)實現(xiàn)的4信道下行轉(zhuǎn)換器只需消耗不到2W的功率,即可實現(xiàn)每秒2,500萬次采樣的輸入數(shù)據(jù)率。這樣的功率雖然比較高,但對于指定的應(yīng)用還是可以接受的。如果將輸入數(shù)據(jù)率提高至每秒6,500萬次采樣,那么消耗的功率將達(dá)到5W,這超出了許多數(shù)字無線產(chǎn)品所能承受的功率門限。

與Altera 20K600相比,在相同的輸入數(shù)據(jù)率條件下,Analog Devices 公司的AD66244信道下行轉(zhuǎn)換器ASIC消耗的功率為700mW。

在較低的速率條件下,F(xiàn)PGA的功率利用率通常優(yōu)于高端DSP。為對此加以說明,考慮Dish

Network公司在數(shù)字視頻廣播中采用的糾錯機(jī)制。在該系統(tǒng)中速率高達(dá)27.647Mbps的多路復(fù)用數(shù)據(jù)采用Reed-Solomon糾錯機(jī)制進(jìn)行編碼,該機(jī)制為每188個數(shù)據(jù)字節(jié)直接生成16個奇偶校驗字節(jié),并生成最大為30Mbps的合成數(shù)據(jù)率。

在5,000個時鐘周期中,TMS320C6203可解碼204個字節(jié)的Reed-Solomon代碼字。為實現(xiàn)所需的數(shù)據(jù)吞吐量,在300 MHz頻率下,CPU必須實現(xiàn)近50%的利用率,而消耗的功率約為1.53W。

與此相反,在Xilinx XCV100E上實現(xiàn)的Reed-Solomon解碼器設(shè)計消耗的功率僅為200mW。這是一個巨大的改進(jìn),可以與商用Reed-Solomon ASIC(如Advanced Hardware Architectures公司的AHA4011C)具備的性能相媲美。

器件選擇

表3總結(jié)了上述結(jié)果。表中每類器件按1至5的標(biāo)度主觀地設(shè)定功率極限,1表示該類較差的選擇,而5則表示最佳選擇。

FPGA可為高度并行或涉及線性處理的高速信號處理功能提供最佳的可編程解決方案。3. DSP可為涉及復(fù)雜分析或決策分析的功能提供最佳可編程解決方案。

隨著技術(shù)的進(jìn)步,DSP、ASIC和FPGA將在芯片上支持更多的功能,這進(jìn)一步模糊了三者之間的界限。而對于軟件無線電設(shè)計人員,這意味著他們在今后的設(shè)計中將面臨更難的選擇。