正交頻分復(fù)用(OrthogonalFrequency Division Multiplexing,OFDM)技術(shù)已經(jīng)成為第四代移動(dòng)通信研究的熱點(diǎn),同時(shí),OFDM同步又是OFDM的關(guān)鍵技術(shù),研究OFDM同步技術(shù)的目的就是為了防止碼間干擾和載波干擾。當(dāng)前OFDM同步的算法是根據(jù)OFDM原理提出的基于數(shù)據(jù)符號(hào)方法,它的優(yōu)點(diǎn)是捕獲快、精度高,適合分組數(shù)據(jù)通信,具體的實(shí)現(xiàn)是在分組數(shù)據(jù)包的包頭加一個(gè)專(zhuān)門(mén)用來(lái)做定時(shí)、頻偏的OFDM塊。基于數(shù)據(jù)符號(hào)的算法又可以分為兩類(lèi):基于訓(xùn)練符號(hào)(導(dǎo)頻碼)的方法和基于循環(huán)前綴(CP)的方法。其中基于循環(huán)前綴的方法是在OFDM符號(hào)中插入保護(hù)間隔,保護(hù)間隔取符號(hào)尾部最后若干個(gè)樣點(diǎn)的復(fù)制,當(dāng)其中的任何一個(gè)位于保護(hù)間隔內(nèi)時(shí),另-個(gè)與它相同,兩者的相關(guān)性較強(qiáng);當(dāng)不在保護(hù)間隔內(nèi)時(shí),這兩個(gè)樣點(diǎn)是獨(dú)立的。利用保護(hù)間隔的這些特性可以完成OFDM系統(tǒng)中符號(hào)定時(shí)偏差和載波頻偏估計(jì)。

基于循環(huán)前綴的同步算法

本文要討論的基于ML(最大似然估計(jì))時(shí)頻同步算法是vande Beek等人提出來(lái)的,這是一個(gè)利用CP所攜帶的信息完成定時(shí)同步和載波同步的最大似然估計(jì)算法。它利用OFDM系統(tǒng)循環(huán)冗佘擴(kuò)展的循環(huán)前綴攜帶的信息進(jìn)行同步估計(jì),避免了基于導(dǎo)頻碼的同步估計(jì)帶來(lái)的頻率和功率資源的浪費(fèi)。

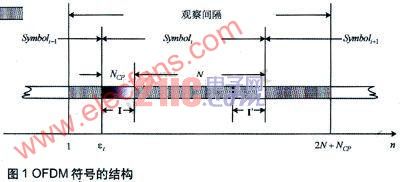

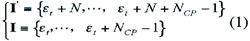

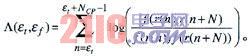

如圖1所示,假設(shè)觀(guān)察接收信號(hào)r(n)的連續(xù)2N+NCP個(gè)樣值。在這些樣值中必然包含了一個(gè)長(zhǎng)為N+NCP的OFDM符號(hào)。由于無(wú)法知道符號(hào)的開(kāi)始位置,只能將其設(shè)為變量。定義兩個(gè)索引集合(Indexsets):

其中,I表示的是OFDM符號(hào)最后NCP個(gè)樣值,I′表示的是循環(huán)前綴的樣值。將觀(guān)察區(qū)間內(nèi)的2N+NCP個(gè)樣值作為一個(gè)集合,可表示為:

由于循環(huán)前綴是OFDM符號(hào)后一段的復(fù)制,所以集合和集合中的元素是相同的。

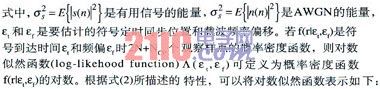

式(4)中同時(shí)使用了一維和二維概率密度函數(shù)。其中乘積項(xiàng)![]() 是對(duì)所有2N+NCP點(diǎn)求乘積,所以與符號(hào)起點(diǎn)εt兀關(guān),如果假設(shè)信息是獨(dú)立同分布的,即r(n)的實(shí)部和虛部是互相獨(dú)立的,則

是對(duì)所有2N+NCP點(diǎn)求乘積,所以與符號(hào)起點(diǎn)εt兀關(guān),如果假設(shè)信息是獨(dú)立同分布的,即r(n)的實(shí)部和虛部是互相獨(dú)立的,則![]() 也與εf無(wú)關(guān),所以可以忽略

也與εf無(wú)關(guān),所以可以忽略![]() 。據(jù)此式(4)可以被化簡(jiǎn)為:

。據(jù)此式(4)可以被化簡(jiǎn)為:

根據(jù)集合I的范圍,式(5)也可以寫(xiě)作:

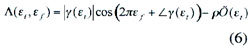

通過(guò)一系列代數(shù)運(yùn)算之后,可被簡(jiǎn)化為:

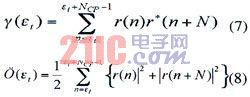

其中∠表示取復(fù)數(shù)的角度,且:

r(n)和r(n+N)的相關(guān)系數(shù)的幅度用ρ表示。

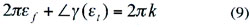

對(duì)于頻偏εf而言,要使式(6)最大,即使余弦項(xiàng)達(dá)到最大值1,即:

其中k為整數(shù)。由于余弦函數(shù)有周期性,所以根據(jù)k的不同會(huì)得到很多個(gè)最大值。如果考慮|εf|<0.5,則k=0。這樣就得到εf的極大似然估計(jì)值:

![]()

要估計(jì)出頻偏就必須對(duì)符號(hào)精確定時(shí)。由此繼續(xù)簡(jiǎn)化可得到:

![]()

由于式(11)只與時(shí)偏有關(guān),所以可以得到的極大似然估計(jì)值為:

![]()

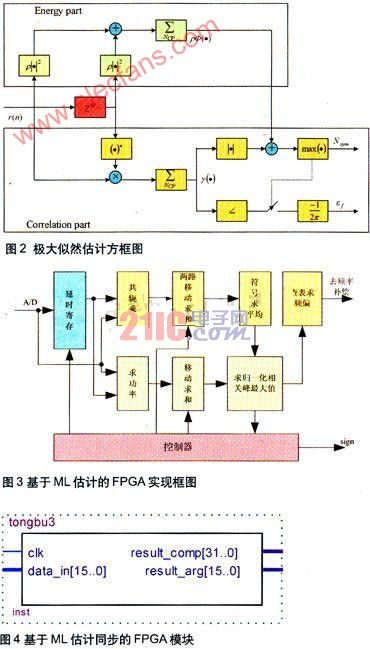

圖2顯示了極大似然估計(jì)算法的方框圖。它增加了能量部分,能量部分是通過(guò)極大似然準(zhǔn)則推導(dǎo)出來(lái)的,能量部分的引入彌補(bǔ)了單純利用循環(huán)前綴相關(guān)性算法的缺點(diǎn),使得定時(shí)更準(zhǔn)確。

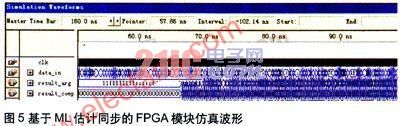

算法的FPGA實(shí)現(xiàn) 圖3所示是同步算法FPGA實(shí)現(xiàn)框圖,設(shè)計(jì)采用512抽樣點(diǎn),最大保護(hù)間隔按照NCP=512×1/4=128計(jì)算。工作過(guò)程大致如下:

512位復(fù)數(shù)數(shù)據(jù)通過(guò)寫(xiě)地址存儲(chǔ)到延時(shí)寄存器,存滿(mǎn)以后通過(guò)讀地址讀出前128位復(fù)數(shù),同時(shí)和后面的直接輸入128位數(shù)據(jù)送到后級(jí)模塊,兩路數(shù)據(jù)分別做共軛乘。延時(shí)寄存器模塊可用一個(gè)512×16的雙端口 RAM,RAM的讀寫(xiě)地址分別為128位計(jì)數(shù)器和512位計(jì)數(shù)器。共軛乘后的復(fù)數(shù)數(shù)據(jù)流送給兩路移動(dòng)求和模塊,求功率后的值送給一路移動(dòng)求和模塊。控制器對(duì)累加器清零,同時(shí)控制RAM的讀寫(xiě)和使能信號(hào)的產(chǎn)生。累加器采用16位二進(jìn)制數(shù)累加,兩路16位的數(shù)據(jù)移動(dòng)求和之后去求符號(hào)平均,然后再和另一路移動(dòng)求和的結(jié)果運(yùn)算歸一化,求相關(guān)峰最人值,若出現(xiàn)相關(guān)峰的最大值,就表明同步的到來(lái),這時(shí)標(biāo)記該數(shù)據(jù)的地址,然后讓控制器發(fā)出標(biāo)志位置高指令,通知從該數(shù)據(jù)開(kāi)始就可以進(jìn)行FFT解調(diào)處理。如果沒(méi)有相關(guān)峰最大值的出現(xiàn),系統(tǒng)再循環(huán)讀出后128位地址數(shù)據(jù),重復(fù)前面的運(yùn)算,直到找到最大相關(guān)峰。

在求歸一化相關(guān)峰最大位置模塊中,先求出平均移動(dòng)和的實(shí)虛部絕對(duì)值之和,再除以功率,得歸一化相關(guān)值。南于歸一化值為小數(shù),故需給結(jié)果乘以一因子,這里取2。由于ML同步脈沖是在最大值后持續(xù)ML窗寬時(shí)間輸出,這期間最大值對(duì)應(yīng)的相關(guān)和實(shí)、虛部保持不變,故求頻偏模塊可順序計(jì)算,只須用ML同步脈沖將求頻偏模塊輸出的頻偏鎖定輸出。

經(jīng)過(guò)QuartusII 5.0工具的設(shè)計(jì)、編譯、綜合等一系列步驟,基于PN序列同步系統(tǒng)融合成一個(gè)整體模塊,如圖4所示。仿真結(jié)果如圖5所示。

結(jié)語(yǔ)

上述FPGA實(shí)現(xiàn)的是基于數(shù)據(jù)符號(hào)的OFDM系統(tǒng)同步算法,采用Altera公司的芯片EPlS25102015進(jìn)行試驗(yàn)仿真,該芯片有25660個(gè)邏輯單元,1944576個(gè)存儲(chǔ)模塊單元,80個(gè)DSP模塊單元,707個(gè)I/O輸出引腳。

基于循環(huán)前綴的同步算法占用芯片資源適中,但是占用了27%的芯片I/O引腳,另外,時(shí)鐘頻率也較低,設(shè)計(jì)電路較難,但是它達(dá)到更高的同步精度還要結(jié)合其他同步方式,它也可以應(yīng)用于無(wú)線(xiàn)信道通信中。綜合算法設(shè)計(jì)占用芯片資源以及相關(guān)情況的分析,算法在FPGA中的實(shí)現(xiàn)是可行且可靠的,充分發(fā)揮了FPGA芯片集成密度大、速度快、功耗低、通用性好、適應(yīng)性強(qiáng)和重復(fù)編程的特點(diǎn)。通常,可編程邏輯芯片都能提供人容量的邏輯和存儲(chǔ)單元,因此,芯片預(yù)留資源都是有富余的,信號(hào)處理的實(shí)時(shí)性和可靠性是關(guān)注的重點(diǎn),當(dāng)然成本也是考慮的一個(gè)因素,與此同時(shí),也要考慮電路的設(shè)計(jì)復(fù)雜程度,因?yàn)樗鼤?huì)影響數(shù)據(jù)處理的速度。