0 引 言

Cadence Design Systems Inc.是全球最大的電子設計技術、程序方案服務和設計服務供應商。它的解決方案旨在提升和監(jiān)控半導體、計算機系統(tǒng)、網絡工程和電信設備、消費電子產品以及其他各類型電子產品的設計。Cadence公司的電子設計自動化產品涵蓋了電子設計的整個流程,包括系統(tǒng)級設計、功能驗證、IC綜合及布局布線、模擬和混合信號及射頻IC設計、全定制集成電路設計、IC物理驗證、PCB設計和硬件仿真建模等。Cadence軟件支持自頂向下(Top-down)的芯片設計,是業(yè)界廣泛采用的設計工具。該軟件通過Li-brary CelI View三級目錄輔助芯片設計:

(1)設計者為自己要完成的系統(tǒng)任務建立新的Li-brary;

(2)分析系統(tǒng)及其指標來確定系統(tǒng)的各個模塊,每個模塊對應于Library中的一個Cell;

(3)每個模塊的設計包括電路(Schematic)設計和版圖(Layout)設計,兩者密不可分,電路圖與版圖都是模塊中的View。

同時,Cadence公司還提供設計方法教學服務,幫助客戶優(yōu)化其設計流程;提供設計外包服務,協(xié)助客戶進入新的市場領域。垂直解決方案是Cadence 為幫助IC設計公司迅速建立設計架構,并獲得更短、可預測性更高的設計周期而推出的獨具特色的整套解決方案,其目標是為了推動不同領域產品的開發(fā)步伐,設計錦囊(Process Design Kit,PDK)是其重要組成部分。“錦囊”通過將驗證方式和流程與IP相結合的方式,更好地應對無線、網絡和消費電子等不同領域在設計方面的挑戰(zhàn)。通過采用“錦囊”,用戶可將其寶貴的資源投入在差異化設計而不是基礎設計方面。

1 低噪聲放大器電路設計

(1)電路結構。圖1是此次實驗中所用電路的完整電路原理圖。圖中共源管M1作為主放大管,給電路提供足夠的增益;共柵管 M2用來減小M1的Cgd1引起的密勒效應以及增強整個電路的反向隔離性能;M3,Rref,Rbias構成偏置電路,以實現(xiàn)M1所需的直流偏置。對于輸入/輸出匹配電路,可以利用Smith圓圖完成初步設計;然后利用Cadence軟件套件中用于集成電路仿真的組件IC 5.1進行更加精確的電路參數調試。

(2)電路設計。設計中采用新加坡特許(CHRT)的0.35μm RF CMOS工藝。電路工作在2.4 GHz,信號源電阻為50 Ω,M1的偏置電流取為5 mA。根據文獻[3],通過計算可得CHRT 0.35 μm COMS工藝Cox的值約為4.6mF/m2,根據文獻[4,5]可以得到最優(yōu)柵寬公式:Wopt△1/3ωLCoxRs,計算得M1的最優(yōu)寬度約為 240μm。根據公式RS=ωtLS,可得LS的值約為O.54 nH。根據公式CRS=(2/3)WoptLCox,得到CgS的值約為150 fF。將LS和CgS的值代入公式![]() 為輸入信號角頻率),可以得到Lg的值約為16.2 nH。偏置電路中M3的尺寸和電流選為M1的1/2。

為輸入信號角頻率),可以得到Lg的值約為16.2 nH。偏置電路中M3的尺寸和電流選為M1的1/2。

2 仿真與調試

(1)電路原理圖仿真。IC 5.1.41中用到的原理圖編輯器是Virtuoso Schematic Editor。首先,在編輯器中輸入圖1所示的低噪聲放大器完整的電路原理圖。接著,為了完成電路仿真,得到所需的電路參數,還需要在模擬環(huán)境 (Analog Design Environment)進行必要的設置,比如電路中用到的各個變量取值、S參數仿真(SP仿真)或者直流(DC)仿真的參數等。這些在軟件的用戶手冊 (Cdsdoc)以及一些相關的使用教程里面都有詳細的說明,在此不再重復。

在必要的軟件設置都完成之后,便可以順利地將電路原理圖轉換成網表并仿真(Netlist and Run),從而得到感興趣的電路參數,軟件默認啟動的仿真器是spec-tre。在此次的低噪聲放大器設計過程中,主要關注電路的S參數、噪聲系數FN。

為了將輸出阻抗匹配到50 Ω,首先可以利用Smith圓圖來完成輸出匹配的初步設計。通過計算,本次設計需要在負載電路端并聯(lián)一個電容Cout1,然后串聯(lián)一個電容Cout2。通過調試,確定Cout1和Cout2的值分別約為180 fF和450 fF。

(2)電路版圖設計。版圖是集成電路設計中十分重要的一環(huán),它對射頻電路的性能有很大的影響。由于工作頻率很高,寄生效應和襯底耦合效應很明顯,因此要整體考慮其布局布線,盡量減小寄生參數的影響。首先,布局要合理,要注意信號線的走線長度,無源器件,特別是電感和其他部分要保持適當的間距;信號線要盡量寬些,這樣可以降低串聯(lián)電感和寄生電阻;

要盡可能的多用地線,電源線與地線盡量平行,以形成去耦電容,達到去除電源的高頻耦合分量的目的;

電源線盡量采用底層金屬,RF信號線盡量采用頂層金屬,而在版圖空白處盡量多布地線,盡可能地降低走線過程中的襯底損耗和串擾。

結合CHRT 0.35μm RF CMOS工藝的PDK,可以很方便地生成電路的元器件版圖輸出,接著完成必要的電路連線,便可以得到電路的版圖結果。

電路實現(xiàn)版圖設計之后還需要完成物理驗證。

此次采用的驗證工具是IC 5.1中自帶的DIVA。除此之外,也可以采用Cadence公司的ASSura,或者Mentor Grahphics公司的Calibre。物理驗證的過程包括設計規(guī)則檢查(DRC)、版圖原理圖對比(LVS)以及寄生參數提取(Extract)三個步驟。

在版圖編輯器(Layout XL Edit)的Verify菜單當中,可以找到DRC,LVS,Extract對應的選項;在完成了必要的參數設置之后,便可以完成電路的物理驗證。在做完寄生參數提取之后,便可以利用包含寄生參數的電路完成電路后仿真(Post-layout simulation),從而得到與實際電路性能更為接近的各項仿真結果。

(3)實驗結果。在完成最終電路的調試后,得到了各項仿真結果。

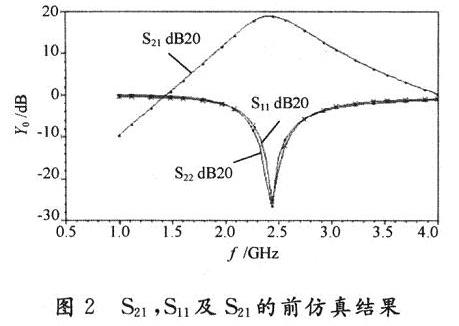

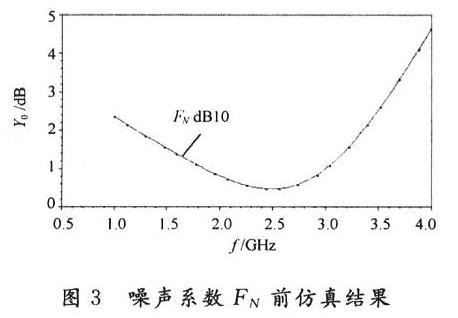

圖2、圖3分別是用電路原理圖仿真(即前仿)得到的S參數以及噪聲系數FN的實驗結果。

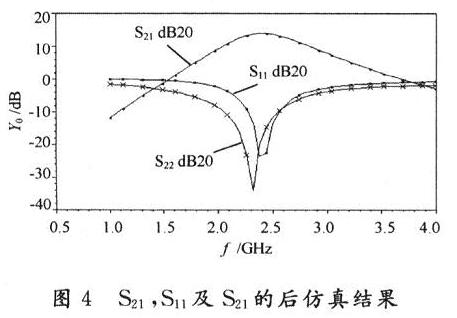

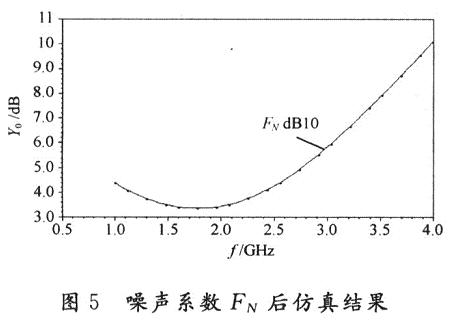

圖4、圖5是完成版圖之后,考慮寄生參數的電路后仿真結果。圖4是S參數的后仿真結果。由S11,S22的曲線可知,在2.4 GHz的中心頻率附近,S11,S22<-10 dB。可見,輸入、輸出電路均有比較好的匹配。圖5是噪聲系數FN的后仿真結果。圖6為電路版圖。

與電路的前仿結果相比,后仿真的噪聲系數有一定的上升,這說明電路中的寄生參數會使電路的噪聲性能惡化。

3 結 語

結合一個具體的低噪聲放大器(LNA)設計實例,采用CHRT的0.35μm RFCMOS工藝,在EDA軟件IC 5.1設計環(huán)境中設計了一個2.4 GHz的低噪聲放大器。設計過程中完成了電路原理圖仿真、版圖設計以及后仿真。實驗結果表明該低噪聲放大器具有較好的電路性能。結合設計過程,還介紹了如何運用Cadence軟件對CMOS低噪聲放大器進行電路設計和仿真。