基于SOC應(yīng)用,采用TSMC 0.18μm CMOS工藝,設(shè)計實現(xiàn)了一個低電壓、高增益的恒跨導(dǎo)軌到軌運算放大器IP核。

該運放采用了一倍電流鏡跨導(dǎo)恒定方式和新型的共柵頻率補償技術(shù),比傳統(tǒng)結(jié)構(gòu)更加簡單高效。用Hspice對整個電路進行仿真,在1.8V電源電壓、10pF負載電容條件下,其直流開環(huán)增益達到103.5dB,相位裕度為60.5度,輸入級跨導(dǎo)最大偏差低于3%。

1引言

在SOC的模擬集成電路設(shè)計中,使用簡單的電路結(jié)構(gòu)來實現(xiàn)高性能成為趨勢,SOC的設(shè)計核心是IP核設(shè)計。運算放大器是模擬電路中最重要的電路單元之一,廣泛應(yīng)用于如數(shù)/模、模/數(shù)轉(zhuǎn)換器和開關(guān)電容電路中[1-2]。隨著電源電壓的不斷降低,為了提高動態(tài)范圍,軌到軌(Rail to Rail)設(shè)計變得十分重要。

通常采用互補差分對實現(xiàn)輸入級共模電壓的Rail to Rail, 但其跨導(dǎo)在整個輸入范圍內(nèi)變化接近一倍[3],這使得頻率補償變得很困難,運放穩(wěn)定性變差。Rail to Rail運放通常需要兩個電容作為Miller補償以提供足夠的相位裕度[4],這不僅會占用大量的面積,也限制了單位增益帶寬。

從IP核的設(shè)計角度出發(fā),本文所設(shè)計的運放采用一倍電流鏡跨導(dǎo)控制電路恒定輸入級跨導(dǎo),這種方式結(jié)構(gòu)簡單,電路芯片面積小,同時也不會增加輸入級的噪聲。輸出級采用AB類推挽結(jié)構(gòu),它能夠在低壓下實現(xiàn)全擺幅的輸出,并且可以在保證低失真的情況下,得到較高的電源效率。針對AB類輸出級的特殊結(jié)構(gòu),采用了一種新型的共柵頻率補償技術(shù)[5],可以消除右半平面低頻零點,而且只需要一個補償電容,不僅提高了單位增益帶寬,也節(jié)省了芯片面積。仿真結(jié)果表明,該運放能夠在1.8V的低電源電壓下穩(wěn)定工作,非常適合于低電壓SOC應(yīng)用。

2電路結(jié)構(gòu)和原理

2.1 Rail to Rail輸入級及跨導(dǎo)控制

為了使運放的共模輸入在整個電源范圍內(nèi)變化時電路都能正常工作,采用NMOS 管和PMOS管并聯(lián)的互補差分輸入對結(jié)構(gòu)來實現(xiàn)輸入級的Rail to Rail。根據(jù)輸入共模電壓的不同,輸入級可分為三個工作區(qū)域[6]:當(dāng)共模輸入電壓接近VSS時,僅PMOS輸入對導(dǎo)通,輸入級跨導(dǎo)為 ;當(dāng)共模輸入電壓接近VDD時,僅NMOS輸入對導(dǎo)通,跨導(dǎo)為 ;當(dāng)共模輸入電壓處于中間值時,p 溝和n 溝輸入對均導(dǎo)通,跨導(dǎo)為:

![]()

由上式可知,Rail-to-Rail 結(jié)構(gòu)的輸入級跨導(dǎo)會在整個共模輸入范圍內(nèi)變化將近一倍。若將其運用于帶有反饋回路的運放中,其環(huán)路增益也變化近一倍,必將引起失真的增大。當(dāng)輸入級跨導(dǎo)增大一倍,則單位增益頻率增大一倍,從而導(dǎo)致相位裕度減小,運放穩(wěn)定性變差,這也造成了頻率補償很難實現(xiàn)。所以必須將其改進以恒定跨導(dǎo)。

本文設(shè)計的Rail-to-Rail 輸入級工作在弱反型區(qū),MOS管總輸入跨導(dǎo)可由下式給出:

其中, 是PMOS輸入對的尾電流, 是NMOS輸入對的尾電流, 分別是PMOS和NMOS輸入對的弱反型斜率因子。

由(2)式可知,工作在弱反型區(qū)的MOS管跨導(dǎo)與漏電流成正比。所以可通過保持互補輸入對總的尾電流恒定來穩(wěn)定 。假設(shè)兩類晶體管的弱反型斜率因子相同,要得到恒定的 ,其總的尾電流應(yīng)滿足:

![]()

滿足上述要求的Rail-to-Rail 輸入級結(jié)構(gòu)如圖1所示,由通過電流開關(guān)M7和一倍電流鏡M5-M6來實現(xiàn)輸入級的gm 控制。若共模輸入電壓較低,電流源 偏置于PMOS輸入對M3-M4,僅有PMOS輸入管對輸入信號有放大作用。當(dāng)共模輸入電壓升高到(VDD-VB1)時,電流開關(guān)M7 就會分走 的部分電流,并通過電流鏡M5-M6 將其注入到NMOS輸入對中。因此,輸入對總的尾電流恒為 。若共模輸入電壓進一步增大,PMOS輸入對截止,電流開關(guān)使得 通過電流鏡全部注入到NMOS輸入對。從而使 在整個共模輸入范圍內(nèi)保持恒定。但由式(2)可知, 還與弱反型傾斜因子n有關(guān)。若NMOS與PMOS輸入對的弱反型斜率因子不等,仍會引起 的變化,可通過改變電流鏡的增益系數(shù)來得到補償。

由于電流開關(guān)和電流鏡所占面積相對較小,該 控制電路幾乎不會增加輸入管的尺寸大小,因此電路芯片面積小、功耗低,非常滿足IP核設(shè)計的要求。還有另一個優(yōu)點是不會增加輸入級的噪聲,因為在gm控制電路中生成的噪聲夾雜在互補輸入對的尾電流中,可認為是共模信號。對Rail-to-Rail輸入級來說,若輸入管匹配,gm控制電路所產(chǎn)生的噪聲就可以忽略掉。

2.2 Rail-to-Rail輸出級及共柵補償技術(shù)

在Rail-to-Rail輸出級中,AB 類傳輸函數(shù)可通過保持輸出管柵極間電壓恒定來實現(xiàn)。采用帶有前饋AB類控制的推挽輸出結(jié)構(gòu),它能夠在低壓下實現(xiàn)全擺幅的輸出,并 且可以在保證低失真的情況下,得到較高的電源效率。

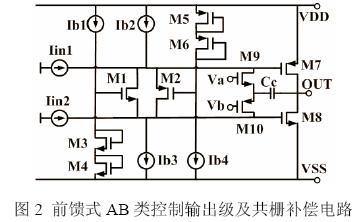

用晶體管耦合直接前饋通路實現(xiàn)的AB 類前饋式輸出級如圖2 所示。M7、M8為Rail-to-Rail 輸出管,M1、M2 組成晶體管耦合的AB 類控制電路。Iin1和Iin2為同相位的小信號電流源。電路中的兩個回路M2-M7 和M1-M8控制輸出管的靜態(tài)電流。當(dāng)一個輸出管電流非常大時,另一個輸出管能夠保持一個最小值,而不是截止為零,避免了從截止到導(dǎo)通所需要的時間延遲,也減少了交越失真。

通常Rail-to-Rail運放是多級放大器,需要兩個(或兩個以上) 電容作為Miller 補償以提供足夠的相位裕度,這不僅會占用大量的面積,也限制了單位增益帶寬;而且多級放大器作為輸出緩沖器時,電路的穩(wěn)定性還容易隨負載電容大小的變化而改變,產(chǎn)生震蕩。Miller補償要求在M23 和M24 柵漏兩端分別接入兩個補償電容,其輸出極點可簡單的表示為(假設(shè)gm7等于gm8, CL 是負載電容) :

由于電容的前饋通路,Miller 補償引入了一個右半平面零點zc,該零點減小了相位裕度,同時也限制了單位增益帶寬。

如圖2所示,針對特殊的AB類輸出級,采用M9,M10和電容CC組成的共柵頻率補償結(jié)構(gòu),可以阻止通過電容的前饋電流,并將右半平面零點移至高頻,同時也減少了一個補償電容,節(jié)省了芯片面積。假設(shè)只考慮晶體管M8 所構(gòu)成的NMOS 共源輸出級,通過小信號分析可以得到,該電路引入了一個位于左半平面的零點:

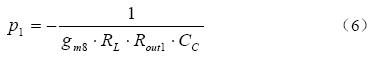

整個放大器主極點可以近似等于:

其中Rout1為第一級放大電路的輸出電阻,RL為負載電阻,對于較大的RL ,輸出極點可以近似為:

從式中看出,輸出極點增大了約gm10Rout1倍,增加M10 (和M9) 的跨導(dǎo)還可將此極點移至高頻,因此采用較小CC就能實現(xiàn)頻率補償,獲得較高的單位增益帶寬。但是,增加gm9, gm10將會導(dǎo)致M9 和M10 的漏電流增加,從而減少流經(jīng)M1 和M2 的電流,進一步減小M1和M2的源漏端的飽和壓降Vdsat,而流經(jīng)M7和M8的電流將增加,輸出阻抗減小,最終導(dǎo)致放大器開環(huán)增益的降低。此外,增大gm9 , gm10還會增加等效的輸入噪聲和放大器的功耗。因此M9、M10的設(shè)計只需使得兩個極點分離足以滿足穩(wěn)定性所需的相位裕度即可。流經(jīng)M9 和M10 的漏電流總是相等,M9和M10的引入并不會影響放大器總體的失配;同時(7)式也說明采用較小的補償電容CC 還可以減少負載電容CL 的增加對電路頻率特性的影響。

3整體電路實現(xiàn)與仿真

綜上所述,電路的整體實現(xiàn)結(jié)構(gòu)如圖3所示,由晶體管M18-M22構(gòu)成的電流鏡和由M28-M31構(gòu)成的電流鏡為整個電路提供偏置電流。為了減小輸入失調(diào),盡量增大輸入晶體管面積,減小其有效柵源電壓,同時盡可能減小電流鏡和電流源的寬長比。通過減小電流開關(guān)M15的寬長比將失調(diào)變化擴展到整個共模輸入范圍,可以增加共模抑制比。

電路采用TSMC 0.18μm 1P6M CMOS數(shù)模混合工藝,基于BSIM3V3 Spice模型,10pF電容負載的條件下,用Hspice對整個電路進行仿真,電源電壓為1.8V,偏置電壓為0.8V。

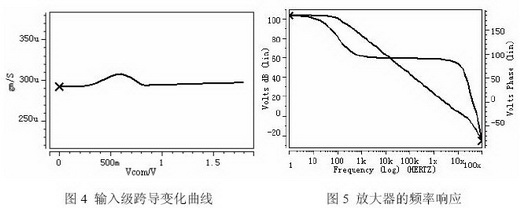

輸入級跨導(dǎo)隨輸入共模電壓變化的結(jié)果如圖4所示,可以看出,輸入級跨導(dǎo)大約為290μS,在整個輸入共模電壓范圍內(nèi)只變化3%,基本保持恒定。在0~0.4V,PMOS差分輸入對導(dǎo)通,NMOS差分輸入對截止,輸入級跨導(dǎo)為PMOS輸入對的跨導(dǎo);在0.9~1.8V,輸入級跨導(dǎo)為NMOS輸入對的跨導(dǎo);在0.4~0.9V,PMOS和NMOS差分輸入對同時導(dǎo)通,電流開關(guān)抽取電流會引起跨導(dǎo)變化,主要是由NMOS和PMOS差分輸入對的寬長比以及弱反型斜率因子的不同引起的。

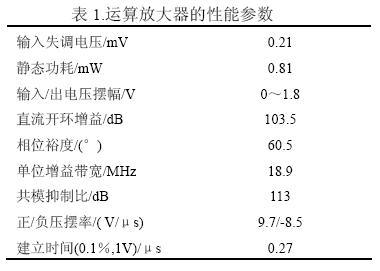

該運放的頻率特性如圖5所示,整個電路的直流開環(huán)增益為103.5dB,相位裕度為60.5度,單位增益帶寬為18.9MHz。相比之下,采用傳統(tǒng)miller補償其帶寬只有9.5MHz。

整個放大器的設(shè)計結(jié)果如下表所示,運算放大器的整體性能較好,并且能夠在1.8V低電壓下工作,功耗低,芯片面積也大大節(jié)省。

4結(jié)束語

隨著電源電壓的降低以及芯片集成度的增加, 以IP核形式的Rail to Rail運算放大器設(shè)計較有優(yōu)勢,它可以節(jié)省成本和縮短系統(tǒng)設(shè)計周期。本文基于0.18μm CMOS工藝設(shè)計了一個恒跨導(dǎo)Rail to Rail運算放大器,整個電路結(jié)構(gòu)簡單緊湊,功耗低,非常適合做成SOC的IP核。

本文作者創(chuàng)新點:

(1) 從IP核的角度進行運算放大器的設(shè)計,使其更具有應(yīng)用價值。

(2) 采用一倍電流鏡方式進行跨導(dǎo)控制,和新型的共柵頻率補償技術(shù),使整個電路結(jié)構(gòu)簡單緊湊,適合與其它電路模塊集成應(yīng)用于SOC。

參考文獻:

[1] Trung K N, Sang G L. Low-voltage, low-power CMOS operation transconductance amplifier with Rail-to-Rail differential input range [J]. IEEE ISCAS. 2006; 10:1639-1642

[2] 候衛(wèi)衛(wèi),馮全源.一種高性能單位增益放大器[J].微計算機信息,2007;2-2:291-293

[3] Juan. M. Carrillo, Francisco J, Duque-carrillo, et al. Constant-gm constant-slew-rate high-bandwidth low-voltage Rail-to-Rail CMOS input stage for VLSI cell libraries [J]. IEEE International Symposium on Circuits and Systems, 2003; 38(1): 165-168

[4] Loikkanen M, Kostamovaara J. Low voltage CMOS power amplifier with rail-to-rail input and output [J]. Analog Integral Circuits Process, 2006, 46(2) :183

[5] 王為之,靳東明. 一種采用共柵頻率補償?shù)能壍杰壿斎?輸出放大器[J]. 半導(dǎo)體學(xué)報,2006;27(11):2026-2028

[6] 楊銀堂,李曉娟,朱樟明等. 低壓低功耗運算放大器結(jié)構(gòu)設(shè)計技術(shù)[J]. 電路與系統(tǒng)學(xué)報,2005;10(4):95-101