圖 10.54 中的瞬態(tài)穩(wěn)定性測(cè)試結(jié)果同時(shí)與 Aol 曲線上的 1/b值和環(huán)路增益曲線一致,因此,證明了只采用 FB#1 構(gòu)建參考緩沖電路,將導(dǎo)致電路運(yùn)行的不穩(wěn)定性。

圖 10.54 FB#1 瞬態(tài)穩(wěn)定性測(cè)試:CMOS RRO

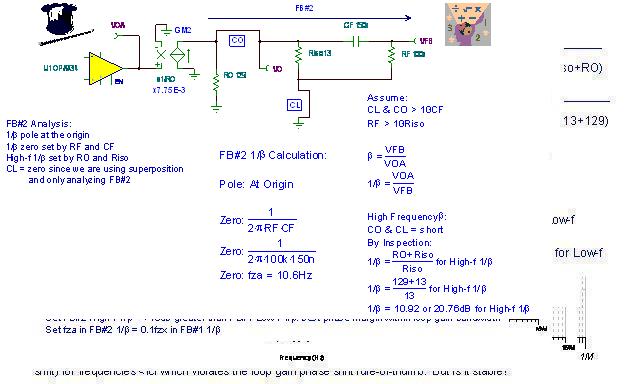

現(xiàn)在,我們必須弄清楚如何合成一種解決方案,以保證設(shè)置電容性負(fù)載參考緩沖電路的穩(wěn)定性。此時(shí),我們進(jìn)一步了解如圖 10.55 所示的 Aol 曲線和 FB#1 1/b曲線。如果我們添加圖?10.55 所示的 FB#2 1/b曲線,我們就會(huì)看到一條最終的?1/b曲線,這樣,根據(jù)?fcl 處的接近速率在歷史上的穩(wěn)定性經(jīng)驗(yàn),可以推斷電路的運(yùn)行也將是穩(wěn)定的。

另外,我們將促使 fpc 低于 1/b曲線中的?fzx 一個(gè) decade,以確保當(dāng)頻率低于 fcl 時(shí),相位裕度優(yōu)于45度。上述工作通過(guò)調(diào)整 1/b FB#2 的高頻部分,使其比 FB#1 低頻 1/b高出?+10dB。接著,設(shè)置 fza,使其至少低于 fpc 一個(gè) decade,以確保當(dāng)實(shí)際應(yīng)用中進(jìn)行參數(shù)變化時(shí),

能夠避免 BIG NOT。通過(guò)觀察,我們發(fā)現(xiàn),最終的?1/b曲線是在?FB#1 1/b曲線和 FB#2 1/b曲線中選擇最小數(shù)值的?1/b通道而形成的。

務(wù)必請(qǐng)記住,在雙反饋通道中,從運(yùn)算放大器輸出端至負(fù)極輸入端的最大電壓反饋將主導(dǎo)著整個(gè)反饋電路。最大的反饋電壓意味著b值最大或者是?1/b值最小。

最后,在 FB#2 取得支配地位之前,預(yù)計(jì) Vout/Vin 的傳輸函數(shù)將隨著 FB#1 的變化而變化。此時(shí),Vout/Vin 將會(huì)衰減至 –20dB/decade,直至 FB#2 與 Aol 曲線相交,然后,將隨著 Aol 曲線下降。

圖 10.55 FB#2 圖解分析:CMOS RRO

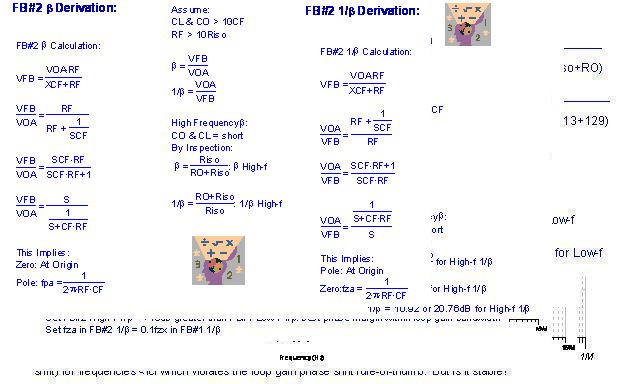

如圖 10.56 所示,里面有一些主要的假設(shè)。我們將這些假設(shè)運(yùn)用于幾乎所有的具有雙通道反饋的 RISO 電路中。首先,我們假設(shè) CL>10* CF,這也就是說(shuō),在高頻率時(shí),CL 早在 CF 短路之前就短路。因此,我們將短路 CL 以排除 FB#1,從而便于單獨(dú)分析 FB#2。另外,我們假設(shè) RF>10*Riso,這意味著作為 Riso 的負(fù)載,該 RF 幾乎完全失效。從圖 10.56 和圖 10.57 中具體的公式推導(dǎo),我們可以看出,當(dāng) zero, fza = 19.41Hz(由 RF 和 CF 產(chǎn)生)時(shí),F(xiàn)B#2 在原點(diǎn)擁有一個(gè)極點(diǎn)。由于在高頻時(shí),CF 和 CL 同時(shí)處于短路狀態(tài),所以 FB#2 高頻 1/b部分即為 Ro+Riso 與 Riso 之間的比值。FB#2 1/b的公式推導(dǎo)請(qǐng)參閱下一張圖(圖10.57),有關(guān)計(jì)算結(jié)果請(qǐng)參閱下圖。FB#2 高頻 1/b設(shè)置為?10.92dB 或 20.76dB、原點(diǎn)擁有一個(gè)極點(diǎn)以及當(dāng)頻率為 10.6Hz 時(shí)的零點(diǎn)。

圖 10.56 FB#2 分析:CMOS RRO

FB#2b的公式推導(dǎo)如圖 10.57左側(cè)所示。由于 1/b是b的倒數(shù),所以?FB#1 1/b的計(jì)算結(jié)果可以輕而易舉的推導(dǎo)出來(lái),具體推導(dǎo)過(guò)程請(qǐng)參閱圖?10.57 右側(cè)。從圖中我們還發(fā)現(xiàn),在b推導(dǎo)過(guò)程中的?pole, fpa 變成了 1/b推導(dǎo)過(guò)程中的?zero, fza。

圖 10.57 FB#2 分析:CMOS RRO

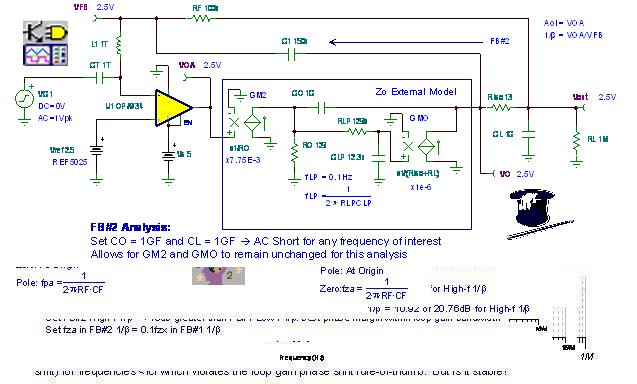

為了檢驗(yàn) FB#2 一階分析情況,我們可采用如圖 10.58 所示的 Tina SPICE 電路。而且,為了便于分析,我們將 CL 設(shè)置為 10GF,因此對(duì)各種相關(guān)的頻率而言,CL 都等同于短路狀態(tài)。但是,在開(kāi)展 AC 分析前,仍允許 SPICE 查找到相應(yīng)的 DC 工作點(diǎn)。

圖 10.58 FB#2 AC 電路分析:CMOS RRO

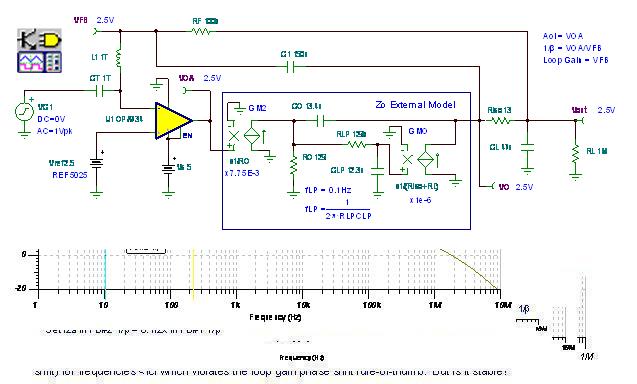

Tina SPICE 仿真結(jié)果如圖 10.59 所示。FB#2 1/b曲線正如當(dāng)?fza= 10.6Hz 以及高頻 1/b= 23.78dB 時(shí),采用一階分析推算出來(lái)的結(jié)果一樣。另外,我們也繪制出 OPA734 Aol 曲線,以弄清楚在高頻時(shí),F(xiàn)B#2 將如何與其相交。

圖 10.59 FB#2 1/b曲線:CMOS RRO

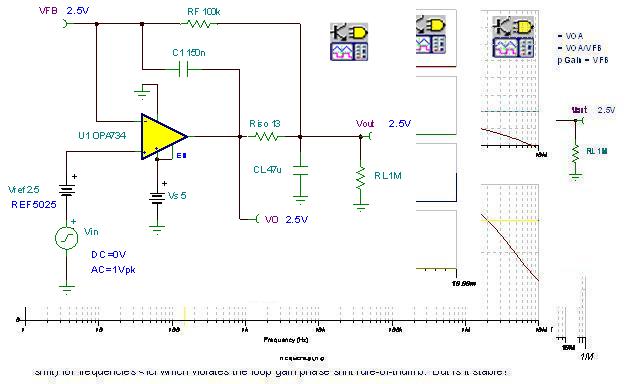

如果推算的 FB#1 和 FB#2 疊加結(jié)果會(huì)產(chǎn)生所需的最終 1/b曲線,那么我們將通過(guò)如圖?10.60 所示的?Tina SPICE 電路開(kāi)展分析工作。同時(shí),我們還可通過(guò) Tina SPICE 電路,繪制出 Aol 曲線、最終的 1/b曲線以及環(huán)路增益曲線。

圖 10.60 最終環(huán)路增益分析電路:CMOS RRO

從圖 10.61 中,我們可以看出,分析結(jié)果驗(yàn)證了我們所推算的最終 1/b曲線。在環(huán)路增益為零的?fcl 處,推算的接近速率為 20dB/decade。

圖 10.61 最終的 1/b曲線:CMOS RRO

最終電路的環(huán)路增益相位曲線(采用 FB#1 和 FB#2)如圖 10.62 所示。相移從未下降至 66.54 度以下(出現(xiàn)在頻率為 146.43kHz 的地方),因?yàn)椋?fcl 處(頻率為 172.64kHz),相位裕度為 87.79 度。

圖 10.62 最終環(huán)路增益分析:CMOS RRO

我們將采用圖 10.63 中的 Tina SPICE 電路對(duì)我們的穩(wěn)定電路進(jìn)行最后的檢驗(yàn)——瞬態(tài)穩(wěn)定性測(cè)試。

圖 10.63 最終瞬態(tài)穩(wěn)定性測(cè)試電路:CMOS RRO

圖 10.64 中最終電路瞬態(tài)穩(wěn)定性的測(cè)試結(jié)果符合我們其他所有的推算結(jié)果,從而研制出一款性能優(yōu)良、運(yùn)行

穩(wěn)定的電路。而且,我們可以信心十足的將這種電路投入量產(chǎn),因?yàn)樗粫?huì)發(fā)生故障或在實(shí)際運(yùn)行中出現(xiàn)異常。

圖 10.64 最終瞬態(tài)穩(wěn)定性測(cè)試電路:CMOS RRO

通過(guò)圖 10.65 中的 Tina SPICE 電路,可驗(yàn)證我們對(duì) Vout/Vin 的推算是否正確。

圖 10.65 最終 Vout/Vin 傳輸函數(shù)電路:CMOS RRO

從圖 10.66 中,我們可以看出,Vout/Vin 的測(cè)試結(jié)果與我們推算的一階分析結(jié)果一致,具體表現(xiàn)為:當(dāng)頻率為 253.88Hz 時(shí),單極點(diǎn)開(kāi)始下降。而且,當(dāng)頻率約為 167kHz(此時(shí),F(xiàn)B#2 與 OPA734 Aol 曲線相交)時(shí),出現(xiàn)第二個(gè)極點(diǎn)。

圖 10.66 最終 Vout/Vin 傳輸函數(shù):CMOS RRO

圖 10.67 總結(jié)了一種易于使用的漸進(jìn)式程序。這種程序輕松地將具有雙通道反饋的 RISO 電容性負(fù)載穩(wěn)定性技術(shù)應(yīng)用于 CMOS RRO 輸出運(yùn)算放大器上。

1)測(cè)量運(yùn)算放大器的 Aol

2)測(cè)量運(yùn)算放大器的 Zo,并在圖上繪制出其曲線

3)確定 CO 和 RO

4)創(chuàng)建 Zo 的外部模型

5)計(jì)算 FB#1 低頻 1/b(由 CO 和 CL 導(dǎo)致)

6)將 FB#2 高頻 1/b 設(shè)置為比 FB#1 低頻 1/b 高 +10dB(為獲得最佳的 Vout/Vin 瞬態(tài)響應(yīng)和實(shí)現(xiàn)環(huán)路增益帶寬內(nèi)相移量最少)

7)從 FB#2 高頻 1/b 中選擇 Riso 以及 RO

8)從 CO、CL、Riso 和 RO 中,計(jì)算 FB#1 1/b fzx

9)設(shè)置 FB#2 1/b fza = 1/10 fzx

10)選擇具有實(shí)際值的 RF 和 CF,以產(chǎn)生 fza

11)采用 Aol、1/b、環(huán)路增益、Vout/Vin 以及瞬態(tài)分析的最終值,運(yùn)行仿真以驗(yàn)證設(shè)計(jì)的可行性。

12)核實(shí)環(huán)路增益相移的下降不得超過(guò) 135 度(>45 度相位裕度)

13)針對(duì)低噪聲應(yīng)用:檢查 Vout/Vin 扁平響應(yīng),以避免增益驟增àVout/Vi 中的噪聲陡升

圖 10.67 具有雙通道反饋的 RISO 補(bǔ)償程序:CMOS RRO

作者簡(jiǎn)介

Tim Green 現(xiàn)任美國(guó)亞利桑那州圖森市 TI 線性應(yīng)用工程經(jīng)理。他擔(dān)任模擬與混合信號(hào)電路板/系統(tǒng)級(jí)設(shè)計(jì)工程師長(zhǎng)達(dá) 24 年之久,其中包括:無(wú)刷馬達(dá)控制、飛機(jī)噴氣式發(fā)動(dòng)機(jī)、導(dǎo)彈系統(tǒng)、功率運(yùn)算放大器、數(shù)據(jù)采集系統(tǒng)以及 CCD 相機(jī)。Tim 最近的工作經(jīng)驗(yàn)包括模擬與混合信號(hào)半導(dǎo)體戰(zhàn)略營(yíng)銷。Tim 畢業(yè)于亞利桑那大學(xué) (University of Arizona),獲電子工程理學(xué)士學(xué)位。如欲聯(lián)系作者,請(qǐng)發(fā)送郵件至 [email protected]。