1 引言

嵌入式系統(tǒng)的終端顯示傾向選擇LCD顯示器。但在大屏幕顯示情況下,大型工業(yè)級LCD液品顯示器造價(jià)高。選擇性少。而為嵌入式系統(tǒng)增加標(biāo)準(zhǔn)VGA接口可很好地解決該問題。支持VGA接口的顯示設(shè)備眾多且價(jià)格相對較低,而且顯示設(shè)備的更換不會(huì)對嵌入式系統(tǒng)產(chǎn)生影響。ARM9器件S3C2410在嵌入式系統(tǒng)中應(yīng)用廣泛。這里主要針對該處理器介紹基于CH7004的嵌入式系統(tǒng)VGA接口設(shè)計(jì)。該設(shè)計(jì)方案硬件設(shè)計(jì)和軟件實(shí)現(xiàn)簡單,成本較低,從而為嵌入式設(shè)備提供了簡單有效的大屏幕圖像顯示解決方案。

2 VGA接口

VGA(Video Graphics Array)是一個(gè)模擬信號接口,是IBM公司推出的一種視頻傳輸標(biāo)準(zhǔn)。該接口具有分辨率高、顯示速率快、顏色豐富等優(yōu)點(diǎn),在彩色顯示器領(lǐng)域得到了廣泛的應(yīng)用。

(1)VGA接口引腳表1為15針VGA接口引腳信號的定義列表。

(2)VGA接口時(shí)序VGA接口有多種時(shí)序,應(yīng)用時(shí)根據(jù)具體需要選擇不同的時(shí)序。圖1為640×480在60 Hz模式下的VGA接口時(shí)序圖。

3 器件介紹

3.1 LCD控制器簡介

S3C2410處理器采用16/32位指令的 ARM920T內(nèi)核,最高工作頻率為202 MHz,內(nèi)部帶有豐富的外設(shè)資源,低功耗、低價(jià)格、高性能的特點(diǎn)使其在嵌入式系統(tǒng)中應(yīng)用廣泛。LCD控制器是S3C2410內(nèi)部集成外設(shè),具有以下特點(diǎn):支持STN、TFT兩種類型液晶顯示屏;支持多種顏色模式,最高支持24位顏色模式;LCD控制時(shí)序可由用戶根據(jù)實(shí)際情況需要設(shè)置。

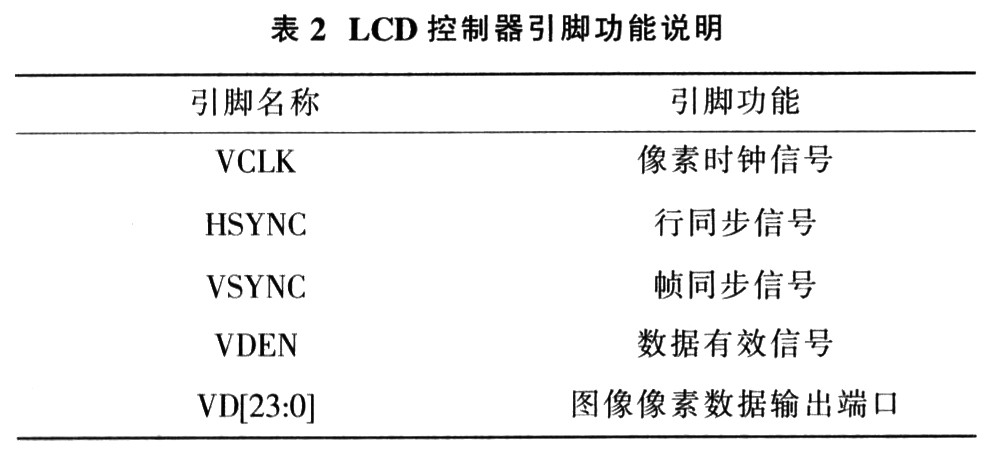

3.1.1 LCD控制器引腳功能

LCD控制器引腳分為時(shí)序控制端口和數(shù)據(jù)端口。與該設(shè)計(jì)相關(guān)的端口具體含義見表2。

3.1.2 LCD控制器內(nèi)部控制寄存器

LCD控制器內(nèi)部有5個(gè)控制寄存器:LCDCON1~LCD-CON5。LCDCON1控制像素時(shí)鐘、掃描模式和顏色模式;LCDCON2控制幀同步脈沖寬度、幀有效行數(shù)及幀同步前、后的無效行數(shù):LCDCON3主要控制行有效像素點(diǎn)數(shù)以及行同步前、后的無效像素點(diǎn)數(shù):LCDCON4主要控制行同步脈沖寬度:LCDCON5主要控制行、場同步脈沖和數(shù)據(jù)有效信號極性,16位色顏色格式.?dāng)?shù)據(jù)輸出與像素時(shí)鐘跳變關(guān)系。

3.2 CH7004器件簡介

CH7004是Chrontel公司生產(chǎn)的一款數(shù)字轉(zhuǎn)換為模擬的視頻編碼器,其內(nèi)部編碼器支持NSTL、PAL兩種視頻制式,通用數(shù)字輸入接口支持8、 12、15、16和24位數(shù)字RGB或者YCrCb格式輸入,支持5種圖像分辨率,內(nèi)部集成3路相互獨(dú)立的高速視頻數(shù)模轉(zhuǎn)換器,可由用戶控制輸出模擬 RGB或YUV,提供I2C接口供用戶控制器件工作模式。

4 VGA接口設(shè)計(jì)

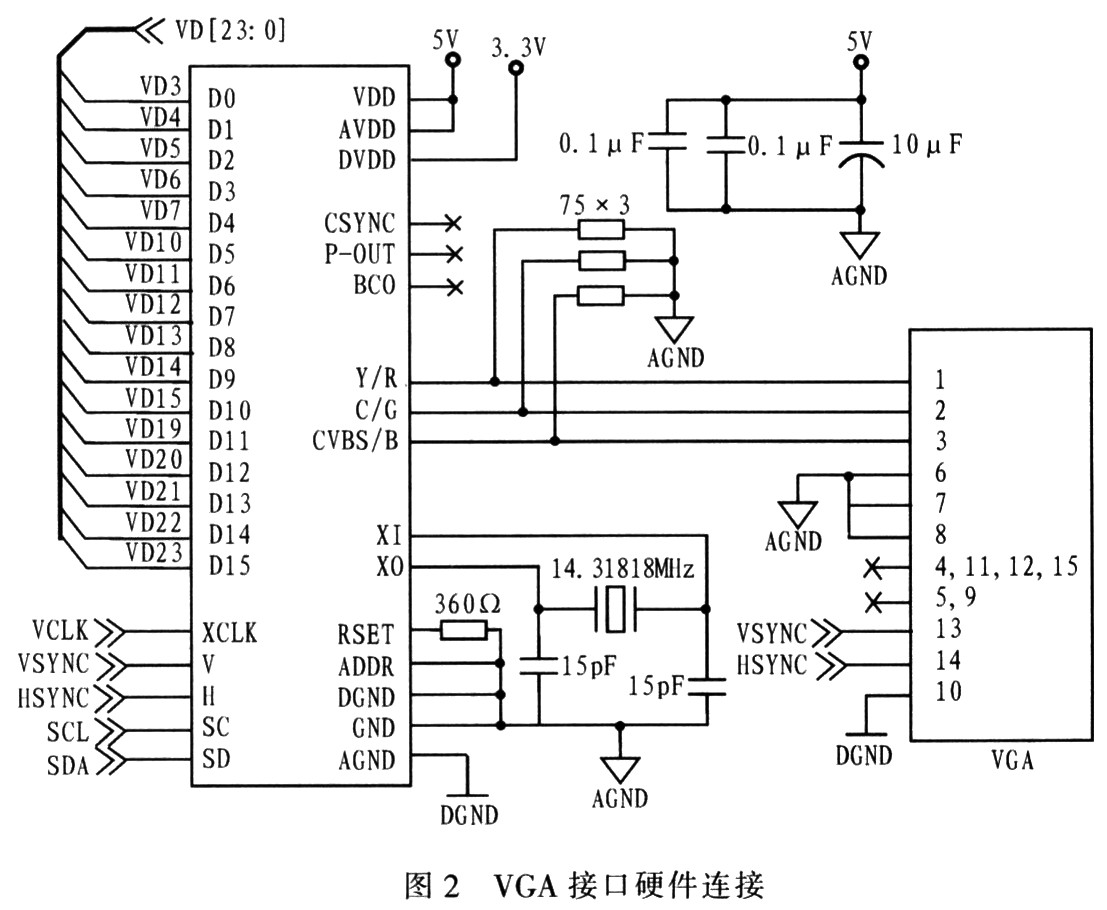

S3C2410處理器的LCD控制器用于產(chǎn)生圖像數(shù)據(jù)、VGA接口時(shí)序(640x480,60 Hz)以及配置CH7004的工作模式。CH7004將數(shù)字圖像數(shù)據(jù)模擬化,最終產(chǎn)生的模擬圖像信號供支持VGA接口的顯示器顯示。VGA接口的硬件連接見圖2。

這里選擇(640x480,60 Hz)模式,是由實(shí)際需要和硬件特性決定的:(1)嵌入式系統(tǒng)中的圖像尺寸大多低于640x480,采用這種VGA模式顯示不會(huì)丟失任何原始圖像信息; (2)VGA的每種顯示模式所要求的像素時(shí)鐘不同,而S3C2410內(nèi)部LCD控制的像素時(shí)鐘由器件的主頻分頻而來,在各種分頻后的像素時(shí)鐘里只有25. 25 MHz(202 MHz主頻進(jìn)行8分頻)與VGA模式中的(640x480,60 Hz)模式所要求的像素時(shí)鐘25.175 MHz最為接近,微小的像素時(shí)鐘偏差不會(huì)影響VGA接口顯示;(3)16位色情況下,(640x480,60 Hz)模式數(shù)據(jù)流帶寬為35.2 MB/s,因而不會(huì)堵塞S3C2410數(shù)據(jù)總線,不影響處理器的其他控制、數(shù)據(jù)處理操作。

CH7004的數(shù)據(jù)輸入端口D0~D15與LCD控制器的相應(yīng)數(shù)據(jù)輸出端口連接,LCD控制器的像素時(shí)鐘VCLK通過XCLK端輸入CH7004內(nèi)部, ADDR為低設(shè)置CH7004的I2C總線地址,為0x76。CH7004輸出端需考慮視頻信號阻抗匹配問題,否則會(huì)出現(xiàn)圖像重影、雪花、或邊緣有波紋等問題。

5 LCD控制器和CH7004配置

5.1 LCD控制器的設(shè)置流程

將LCD控制器工作模式設(shè)置為(640x480,60 Hz),16位色(5:6:5),TFT模式。

(1)將系統(tǒng)主時(shí)鐘(FCLK)設(shè)置為202 MHz,外設(shè)時(shí)鐘(HCLK)設(shè)置為101 MHz;

(2)將LCD控制器外部端口設(shè)置為TFT作模式;

(3)開辟1塊大小為600 KB(640x480x2 Bytes)用于存放數(shù)據(jù)的連續(xù)內(nèi)存區(qū)域;

(4)設(shè)置LCD控制器的控制邏輯寄存器LCDCON1~LCD-CON5。其中,LCDCON1:設(shè)置像素時(shí)鐘(VCLK)從系統(tǒng)主頻分頻的分頻系數(shù) CLKVAL=1,VM的觸發(fā)速率為每幀觸發(fā),顯示模式TFT,單像素顏色位數(shù)16位.禁止LCD控制器數(shù)據(jù)輸出和控制信號產(chǎn)生ENVID=0; LCDCON2:設(shè)置幀同步后無效行數(shù)VBPD=32,幀有效行數(shù)LINEVAL=469;幀同步前無效行數(shù)VFPD=9,幀同步寬度VSPW=1; LCDCON3:行同步后無效像素點(diǎn)數(shù)HBPD=47,行有效像素點(diǎn)數(shù)HOZVAL=639,行同步前無效像素點(diǎn)數(shù)HFPD=15;LCDCON4:行同步寬度HSPW=95;LCDCON5:圖像在內(nèi)存的存儲(chǔ)方式設(shè)置為小端存儲(chǔ)BPP24BL=0.16位色圖像為5:6:5格式FRM=1,像素時(shí)鐘 VCLK設(shè)置為上升沿傳輸一個(gè)像素?cái)?shù)據(jù),行同步脈沖設(shè)置為負(fù)脈沖有效INVVUNE=1,幀同步脈沖設(shè)置為負(fù)脈沖有效IN-VFRAME=1,LEND信號極性設(shè)置正常模式INVLEND=0,PWREN信號設(shè)置有效設(shè)置PWREN=1,LEND信號輸出為允許ENLEND=1。

(5)允許視頻數(shù)據(jù)輸出和時(shí)序控制ENVID=1。

5.2 CH7004工作模式配置

CH7004C內(nèi)部有25個(gè)工作模式控制寄存器。與此設(shè)計(jì)模式相關(guān)的寄存器有4個(gè):顯示模式寄存器(Display Mode),輸入數(shù)據(jù)模式寄存器(Input Data Format),時(shí)鐘模式寄存器(Clock Mode),同步信號極性寄存器(Sync Polarity)。通過配置CH7004內(nèi)部工作模式控制寄存器的使CH7004與LCD控制器工作相對應(yīng)。

將CH7004 工作模式設(shè)置為與國LCD控制器相一致。圖像大小為640x480,輸入數(shù)據(jù)為16位5:6:5格式.?dāng)?shù)據(jù)不經(jīng)制式編碼器而直接送人內(nèi)部D/A轉(zhuǎn)換器。對 CH7004的配置順序?yàn)椋?1)Display Mode寄存器設(shè)置640x480顯示模式,可選擇的模式為13~17。(2)Input Data Format寄存器設(shè)置為16位色。RGB5:6:5格式,RGB信號旁路。選擇旁路模式使得RGB輸入圖像信號不經(jīng)視頻編碼器而直接送入D/A轉(zhuǎn)換器。 (3)Clock Mode寄存器設(shè)置為像素時(shí)鐘上升沿鎖存圖像信號。(4)Sync Polarity寄存器設(shè)置行、場同步負(fù)脈沖有效,行、場同步信號由外部處理器產(chǎn)生并南CH7004的V、H端口輸入。在實(shí)際操作中,系統(tǒng)上電后,處理器只需配置CH7004內(nèi)部的輸入數(shù)據(jù)模式(Input Data Format)寄存器,其他寄存器直接使用復(fù)位默認(rèn)值。

5.3 CH7004的I2C總線配置時(shí)序

S3C241O配置CH7004的I2C總線的步驟:(1)在I2C總線上首先產(chǎn)生CH7004片選地址0x76和讀寫位(0:寫;1:讀);(2)產(chǎn)生某一寄存器的片內(nèi)偏移地址;(3)產(chǎn)生配置數(shù)據(jù)。PC控制器一個(gè)操作步驟結(jié)束后,必須等獲得CH7004發(fā)出正確操作答復(fù),才能繼續(xù)執(zhí)行下一步操作。圖3 為CH7004的I2C讀寫時(shí)序圖。

6 測試與結(jié)論

實(shí)驗(yàn)證明.色條圖像通過VGA接口在顯示器上顯示效果良好。介紹的VGA接口設(shè)計(jì)方法使用S3C2410處理器和CH7004視頻編碼器件,具有硬件設(shè)計(jì)、軟件實(shí)現(xiàn)簡單,價(jià)格低廉的特點(diǎn)。為嵌入式設(shè)備提供了簡單有效的大屏幕圖像顯示解決方案。