0 引 言

傳統(tǒng)氣體壓力測(cè)量?jī)x器的傳感器部分與數(shù)據(jù)采集系統(tǒng)是分離的,抗干擾的能力較差,,并且通常被測(cè)對(duì)象的壓力變化較快,。因此不僅要求系統(tǒng)具有較快的數(shù)據(jù)吞吐速率,而且要能夠適應(yīng)復(fù)雜多變的工業(yè)環(huán)境,,具有較好抗干擾性能,、自我檢測(cè)和數(shù)據(jù)傳輸?shù)墓δ堋?br />

在此,利用FPGA具有擴(kuò)展靈活,,可實(shí)現(xiàn)片上系統(tǒng)(SoC),,同時(shí)具有多種IP核可供使用等優(yōu)點(diǎn),設(shè)計(jì)了能夠控制多路模擬開(kāi)關(guān),、A/D轉(zhuǎn)換,、快速數(shù)據(jù)處理與傳輸、誤差校正,、溫度補(bǔ)償?shù)闹悄軅鞲衅飨到y(tǒng),;同時(shí)將傳感器與數(shù)據(jù)采集處理控制系統(tǒng)集成在一起,使系統(tǒng)更加緊湊,,提高了系統(tǒng)適應(yīng)工業(yè)現(xiàn)場(chǎng)的能力,。

1 系統(tǒng)性能及元器件

1.1 智能傳感器系統(tǒng)性能要求

傳感器壓力測(cè)量范圍:0~5 MPa;系統(tǒng)精度:±0.1%FS,;1通道模擬電壓輸入(壓力信號(hào))大于250 sampies/通道/s,;采用串行RS 232C接口輸出。

1.2 系統(tǒng)主要元器件及性能

根據(jù)系統(tǒng)的精度指標(biāo)的要求選擇器件:

FPGA芯片 選用Altera的CycloneⅡEP2C5,,其邏輯單元有4 608個(gè)LE,,26個(gè)M4K RAM塊,142個(gè)用戶I/O引腳,。

壓力傳感器 采用PDCR130W,,壓力范圍0~7 MPa,工作電壓直流10~30 VDC,,輸出0~10 V,,精度±0.05%FS,使用溫度范圍-40~+125℃,,溫度影響±0.015%FS/℃,。

溫度傳感器 采用高精度集成溫度傳感器LM335,其靈敏度為10 mV/K,精度為1℃,,溫度范圍-40~+100℃,。

A/D轉(zhuǎn)換器 選擇內(nèi)含采樣保持器的12位A/D轉(zhuǎn)換器AD1674,其轉(zhuǎn)換時(shí)間為10 μs,,0~10 V單極輸入或±5 V雙極輸入,,可并行12位輸出。

多路模擬開(kāi)關(guān) 采用四選一多路模擬開(kāi)關(guān)AD7502,,其引腳設(shè)置為EN=1的使能信號(hào),;A1A0引腳為通道選擇信號(hào)。

輸出電平轉(zhuǎn)換接口 系統(tǒng)使用MAX232芯片完成TTL和RS 232C電平的轉(zhuǎn)換,。

2 系統(tǒng)誤差校正方法

2.1 零點(diǎn)漂移和增益誤差的校正方法

在智能儀表中,,誤差模型的誤差校正公式為:

![]()

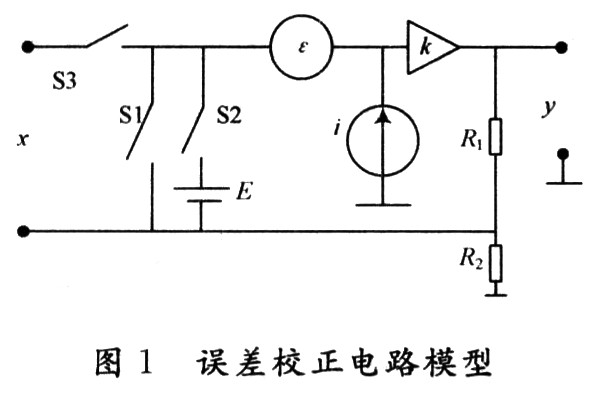

式中:b1和b0為誤差校正因子。誤差校正電路模型如圖1所示,,其中x為被測(cè)信號(hào),;y為系統(tǒng)輸出;ε,,k,,i為影響系統(tǒng)的未知量。

誤差校正過(guò)程為:

當(dāng)S1閉合時(shí),,x=0,,依據(jù)誤差校正公式得到式(2),用于系統(tǒng)零點(diǎn)校準(zhǔn),;

![]()

當(dāng)S2閉合時(shí),x=E(標(biāo)準(zhǔn)電壓),,得到公式(3),,用于系統(tǒng)增益誤差校正;

![]()

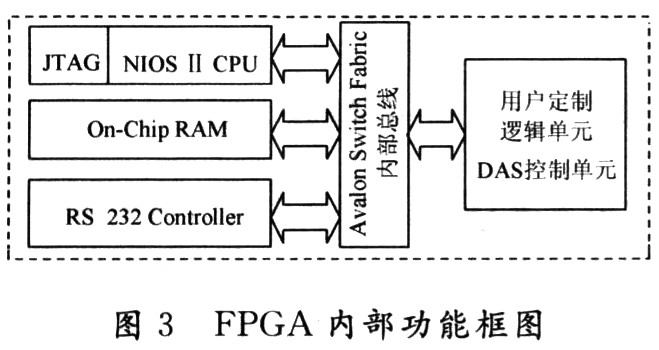

聯(lián)立式(2),、式(3)可得誤差校正因子:

當(dāng)進(jìn)行實(shí)際測(cè)量時(shí)S3閉合,,利用計(jì)算出的誤差校正因子和誤差校正公式(1),即可求出校正后的輸出信號(hào)y,。

2.2 傳感器溫度補(bǔ)償方法

對(duì)壓力傳感器來(lái)說(shuō),,環(huán)境溫度對(duì)其測(cè)量結(jié)果有較大的影響,為了消除溫度引起的誤差,,需要對(duì)傳感器的信號(hào)做溫度補(bǔ)償,。通過(guò)測(cè)量傳感器的工作溫度實(shí)現(xiàn)傳感器溫度的補(bǔ)償。傳感器的溫度誤差校正模型為:

![]()

式中:y為測(cè)量值,;yc經(jīng)溫度補(bǔ)償后的測(cè)量值,;△φ為傳感器的實(shí)際工作溫度與標(biāo)準(zhǔn)測(cè)量溫度之差;a0為校正溫度變化引起的傳感器標(biāo)度變化系數(shù),a1為校正溫度引起的傳感器零位漂移變化系數(shù),,這兩個(gè)系數(shù)反映了傳感器的溫度特性,。

2.3 隨機(jī)誤差消除方法

系統(tǒng)采用算術(shù)平均的數(shù)字濾波方法消除系統(tǒng)的隨機(jī)誤差,通過(guò)連續(xù)N個(gè)采樣值取其算術(shù)平均值,,得數(shù)學(xué)表達(dá)式為:

適合用于對(duì)具有隨機(jī)干擾信號(hào)的濾波,。

3 系統(tǒng)硬件結(jié)構(gòu)設(shè)計(jì)

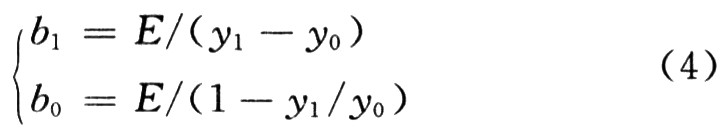

依據(jù)系統(tǒng)的誤差校正和溫度補(bǔ)償方法,可得系統(tǒng)的硬件連接結(jié)構(gòu)如圖2所示,。圖2中模擬多路開(kāi)關(guān)AD7502的4個(gè)輸入通道分別為:A1A0=00,,選通S0,S0通道接地,,用于零點(diǎn)漂移校準(zhǔn),;A1A0=01,選通S1,,S1通道接+5 V(為AD1674最大輸入電壓的50%),,用于增益誤差校正;A1A0=10,,選通S2,,S2通道接溫度測(cè)量信號(hào),用于傳感器的溫度補(bǔ)償,;A1A0=11,,選通S3,S3通道連接壓力測(cè)量信號(hào),。通道選通信號(hào)A0,,A1由FPGA芯片中的DAS_A0和DAS_A1引腳控制。

系統(tǒng)中A/D轉(zhuǎn)換器AD1674采用獨(dú)立工作模式,,其控制引腳設(shè)置為:CE和12/8接高電平,;CS和A0接低電平。此時(shí),,AD1674設(shè)置為12位A/D轉(zhuǎn)換,,12位數(shù)據(jù)輸出,其轉(zhuǎn)換完全由R/C控制,,如圖2所示,。當(dāng)R/C=O時(shí),啟動(dòng)12位A/D轉(zhuǎn)換,;當(dāng)A/D轉(zhuǎn)換結(jié)束時(shí),,狀態(tài)信號(hào)STS=0,否則STS=1,;當(dāng)R/C=1時(shí),,讀取12位A/D轉(zhuǎn)換數(shù)據(jù),。R/C信號(hào)由FPGA芯片的DAS_RC控制。整個(gè)系統(tǒng)由基于FPGA的片上系統(tǒng)(SoC)控制,。其中,,F(xiàn)PGA芯片中的DAS_STS,DAS_RC,,DAS_IN,,DAS_A引腳為用戶定制邏輯,即DAS控制單元的外部接口,,用于控制AD1674的工作時(shí)序轉(zhuǎn)換和AD7502的通道選擇,。

3.1 SoC結(jié)構(gòu)的實(shí)現(xiàn)

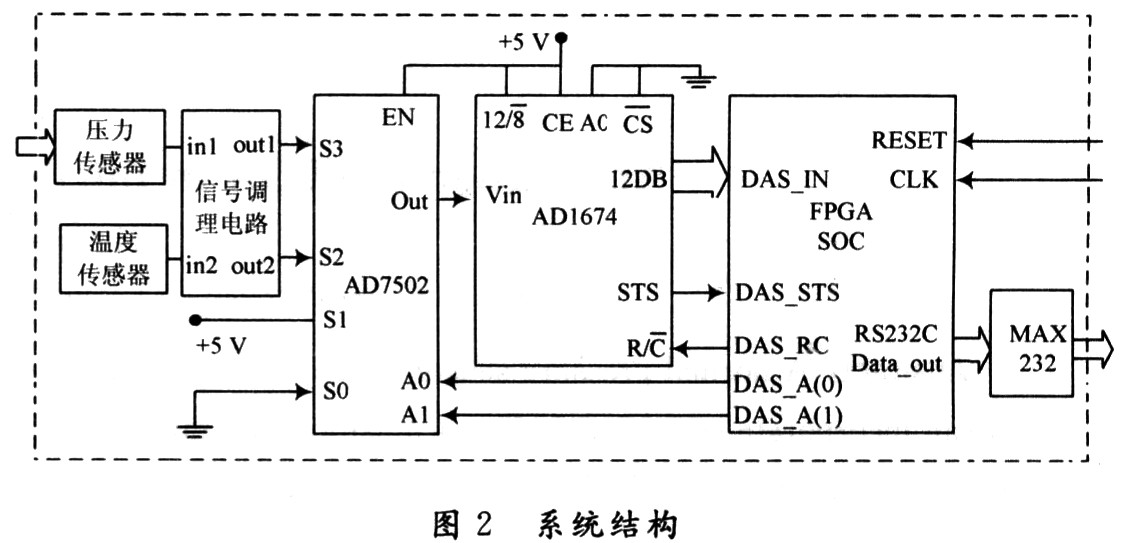

SoPC設(shè)計(jì)由CPU、存儲(chǔ)器接口,、標(biāo)準(zhǔn)外設(shè)和用戶定制邏輯單元模塊等組件構(gòu)成,。Altera的SoPCBuilder工具提供了大量IP核可供調(diào)用,可以很方便地在單片F(xiàn)PGA芯片上配置嵌入NoisⅡ處理器軟核,、片上RAM和RS 232控制器,、擴(kuò)展片外存儲(chǔ)器、用戶定制邏輯單元,,同時(shí)自動(dòng)地為系統(tǒng)的每個(gè)外設(shè)分配地址,、連接系統(tǒng)總線,確定設(shè)備優(yōu)先級(jí),,其內(nèi)部結(jié)構(gòu)如圖3所示,。

3.2 數(shù)據(jù)采集控制單元的實(shí)現(xiàn)

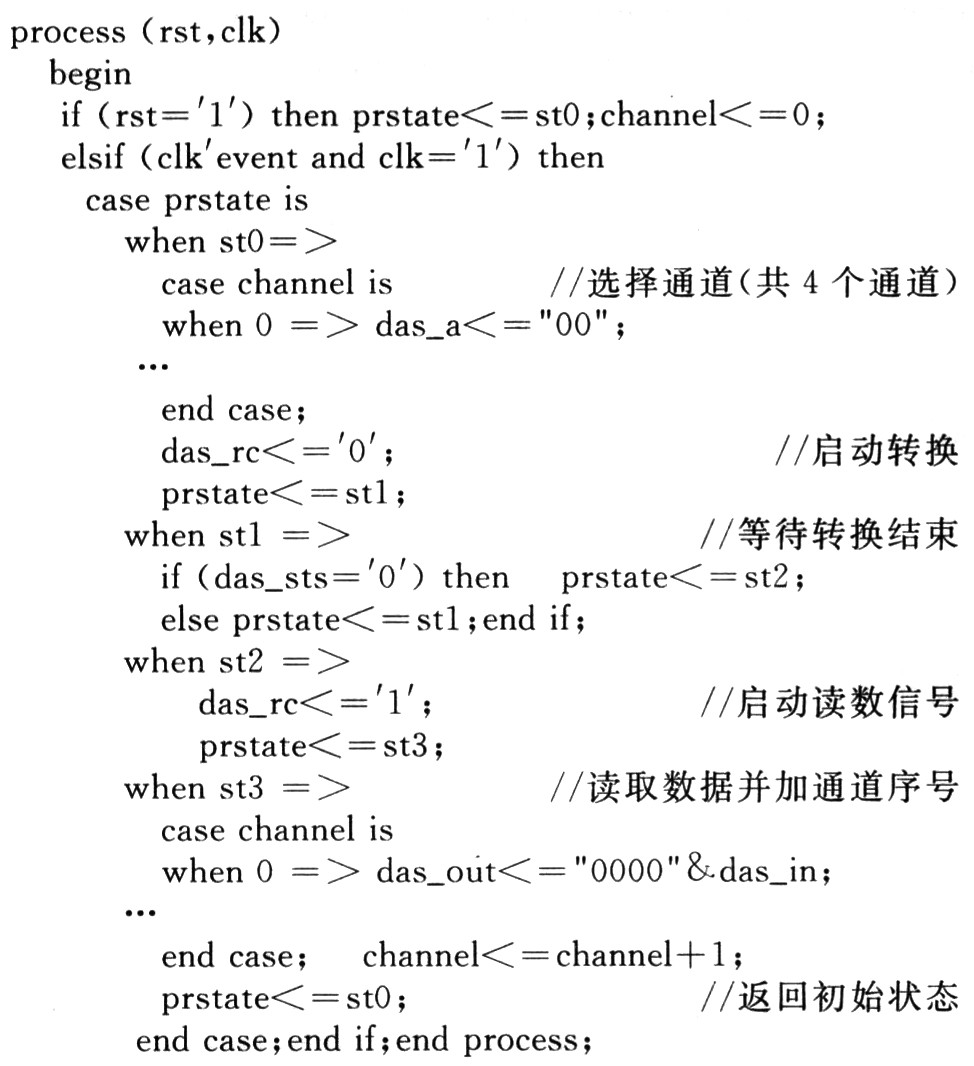

數(shù)據(jù)采集系統(tǒng)(DAS)控制單元是整個(gè)系統(tǒng)的核心,其輸入端口及其功能:DAS_STS用于接收AD1674的STS狀態(tài)信號(hào),;DAS_IN(12位)用于接收AD1674并行12位轉(zhuǎn)換輸出,;CLK,RST用作系統(tǒng)時(shí)鐘和RESET的信號(hào),。輸出端口DAS_RC接AD1674的R/C端,,用以控制A/D轉(zhuǎn)換器的啟動(dòng)和讀數(shù);DAS_A用作控制AD7502的A1A0通道選通信號(hào),;DAS_OUT(加通道的序號(hào)為16位)用作DAS控制單元的16位輸出數(shù)據(jù),。

DAS控制單元的有限狀態(tài)機(jī)(FSM)有4個(gè)狀態(tài),,分別為St0,,St1,St2,,St3,。St0為選擇通道,啟動(dòng)A/D轉(zhuǎn)換,,進(jìn)入St1狀態(tài),;St1為等待轉(zhuǎn)換結(jié)束,若轉(zhuǎn)換結(jié)束,進(jìn)入St2狀態(tài),,否則保持在St1狀態(tài),;St2為發(fā)出讀數(shù)據(jù)信號(hào),進(jìn)入St3狀態(tài),;St3為輸出轉(zhuǎn)換數(shù)據(jù),;選擇其他通道,返回St0狀態(tài),。DAS控制單元采用VHDL語(yǔ)言進(jìn)行開(kāi)發(fā),,程序的部分代碼如下所示:

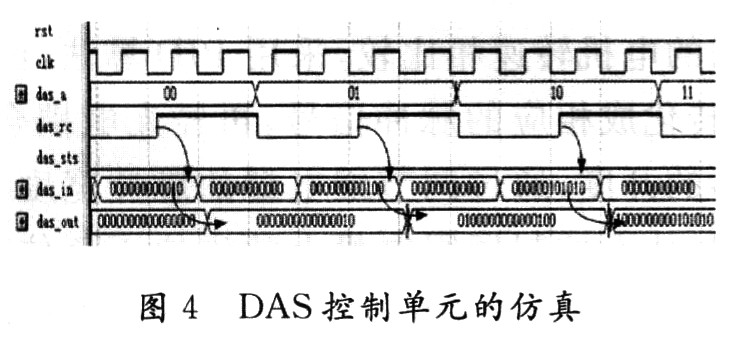

DAS控制單元的仿真如圖4所示。圖中顯示控制單元運(yùn)行正確,。

3.3 智能傳感器系統(tǒng)軟件工作流程

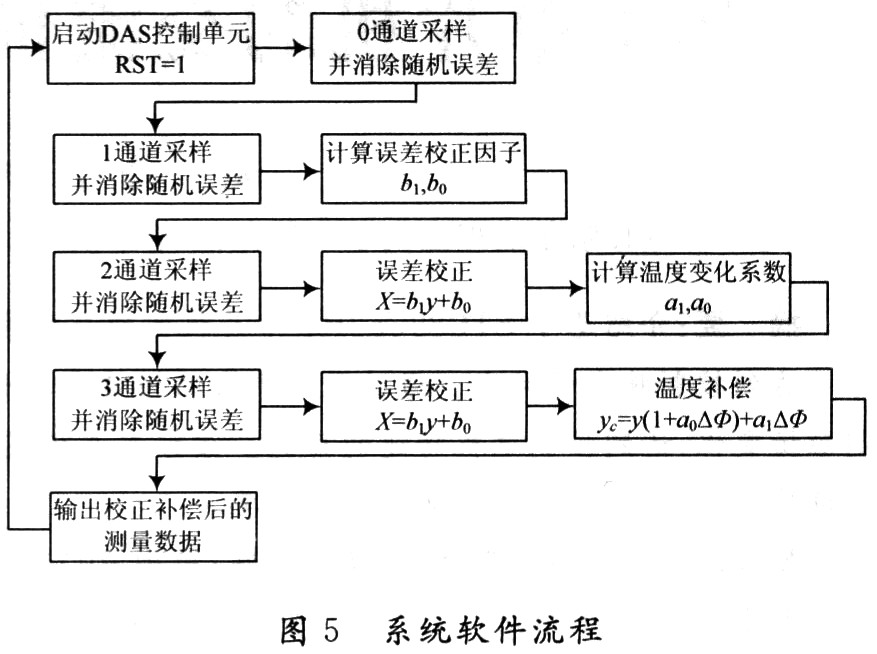

系統(tǒng)中誤差校正和溫度補(bǔ)償由系統(tǒng)軟件控制完成,。系統(tǒng)軟件由SoPC Builder工具中的軟件開(kāi)發(fā)工具(SDK)進(jìn)行開(kāi)發(fā)。系統(tǒng)軟件流程如圖5所示,。

系統(tǒng)上電初始化并啟動(dòng)DAS控制單元,,選通每個(gè)通道并消除每個(gè)通道的隨機(jī)誤差;然后根據(jù)校正過(guò)的0通道和1通道的數(shù)值,,實(shí)時(shí)計(jì)算出誤差校正因子,,依據(jù)誤差校正公式(1)實(shí)時(shí)校正零點(diǎn)漂移校準(zhǔn)和增益誤差,再根據(jù)測(cè)量得到傳感器的工作溫度,,計(jì)算與標(biāo)準(zhǔn)溫度的差值,,通過(guò)查表獲得傳感器溫度變化系數(shù),最后依據(jù)溫度補(bǔ)償公式(5)校正測(cè)量壓力數(shù)據(jù),,并將數(shù)據(jù)輸出,。

4 結(jié) 語(yǔ)

在系統(tǒng)的設(shè)計(jì)過(guò)程中,充分利用FPGA構(gòu)建系統(tǒng)靈活,,軟,、硬件開(kāi)發(fā)相結(jié)合的特點(diǎn),在滿足系統(tǒng)性能的基礎(chǔ)上,,合理分配軟硬件功能,,簡(jiǎn)化系統(tǒng)設(shè)計(jì)。FPGA把過(guò)去由分立芯片實(shí)現(xiàn)的系統(tǒng)放在單個(gè)芯片中,,這種單片系統(tǒng)的設(shè)計(jì),,大大提高了系統(tǒng)的穩(wěn)定性和可靠性,同時(shí)提高了系統(tǒng)抗工業(yè)現(xiàn)場(chǎng)干擾的能力,。