對于各具特色的移動電話、移動GPS設(shè)備和消費電子小玩意等電池供電的便攜式設(shè)備應用來說,高端負載開關(guān)一直受到眾多工程師和設(shè)計人員的青睞。本文將以易于理解的非數(shù)學方式全方位介紹基于MOSFET的高端負載開關(guān),并討論在設(shè)計和選擇過程中必須考慮的各種參數(shù)。

高端負載開關(guān)的定義是:它通過外部使能信號的控制來連接或斷開至特定負載的電源(電池或適配器)。相比低端負載開關(guān),高端負載開關(guān)“流出”電流至負載,而低端負載開關(guān)則將負載接地或者與地斷開,因此它從負載“汲入”電流。

高端負載開關(guān)不同于高端電源開關(guān)。高端電源開關(guān)管理輸出電源,因此通常會限制其輸出電流。相反地,高端負載開關(guān)將輸入電壓和電流傳遞給“負載”,并且它不具備電流限制功能。

高端負載開關(guān)包含三個部分:

傳輸元件:本質(zhì)上是一個晶體管,通常為一個增強型MOSFET。傳輸元件在線性區(qū)工作,將電流從電源傳輸至負載,就像一個“開關(guān)”(與放大器相對應)。

柵極控制電路:向傳輸元件的柵極提供電壓來控制導通或關(guān)斷。它還被稱為電平轉(zhuǎn)換電路,外部使能信號通過電平轉(zhuǎn)換來產(chǎn)生足夠高或者足夠低的柵極電壓(偏置電壓)來全面控制傳輸元

件的導通和關(guān)斷。

輸入邏輯電路:主要功能是解釋使能信號,并觸發(fā)柵極控制電路來控制傳輸元件的導通和關(guān)斷。

傳輸元件

傳輸元件是高端開關(guān)最基本的組成部分。最經(jīng)常考慮的參數(shù),特別是開關(guān)導通時的阻抗(RDSON),與傳輸元件的結(jié)構(gòu)和特性有直接關(guān)系。

由于增強型MOSFET一般在工作期間消耗的電流較少,在關(guān)斷期間泄漏的電流也較少,并且具有比雙極晶體管更高的熱穩(wěn)定性,所以被廣泛用作高端負載開關(guān)中的傳輸元件。本文將專門介紹基于增強型MOSFET的傳輸元件。增強型MOSFET傳輸元件可以是N溝道FET,也可以是P溝道FET。

當N溝道FET的柵極電壓(VG)比其源極電壓(VS)和漏極電壓(VD)高出一個閾值(VT)時,N溝道FET就會被完全轉(zhuǎn)換至導通狀態(tài)或者工作于其線性區(qū)。以下式子給出了導通條件的數(shù)學表達式:

VG-VS=VGS>VT

VG-VT>VD

或者是,

VGS-VT>VDS

其中,VG為柵極電壓、VS為源極電壓、VD為漏極電壓、VT為FET的閾值電壓、VGS為柵-源極壓降、VDS為漏-源極壓降,所有參數(shù)均為正。

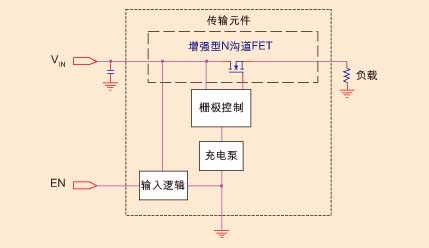

圖1:具有內(nèi)置電荷泵的N溝道FET高端負載開關(guān)。

當N溝道FET導通時,漏極電流ID為正,從漏極流向源極(如圖1和圖2所示)。當P溝道FET的柵極電壓(VG)比其源極電壓(VS)和漏極電壓(VD)低出一個閾值(VT)時,P溝道FET就會被完全轉(zhuǎn)換至導通狀態(tài)或者工作于其線性區(qū):

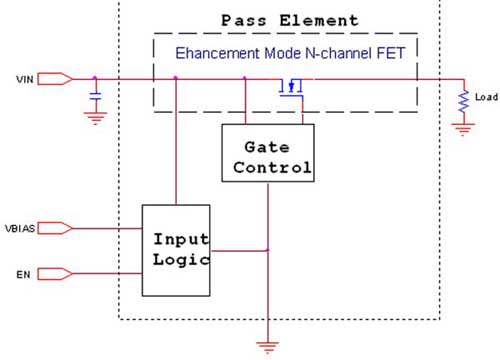

圖2:具有額外VBIAS輸入的N溝道FET高端負載開關(guān)。

VS-VG=VSG>VT

VD-VT>VG

或者是, VSG-VT>VSD

其中,VG為柵極電壓、VS為源極電壓、VD為漏極電壓、VT為FET的閾值電壓、VSG為源柵極壓降、VSD為源漏極壓降,這里的所有參數(shù)也均為正的。

當P溝道FET處于導通狀態(tài)時,漏極電流ID為負,從源極流向漏極(圖3)。N溝道FET將電子用作“多數(shù)載流子”,與P溝道FET的“多數(shù)載流子”空穴相比,電子具有更高的移動率。這意味著,在相同的物理密度下,N溝道FET比P溝道FET具有更高的跨導,從而使得在導通狀態(tài)期間產(chǎn)生較低的漏-源極阻抗(即RDSON)。N溝道FET的RDSON一般為相同尺寸的P溝道FET的RDSON的1/3~1/2,漏極電流ID也會高出相應的倍數(shù)(未考慮連接線厚度和封裝等其它限制參數(shù))。這還表示,對于相同的RDSON和ID,N溝道FET一般需要較少的硅片,因此它的柵極電容和閾值電壓比P溝道FET要低。

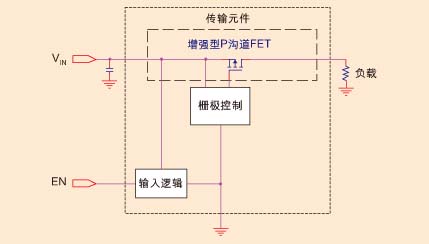

圖3:P溝道FET高端負載開關(guān)。

此外,由于當開關(guān)導通時N溝道FET的VD比VG低VT,并且VD一般與VIN相連,因此有可能傳遞給負載的VIN非常低。理論上講,N溝道FET開關(guān)的VIN可以低至接近GND,并且不高于VG-VT。另一方面,P溝道FET開關(guān)傳遞給負載的VIN(與VS相連)總是高于VG+VT。但這并不表示在任何情況下選擇傳輸元件時N溝道FET都比P溝道FET好。

如上所述,N溝道FET的一個基本屬性是開關(guān)導通時工作在線性區(qū),VG要比VD高VT。但是,由于VD幾乎總是與VIN(通常是開關(guān)的最高電壓)相連,因此VG必須從現(xiàn)有電壓(如外部使能信號EN)進行由低向高的電平轉(zhuǎn)換,或者通過直流偏移進行從低向高的偏置,直流偏移是單個新的高壓軌,通常被稱為“VBIAS”。

如果柵極電壓從使能信號進行從低向高的電平轉(zhuǎn)換,通常需要一個電荷泵作為附加的內(nèi)部電路。電荷泵需要一個內(nèi)置的振蕩器,芯片上至少需要一個“快速”(flying)電容器,從而產(chǎn)生柵極電壓(通常是在導通過程中的多個使能信號)。這當然增加了設(shè)計復雜性和硅片大小,從而抵消了N溝道FET因RDSON較低所帶來的硅片縮小的優(yōu)勢。當負載電流相對較低(幾安培)時,電荷泵確實會增加硅片面積,并且增加的面積比RDSON所能縮小的面積要大,這使得N溝道開關(guān)解決方案的成本和設(shè)計復雜性要高于P溝道開關(guān)方案。更多細節(jié)如圖1所示。

如果柵極電壓通過直流偏移VBIAS進行從低向高的偏置,就不再需要電荷泵,從而硅片面積的增加也不再是主要問題。但是由于可能不具備額外的高壓軌(這是大多數(shù)電池供電的設(shè)置和器件都需要的),因此這可能不是系統(tǒng)級的最佳解決方案(圖2)。

而在P溝道FET中,VG通常低于VS(與VIN相連)。只要開關(guān)導通時VS保持在VG±VT的范圍,那么它將始終工作在線性區(qū),并且不需要特定的內(nèi)部電路或外部電壓軌。這是通過采用柵極控制電路將使能信號的電平從高向低轉(zhuǎn)換至適當?shù)腣G電平來實現(xiàn)的。此方案不需要太多的電路或者額外的硅片面積(見圖3)。

N溝道高端負載開關(guān)通常是要求極低RDSON的高功率系統(tǒng)或者要求將接近

GND的低VIN傳遞給負載的低輸入電壓系統(tǒng)的理想選擇。另一方面,P溝道高端負載開關(guān)在要求設(shè)計復雜度不高的低功率系統(tǒng)或者要求將高VIN傳遞給負載的高輸入電壓系統(tǒng)中具有一定優(yōu)勢。

柵極控制

柵極控制電路或者電平轉(zhuǎn)換電路通過控制MOSFET的VG來實現(xiàn)其導通或關(guān)斷。柵極控制電路的輸出由從輸入邏輯電路收到的輸入直接決定。

在導通期間,柵極控制電路的主要任務是對使能信號進行電平轉(zhuǎn)換,以產(chǎn)生高(N溝道)或低(P溝道)VG來完全導通開關(guān)。同樣,在關(guān)斷期間,柵極控制電路產(chǎn)生低(N溝道)或高(P溝道)VG來完全關(guān)斷開關(guān)。

許多高端負載開關(guān)都在柵極控制電路中采用“斜率控制”或“軟啟動”功能。斜率控制功能可以在開關(guān)導通時限制VG的上升速度,從而逐步產(chǎn)生ID。其目的是為了保護負載不受過多“電涌”的影響,電涌有可能導致栓鎖等故障。

負載有時不僅僅具有阻抗性,也會具有高容性。因此,當開關(guān)關(guān)斷時,聚集在容性負載上的電荷不會迅速放電,這會導致負載沒有完全關(guān)斷。為了避免這種情況,一些高端負載開關(guān)加入了“活動負載放電”功能,其目的是提供一個電流通路,在開關(guān)關(guān)斷時使容性負載迅速放電。通常采用一個小型低端FET來實現(xiàn)該功能。圖4是該方法的示意圖,其中,底部N溝道FET的柵極與柵極控制內(nèi)核相連,漏極與負載相連,當頂部的主開關(guān)P溝道FET關(guān)斷時,底部的N溝道FET導通,以使容性負載放電。

圖4:MIC94060/1/2/3P溝道高端負載開關(guān)產(chǎn)品結(jié)構(gòu)圖。

輸入邏輯

輸入邏輯電路的唯一功能是解釋使能信號,并將正確的邏輯電平傳遞給柵極控制電路,以便柵極控制電路能夠以輸入邏輯電平控制傳輸元件的導通和關(guān)斷。輸入邏輯電路只采用下拉電阻就可以實現(xiàn)。

在某些情況下,使能信號和柵極控制電路之間需要緩沖器。這是因為使能信號無法為柵極控制電路提供足夠的驅(qū)動電流來驅(qū)動VG,而緩沖器卻可以充當額外驅(qū)動電流的來源。

關(guān)鍵應用參數(shù)

工程師在設(shè)計中采用高端負載開關(guān)時需要考慮一些關(guān)鍵應用參數(shù)。

第一個關(guān)鍵參數(shù)是ID。這是在設(shè)計周期早期選擇的系統(tǒng)級參數(shù)。高端負載開關(guān)的ID由MOSFET物理特性(N溝道或P溝道)、MOSFET的尺寸、連接線的物理特性(長度和厚度)以及封裝的熱性能等參數(shù)決定。通常,高ID開關(guān)為N溝道,采用熱增強型封裝,而低ID開關(guān)為P溝道,采用小型封裝。

第二個關(guān)鍵參數(shù)為RDSON。當選定ID時,RDSON越低就越好。這是因為較低的RDSON可以提高總效率、降低VIN和負載之間的壓降并減輕開關(guān)的散熱壓力。

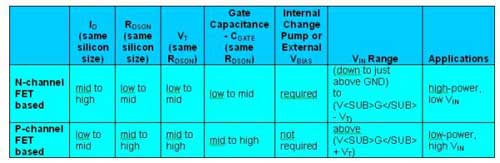

表1:N溝道FET開關(guān)和P溝道FET開關(guān)的比較。

如果ID和RDSON都已確定,設(shè)計人員通常會考慮開關(guān)的以下四個關(guān)鍵參數(shù):動態(tài)響應、關(guān)斷電源電流、關(guān)斷泄漏電流和封裝尺寸。

對于高端負載開關(guān),動態(tài)響應是指負載電壓隨著使能信號邏輯電平的變化從GND升至VOUT(=VIN-RDSON×ID)或者從VOUT降至GND所用的時間。

當使能信號在傳播延遲或?qū)ㄑ舆t時間(tON_DLY)之后使能時(由柵極控制電路和輸入邏輯電路引起),VG將轉(zhuǎn)換至導通開關(guān)所需的足夠高(或足夠低)的電平。此時,負載上的輸出電壓(N溝道FET開關(guān)的輸出電壓為VS,P溝道FET開關(guān)的輸出電壓為VD)開始上升,電壓達到滿VOUT所用的時間稱為導通上升時間(tON_RISE)。要求快速響應的應用需要tON_DLY和tON_RISE足夠短,而需要軟件啟動來限制電涌的應用則要求tON_DLY和tON_RISE相對較長,這取決于系統(tǒng)要求。

同樣,當使能信號在傳播延遲或關(guān)斷延遲時間(tON_DLY)之后使能無效時,VG將轉(zhuǎn)換至關(guān)斷開關(guān)所需的足夠低(或足夠高)的電平。此時,負載上的輸出電壓從滿VOUT開始下降,電壓下降到GND所用的時間稱為關(guān)斷下降時間(tOFF_FAIL)。通常要求tOFF_DLY和tOFF_FAIL足夠短,以便負載能夠迅速被關(guān)斷。如果負載具有較大的容性元件,活動負載放電功能將有助于減小tOFF_FAIL。

關(guān)斷電源電流和關(guān)斷泄漏電流也是需要考慮的重要參數(shù),特別是在設(shè)計需要較長的電池工作時間的電池供電設(shè)備時。

關(guān)斷電源電流是內(nèi)部電路在開關(guān)關(guān)斷時消耗的電流。關(guān)斷泄漏電流是開關(guān)關(guān)斷時MOSFET傳遞給輸出的電流。關(guān)斷電源電流和關(guān)斷泄漏電流越低,系統(tǒng)總效率就越高。對于電池供電的應用,這可以獲得更長的電池工作時間。

對于封裝尺寸(管腳面積和外形輪廓)而言,很明顯是越小越好。特別是對于空間有限的低電流系統(tǒng)(電池供電的手持設(shè)備)中使用的P溝道開關(guān),情況更是如此。

Micrel半導體公司提供一套完整的P溝道FET高端負載開關(guān),目標市場為電池供電的便攜式設(shè)備。最新成員MIC94060/1/2/3產(chǎn)品系列擁有業(yè)內(nèi)領(lǐng)先的關(guān)鍵參數(shù),而這些參數(shù)都是設(shè)計師們最關(guān)心的。

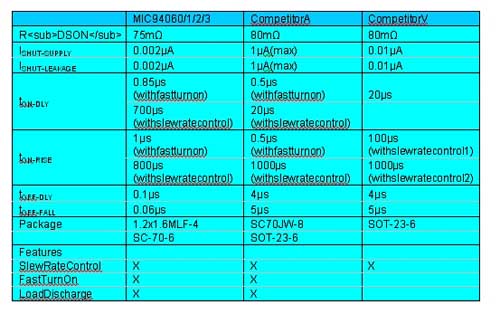

表2:MIC94060/1/2/3與其它產(chǎn)品的比較。

從表2可看出,MIC94060/1/2/3可在2A電流等級提供75m?的最佳RDSON。此外,它還具有市場上最低的關(guān)斷電源電流和關(guān)斷泄漏電流,具有導通和關(guān)斷狀態(tài)下出色的動態(tài)響應以及1.2×1.6mm的最小MLF封裝。因此,在文章開頭提到的那些電池供電的便攜式設(shè)備中,MIC94060/1/2/3已經(jīng)確立了其性能領(lǐng)先的地位。