引言

隨著中國開始在人口密集的都市部署第三代(3G)無線業(yè)務(wù),各種客觀局限性驅(qū)使用戶對高性能模數(shù)轉(zhuǎn)換器(ADC)提出更多重要需求。高速ADC的應(yīng)用多種多樣,但低功耗是用戶普遍要求的關(guān)鍵因素。要為用戶的最終產(chǎn)品提供具有競爭性的優(yōu)勢,ADC需要在更低的功率和更小的尺寸基礎(chǔ)上實現(xiàn)高分辨率、高速度和高性能。

3G基礎(chǔ)設(shè)施要求

高速ADC在GSM、WCDMA和TD-SCDMA基站的接收(Rx)和發(fā)射(Tx)通路中發(fā)揮著重要作用。雖然前一代設(shè)計方案廣泛使用消耗功率超過1500mW的高功率ADC,新型基站設(shè)計方案仍然需要具有高性能的低功率ADC。在城域中尤其如此,因為都市需要微基站和皮基站的密集網(wǎng)絡(luò)來保證服務(wù)質(zhì)量。除了對低功率工作這種顯而易見的要求之外,小尺寸的基站在核心元器件的熱耗散上還有額外限制。有限的系統(tǒng)散熱能力經(jīng)常成為實現(xiàn)集成密度的瓶頸。有競爭優(yōu)勢的系統(tǒng)設(shè)計方案要求ADC在緊湊和低功率基礎(chǔ)上,實現(xiàn)高性能的同時還要保持低溫度。

由于最終客戶的要求不同,不同的制造商所選擇的Rx通路架構(gòu)也大相徑庭。前一代接收器通常使用雙ADC對從單通道解調(diào)的I和Q信號采樣。因為在這

種方法中I和Q信號相對靠近基帶,對雙ADC的性能要求也相對較低。就下一代設(shè)計而言,趨勢是通過直接在中頻(IF)采樣,由單個Rx通路支持多通道傳輸。該架構(gòu)對ADC的要求更高。考慮到多個載波的頻率規(guī)劃情況,14位通常要求65Msps或80Msps的采樣率。由于IF頻率常在70MHz至140MHz之間,好的欠采樣性能也是必需的。

3G基站的Tx通路中也需要高性能ADC。在Tx通路中,輸出功率放大器(PA)的非線性限制了系統(tǒng)級性能,因此要采用不同的方法線性化PA輸出。以前,PA線性化通過如前饋方法的全模擬技術(shù)實現(xiàn)。就下一代設(shè)計而言,發(fā)展趨勢是通過采用快速反饋通路對PA輸入進(jìn)行數(shù)字化預(yù)失真來補(bǔ)償其非線性。

例如,盡管主流WCDMA基站一般在12位時要求125Msps采樣率,但PA線性化所需采樣率取決于數(shù)字化載波數(shù)量以及線性化在何種頻率范圍內(nèi)有效。為了減少RF下變頻階數(shù),目前趨勢是在更高的IF頻率上采樣。由于目標(biāo)IF頻率在100MHz至200MHz范圍內(nèi)已很普遍,ADC必須具有卓越的欠采樣性能。

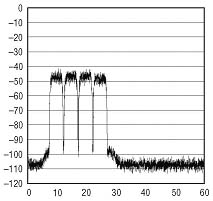

在同時數(shù)字化多個WCDMA調(diào)制載波時,該應(yīng)用的一個重要衡量指標(biāo)是ADC的相鄰?fù)ǖ佬孤┞剩ˋCLR)。圖1所示是一個常見方案的FFT頻譜,其中4個以140MHz為中心的WCDMA載波以122.88Msps采樣率和12位分辨率采樣。ACLR測量結(jié)果反映該ADC在靠近每個載波邊緣的頻率信噪比(SNR)與其互調(diào)失真。該測量常常被視為判定某特定ADC可否用于一個給定PA線性化應(yīng)用的關(guān)鍵測試。

圖1

如何挑選一個高速ADC

高速ADC的性能特性對整個信號處理鏈路的設(shè)計影響巨大。系統(tǒng)設(shè)計師在考慮ADC對基帶影響的同時,還必須考慮對射頻(RF)和數(shù)字電路系統(tǒng)的影響。由于ADC位于模擬和數(shù)字區(qū)域之間,評價和選擇的責(zé)任常常落在系統(tǒng)設(shè)計師身上,而系統(tǒng)設(shè)計師并不都是ADC專家。

除了上文提及的用戶需求之外,還有一些重要因素用戶在最初選擇高性能ADC時常常忽視。他們可能要等到最初設(shè)計樣機(jī)將要完成時才能知道所有系統(tǒng)級結(jié)果,而此時已不太可能再選擇另外的ADC。

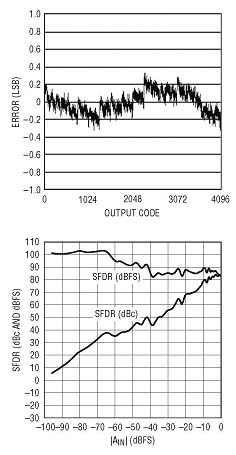

影響很多無線通信系統(tǒng)的重要因素之一就是低輸入信號電平時的失真度。大多數(shù)無線傳輸?shù)竭_(dá)ADC的信號電平遠(yuǎn)低于滿標(biāo)度輸入范圍。為確保多路傳輸信號的功率同時匯集到ADC輸入時不發(fā)生壓縮,信號鏈路的前端增益被設(shè)計成稍微低于ADC的滿標(biāo)度范圍。然而,幾乎所有高速ADC都保證其SFDR性能在輸入電平從滿標(biāo)度的 -1dB。此外,大多數(shù)數(shù)據(jù)表都有寬輸入幅度范圍內(nèi)典型的SFDR圖。用戶應(yīng)該仔細(xì)觀察該曲線,核實運行是否穩(wěn)定和是否可預(yù)知。低輸入幅度上存在任何大步進(jìn)或鋸齒特性都表明ADC轉(zhuǎn)移函數(shù)中的系統(tǒng)非線性。由于轉(zhuǎn)移函數(shù)線性度和低輸入電平失真密切相關(guān),對最大積分非線性(INL)有嚴(yán)格保證的ADC在低輸入幅度上一般會有更穩(wěn)定的失真性能。

選擇對INL、差分非線性(DNL)、SNR和SFDR等所有關(guān)鍵性能規(guī)格具保證最小或最大值限制的ADC是非常重要。這些規(guī)格在應(yīng)用的整個工作溫度范圍內(nèi)應(yīng)該得到保證。用戶特別需要留意這些關(guān)鍵參數(shù)是否僅在小溫度范圍內(nèi)或室溫下才能保證。高速ADC內(nèi)部的精確運算放大器和快速比較器如果設(shè)計得不夠堅固,它們在溫度變化時可能會發(fā)生很大的變化。選擇沒有寬溫度范圍內(nèi)保證限制的ADC會給設(shè)計帶來不必要的風(fēng)險。

解決方案的尺寸要求也很關(guān)鍵,因為都市基站設(shè)計的PCB面積非常有限。由于使用QFN等小型扁平IC封裝縮減小了ADC本身的面積,總體解決方案面積實際上可能大得多。仔細(xì)察看所推薦的電路會發(fā)現(xiàn)很多高速ADC都需要大量電容值很大的電容器(如10μF),這些電容器比ADC占用的PCB面積大得多。由于存在封裝連接線寄生電感,很多高速ADC需要此類大外部電容器旁路電源和內(nèi)部基準(zhǔn)電路系統(tǒng)。要在最終產(chǎn)品中實現(xiàn)小體積,就要求ADC不僅采用小型封裝,而且還要使這些大的外部旁路電容器尺寸和數(shù)量最小化。

技術(shù)趨勢

除了新穎的電路設(shè)計技術(shù),工藝的進(jìn)步在低功率高速ADC的開發(fā)中同樣重要。特別值得一提的是,由于數(shù)字技術(shù)最初的驅(qū)使,硅技術(shù)工藝不斷調(diào)整,采用CMOS工藝制造的ADC也因此受益匪淺。

就模擬電路設(shè)計而言,CMOS工藝調(diào)整的關(guān)鍵優(yōu)勢在于更低的功率和更高的速度運作。與僅消耗動態(tài)功率的傳統(tǒng)數(shù)字CMOS電路不同,ADC消耗的大部分功率都是靜態(tài)電流用來偏置放大器和比較器等模擬電路引起的。對給定的模擬偏置電流,更短的通道長度(L)工藝為晶體管提供更高的跨導(dǎo)(gm),這是器件性能的一個關(guān)鍵衡量指標(biāo)。更小的晶體管尺寸也使器件的寄生電容更小。在高速ADC的每一種流水線級上,精確運算放大器等關(guān)鍵電路的模擬穩(wěn)定速度極大程度上由晶體管gm決定。因此,在給定總偏置電流情況下,縮短L會使工作速度更快。

另一個好處是,電源電壓通常隨著L縮短而降低,因此即使模擬偏置電流保持不變,總體功耗也會降低。通過工藝精細(xì)程度的調(diào)整,ADC設(shè)計師可以靈活地在給定功率級別上提高速度或在給定速度時降低功率。

然而,模擬電路的工藝調(diào)整存在一個嚴(yán)重的缺點。由于降低了電源電壓,ADC的滿標(biāo)度輸入范圍也必須降低,以便為運算放大器等模擬電路系統(tǒng)提供足夠的電壓空間。更小的輸入范圍導(dǎo)致更低的信號功率,SNR會隨著工藝調(diào)整而下降。低功率、高性能設(shè)計方案的挑戰(zhàn)還在于降低ADC產(chǎn)生的噪聲,以保持足夠的信噪比。

凌特公司低功率高性能ADC介紹

很明顯,低功率、高性能是市場上用戶的主要要求。為滿足市場需求,凌特公司新近推出了幾個高速ADC系列。

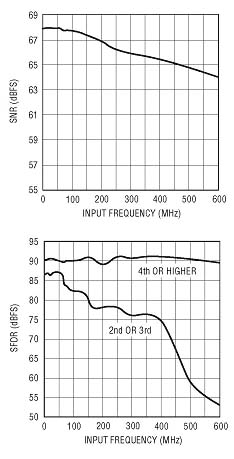

LTC2224/2222/2223是引腳兼容的3.3V 12位135/105/80Msps ADC,并為欠采樣而優(yōu)化。LTC2224系列在輸入頻率高達(dá)140MHz時具有超過67.5dB的SNR和80dB的SFDR,而在135Msps時僅消耗630mW功率。該高度優(yōu)化的跟蹤與保持設(shè)計對高達(dá)400MHz的輸入頻率持續(xù)保持超過65dB的SNR和75dB的SFDR,在低功率時具有極佳的欠采樣性能。圖2概括了LTC2224的高頻性能。即使是那些消耗功率高得多的器件也極少在高輸入頻率時具有如此的欠采樣性能。如圖3所示,就12位ADC而言,該ADC轉(zhuǎn)移函數(shù)的線性度也很高,可與很多14位器件媲美。如同干凈的轉(zhuǎn)移函數(shù)預(yù)料,小輸入幅度時的失真性能也相當(dāng)穩(wěn)定。LTC2224系列非常適合要求低功率和卓越欠采樣性能的WCDMA PA線性化應(yīng)用。

圖2

圖3

LTC2249/LTC2229系列是引腳兼容的3V 14位/12位ADC,具有高達(dá)80Msps的速度。表1概括了這些器件的性能特性。這些高速ADC功率極低,范圍從LTC2249/LTC2229在80Msps時的222mW至LTC2245/LTC2225在10Msps時的60mW。實現(xiàn)這些低功率并未損失性能。例如,如圖4所示,LTC2248(65Msps)對遠(yuǎn)離奈奎斯特頻率(Nyquist Frequency)的輸入保持為74dB SNR和80dB SFDR。通過使用5mm×5mm纖巧型QFN封裝,這兩個系列還實現(xiàn)了小體積。大部分必需的旁路電容都直接集成在芯片上,因此這些器件僅需要少量低值外部旁路陶瓷電容器,就能達(dá)到數(shù)據(jù)表所顯示的性能。引腳兼容的LTC2249和LTC2229系列具有高性能,低功耗,小體積的特點。使它們非常適合用于小型WCDMA、GSM和TD-SCDMA等基站。

圖4

表1

結(jié)論

都市基站設(shè)計方案在高輸入頻率和寬輸入帶寬時要求良好的SNR和SFDR性能。這樣就需要有高線性度的跟蹤與保持設(shè)計以及小內(nèi)部采樣時鐘抖動;每一方面在ADC中都需要消耗功率。很多低功率ADC的SNR和SFDR都隨著輸入頻率的提高而迅速下降,因為內(nèi)部時鐘抖動和跟蹤與保持電路的非線性主要影響了響應(yīng)。但是,最近推出的低功率和小尺寸的高性能ADC克服了這些問題,滿足了新一代無線通信市場對尺寸更小、功率效率更高產(chǎn)品的需求。