2010年一季度,LSI發(fā)布了新一代多核媒體處理器或基帶處理器:StarPro2704和StarPro2716(簡稱SP27xx)。LSI上一代多核媒體處理器StarPro2603和StarPro2612(簡稱SP26xx)已經(jīng)在2G無線基帶及語音媒體網(wǎng)關(guān)上成功應用。SP27xx相比SP26xx,在媒體和基帶算法處理能力上有至少2倍的增強,同時在降低功耗方面加入了很多先進技術(shù)。針對運營商級和中小企業(yè)級的3G/4G無線基站、更高密度的語音媒體網(wǎng)關(guān)以及高清視頻服務(wù)器等方面的應用,SP27xx均能提供業(yè)界領(lǐng)先的高性能低功耗的解決方案。本文首先介紹SP27xx的新特性,然后著重分析SP27xx在高清視頻領(lǐng)域的應用。

SP27xx體系結(jié)構(gòu)

SP2716是通過MCM多芯片封裝工藝將4個SP2704的裸片封裝成一個芯片,其處理能力是SP2704的4倍。相對于4個SP2704,SP2716大大放寬了對單板尺寸的限制,這使得用戶能夠更方便地擴展高端音視頻業(yè)務(wù)。下文重點介紹SP2704的體系結(jié)構(gòu)。

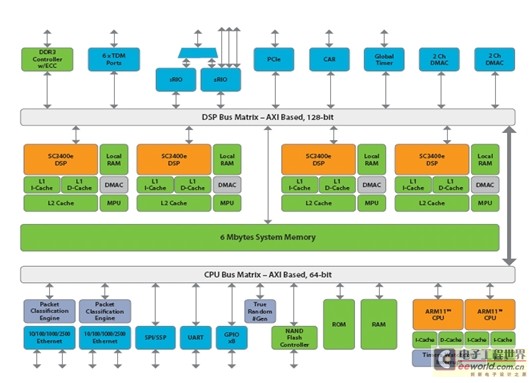

SP2704繼承了SP2603的體系構(gòu)架,由2個基本模塊組成:媒體處理模塊(MPB)和包處理模塊(PPB)。媒體處理模塊主要由4個SC3400e的DSP子系統(tǒng)組成,而包處理模塊的核心是ARM11雙核處理器系統(tǒng)。在這種單芯片DSP+ARM的多核處理器結(jié)構(gòu)中,數(shù)據(jù)面和控制面分別由DSP和ARM來處理,使得DSP可以最大程度地利用其運算優(yōu)勢,同時不需要額外使用片外處理器來處理應用程協(xié)議,是最高效的音視頻媒體網(wǎng)關(guān)結(jié)構(gòu)。

SP2704擁有超大的片內(nèi)內(nèi)存,對于高密度語音網(wǎng)關(guān)和非高清視頻應用,一般不需要使用片外存儲區(qū),這就最大程度地降低了成本和單板總功耗,減少了軟硬件設(shè)計復雜度,也放寬了單板尺寸的限制。此外,SP27xx采用了業(yè)界領(lǐng)先的40nm芯片工藝,還引入了許多先進的低功耗技術(shù)。以語音網(wǎng)關(guān)應用為例,SP27xx的每通道功耗遠遠低于業(yè)界其他同類芯片。

1)DSP子系統(tǒng)(DSS)

SP2704有4個頻率為750MHz的StarCore SC3400eDSP子系統(tǒng)(DSS)。相對上一代芯片SP2603,如果不考慮DSP內(nèi)核能力的增強,SP2704的DSP處理能力可達SP2603的兩倍。每個DSS還包含內(nèi)存保護單元(MPU),256KB本地零等待RAM,32KB一級指令高速緩存,32KB一級數(shù)據(jù)高速緩存,512KB L2高速緩存,兩個專用的2通道DMA控制器。

2)包處理模塊(PPB)

包處理模塊(PPB)是基于雙核ARM11 MP的子系統(tǒng),工作頻率僅為DSS工作頻率的一半。PPB主要負責整個芯片加載和管理(包括ARM和DSP),以及輸入輸出數(shù)據(jù)包的管理。PPB還包括:ROM用于存放ARM Boot代碼,以及SPI/SSP、UART、NAND flash控制器接口,可為客戶提供多種Boot方式。

3)豐富的片內(nèi)內(nèi)存和2個超高帶寬總線

SP2704中有2個超高帶寬總線矩陣:DSP總線矩陣和PPB總線矩陣,可用作數(shù)據(jù)處理功能模塊的系統(tǒng)互連,以1/2DSP子系統(tǒng)時鐘速率運行,帶寬分別是128位和64位。SP2704擁有豐富的片內(nèi)內(nèi)存,除了DSP和ARM子系統(tǒng)內(nèi)部的零等待RAM,還有一個6M的片內(nèi)系統(tǒng)共享內(nèi)存。共享內(nèi)存分成12個存儲塊,不同的內(nèi)核可以同時訪問不同的存儲塊,真正達到了數(shù)據(jù)訪問的高吞吐量、高可用性以及低時延。

4) 豐富的接口資源

SP2704擁有豐富的接口資源,可以滿足各種音視頻網(wǎng)關(guān)服務(wù)器應用:兩個10/100/1000/2500Mbps以太網(wǎng)MAC,可配置為FE(SS-SMII)或GE(SGMII);TDM處理模塊通過6個串行端口進行TDM流量的多路復用和解多路復用;10Gbps x4 sRIO接口(4個3.125Gbps Lane)或者配置為兩個獨立的x1SRIO接口;PCIe接口,可接到host或SP2704設(shè)備之間互聯(lián);32位DDR3接口工作頻率高達1066MHz。

圖1 SP2704媒體處理器體系結(jié)構(gòu)。

SC3400e---基于SC3400的增強

SC3400e與SC3400后向兼容,SC3400e繼承了SC3400的變長指令集(VLES)結(jié)構(gòu)和12級流水深度。SC3400e的能力增強表現(xiàn)在以下幾個方面:

1)實數(shù)和復數(shù)乘加能力的增強

SC3400e與SC3400的數(shù)據(jù)算術(shù)邏輯單元(DALU)都包含了4個乘加單元(MAC)。SC3400的MAC包含1個16位*16位的乘法器和1個40位的加法器;而SC3400e的MAC包含4個16位*16位的乘法器和2個40位的加法器,其加法器支持2個40位復數(shù)操作數(shù)的加/減法。實數(shù)乘加運算能力提高1倍,而復數(shù)乘加運算能力則是原來的4倍。

SC3400e的實數(shù)和復數(shù)MAC運算能力可概括為:每周期可完成8個16位實數(shù)乘加運算,性能是SC3400的2倍;每周期可完成4個16位(16位實部,16位虛部)的復數(shù)乘加運算,性能是SC3400的4倍;每周期可完成8個8位(8位實部,8位虛部)的復數(shù)乘加運算,性能是SC3400的8倍;每周期可完成4個32位*16位的實數(shù)乘加運算,性能是SC3400的2倍;每周期可完成4個(16位*16位+16位*16位+40位)的實數(shù)點積運算。如果設(shè)置了飽和模式,A=sat{sat{A+BxC}+DxE},則性能是SC3400的2倍。

2)在COF和控制代碼效率方面的改進

SC3400采用先進的動態(tài)分支預測機制,可有效減少COF(Change of Flow)的延遲。例如,某條JMP指令已經(jīng)在分支目標緩沖(BTB)中,實際執(zhí)行只需要1個周期,而不是6個周期。SC3400e在原有的分析預測機制的基礎(chǔ)上,完成了多方面的改進。

在SC3400e中,硬件循環(huán)和COF共同使用n個BTB,突破了SC3400中只支持4層嵌套的零開銷硬件循環(huán)的限制。而且,SC3400e還改進了硬件循環(huán)誤判的開銷,就算硬件循環(huán)條件不成立,開銷也只有3個周期,而在SC3400中這樣的開銷最多達6個周期;在SC3400e中,提高了短循環(huán)的執(zhí)行效率,同時短循環(huán)不再占用BTB;SC3400e支持4個返回地址寄存器,相對SC3400中的一個返回地址寄存器,減少了子程序返回的平均延遲。總體看,相對SC3400,SC3400e控制代碼的效率提高了0.25倍。

圖2 高清視頻編碼及解碼的多核功能分配示意圖。

3) 查找表的性能提高

在SC3400e中,帶有線性地址修改的指令1個周期就能完成。查找表的性能提高了0.5倍。

4) SC3400e中改進的視頻加速指令

SC3400e中改進的視頻加速指令主要包括:用于半像素插值的插值指令,性能提高1倍;用于運動補償?shù)腁dd-and-Sat指令,性能提高1倍;1個周期完成位插入或位抽取操作。對于位流與字節(jié)之間的pack/unpack及其他位流處理算法,性能提高1倍。

SP2704二級緩存的使用

SP2704支持二級緩存(L2 cache):其中一級緩存(L1 cache)分成32k指令緩存和32K數(shù)據(jù)緩存,二級緩存可靈活用于片外程序和數(shù)據(jù)的緩存。對于高清視頻編解碼的應用,需要使用DDR3存儲器來存儲大量的視頻數(shù)據(jù)。這時,一般會配置二級緩存映射到DDR存儲空間。同時,如果再配置L1 cache緩存L2 cache的數(shù)據(jù),對緩存進行合理的優(yōu)化,會使片外的視頻數(shù)據(jù)讀寫效率更高。

L2 cache還可以配置成共享內(nèi)存,如果L2 cache配置成共享內(nèi)存,6MB共享內(nèi)存的空間就擴展為8MB。對于不需要放置片外存儲器的應用,一般會把L2 cache配置成共享內(nèi)存,進一步增加數(shù)據(jù)和代碼的片內(nèi)存儲空間。

分層的多核編解碼器構(gòu)架

對于H.263或H.264的高清視頻編碼,一個DSP核無法完成1路圖像的編碼/解碼,因而需要由多個核協(xié)作完成,這就涉及到多核之間任務(wù)分配的問題。LSI目前采用靈活的多層編解碼構(gòu)架,以片(slice)為基本單位對圖像進行分割,每個核處理一個或多個片。這樣,可以在多核之間擴展,也可以通過sRIO、PCIe等高速互連總線在多器件之間擴展。

以1080P(1280*720)H.264的解碼和編碼為例,如果一個SP2704處理1路30fps 1080p H.264解碼,多個SP2704協(xié)同處理1路30fps 1080p H.264編碼,SP2704#1解碼后的YUV4:2:0的圖像數(shù)據(jù)提供給SP2704#2來進行編碼,參考幀數(shù)據(jù)將存放在DDR3存儲器中,如圖2所示。

多核分層編碼器

在協(xié)同處理1路圖像的多個核中,一個核作為主核,其他核為從核。主核除了要負責一些slice的編解碼之外,還要處理負荷平衡、場景識別及速率控制這樣的公共任務(wù)。其他從核將只是對分配的slice進行處理。

多核分割可以減少高清視頻編碼的延遲,而動態(tài)負荷平衡功能可最大程度減少延遲。SP2704內(nèi)部的4個DSP核可以通過6M的共享內(nèi)存和DDR3片外存儲器來共享視頻數(shù)據(jù):當前圖像存放在6M的共享內(nèi)存中,通過L1數(shù)據(jù)cache緩存片內(nèi)共享內(nèi)存的圖像數(shù)據(jù),參考圖像存放在DDR3外部存儲器中,通過L2 cache來緩存DDR3中的圖像數(shù)據(jù)。從而使得視頻數(shù)據(jù)訪問的速度達到最快。

SP2716中的2個SP2704之間可以通過PCIe共享DDR3存儲器,這樣可減少2個SP2704之間的數(shù)據(jù)交互,從而簡化了軟件開發(fā)的復雜度,還將整個硬件設(shè)計所需的DDR3設(shè)備數(shù)量減少了一半。此外,多個SP2704器件之間通過sRIO接口來傳輸或共享視頻數(shù)據(jù),這些SP2704都連接到sRIO開關(guān)上。每個器件都可以自發(fā)地寫入到其他任何一個器件的I/O空間。

多核解碼器

H.264解碼涉及串行操作和并行操作。熵解碼包含一系列串行操作,無法分配給多個內(nèi)核并行處理,因而將由主核處理,其他并行操作可以分配到各個從核來處理。LSI分層解碼器的基本原理是:由主核負責熵解碼,再把熵解碼后的數(shù)據(jù)分配到各個從核來處理。其他從核讀取數(shù)據(jù)后進行后續(xù)處理,例如逆量化、逆變換等;對于P宏塊還要從DDR3中讀取參考幀數(shù)據(jù)并進行運動補償。最后進行循環(huán)濾波,并把得到的宏塊數(shù)據(jù)存入DDR3的當前幀中。