1 引言

雷達(dá)回波模擬在雷達(dá)系統(tǒng)的設(shè)計(jì)、改進(jìn)和定型中具有十分重要的意義。AD9856是美國(guó)ADI生產(chǎn)的正交數(shù)字上變頻器,其內(nèi)部集成了1個(gè)高速直接數(shù)字頻率合成器(DDS)、1個(gè)12位高速、高性能數(shù)/模轉(zhuǎn)換器、時(shí)鐘倍頻電路、數(shù)字濾波器及其他數(shù)字信號(hào)處理功能模塊。它具有低成本、低功耗、體積小、動(dòng)態(tài)范圍大等優(yōu)點(diǎn),可以處理來(lái)自DSP的成型后的基帶抽樣值序列,將其上變頻變?yōu)橹蓄l,產(chǎn)生雷達(dá)回波的中頻模擬信號(hào)。AD9856可以應(yīng)用在通信和雷達(dá)等系統(tǒng)中。

2 AD9856的工作原理

2.1 AD9856的基本功能

AD9856的基本特性和技術(shù)指標(biāo)如下:

●+3V單電源供電;

●直流到80MHz的輸出帶寬;

●在40MHz輸出頻率下具有大于52dB的SF-DR,在70MHz輸出頻率下,SFDR大于48dB,在70MHz輸出頻率下的窄帶SFDR大于80dB;

●有采樣率可編程的內(nèi)插濾波器;

●有可編程的參考時(shí)鐘倍頻器;

●有內(nèi)置的Sinx/x補(bǔ)償濾波器;

●有雙向控制總線接口;

●支持突發(fā)和持續(xù)Tx二種模式

;

●單頻模式可用于直接頻率合成。

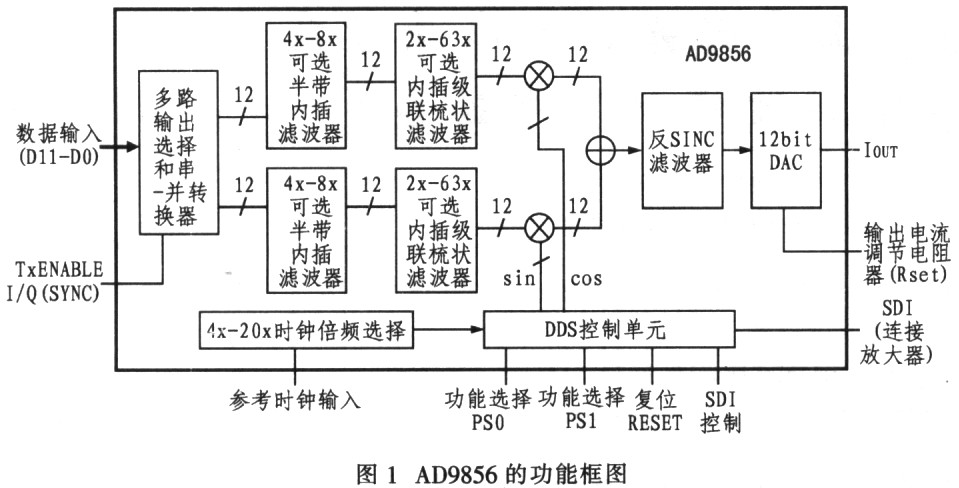

2.2 AD9856的原理及各部分的功能

(1)數(shù)據(jù)復(fù)合和串并轉(zhuǎn)換

AD9856的結(jié)構(gòu)如圖1所示。AD9856內(nèi)部的數(shù)據(jù)格式是12bit的二進(jìn)制補(bǔ)碼。基帶信號(hào)的I、Q2路數(shù)據(jù)是交替輸入的,數(shù)據(jù)復(fù)合器需對(duì)輸人數(shù)據(jù)進(jìn)行識(shí)別,將其轉(zhuǎn)換成I、Q2路并行數(shù)據(jù)流,送往下一級(jí)電路。

(2)半帶濾波器(HBF)

半帶濾波器(HBF)分為3級(jí):HBFl、HBF2和HBF3。其中HBFI是47階濾波器,HBF2是15階濾波器,前2級(jí)HBF的聯(lián)合內(nèi)插損失僅為0.01dB,HBF3是可選11階濾波器,它對(duì)信號(hào)的損耗為0.03dB。每級(jí)HBF可使數(shù)據(jù)的采樣率提高1倍,為了使信號(hào)頻帶處于濾波器通帶的平坦部分,需要提高HBF的截止頻率,也就是說(shuō)在數(shù)據(jù)輸入AD9856之前要進(jìn)行過(guò)采樣。

(3)級(jí)聯(lián)積分梳狀濾波器

AD9856的CIC實(shí)際上是可編程的過(guò)采樣濾波器,過(guò)采樣率的范圍是2≤R≤63。隨著R的改變, CIC會(huì)引入不同的插入損耗。為了彌補(bǔ)這種損耗。用戶(hù)可以設(shè)置CIC增益位,使得CIC的輸出增大1倍。但在這種工作模式下,必須確保輸出信號(hào)不會(huì)溢出。

(4)正交調(diào)制

AD9856的正交調(diào)制就是將基帶信號(hào)的頻譜移到所需要的載波頻率上,即通常所說(shuō)的上變頻。正交調(diào)制所需要的余弦和正弦2路數(shù)字載波由1個(gè)高速直接數(shù)字信號(hào)合成器(DDS)產(chǎn)生,其頻率可以通過(guò)設(shè)置相應(yīng)的寄存器來(lái)控制。這2路數(shù)字載波分別與CIC輸出的I、Q數(shù)據(jù)相乘,然后再進(jìn)行相加或相減,即得到調(diào)制后的數(shù)字中頻信號(hào)。CIC輸出的I、Q數(shù)據(jù)的采樣率與DDS數(shù)字載波的采樣率是相同的,也就是AD9856的系統(tǒng)時(shí)鐘采樣率(SYSCLK)。所以,調(diào)制后的信號(hào)實(shí)際上是一組采樣率為SYSCLK的數(shù)據(jù)流。

(5)數(shù)/模轉(zhuǎn)換

調(diào)制后的數(shù)字信號(hào)要經(jīng)過(guò)12位的DAC轉(zhuǎn)換成模擬信號(hào)。DAC通過(guò)零階保持實(shí)現(xiàn)數(shù)/模轉(zhuǎn)換。由于存在零階保持效應(yīng),所以其輸出信號(hào)的頻譜實(shí)際上是被SINC包絡(luò)加權(quán)過(guò)的。因此需要在DAC前面加上1個(gè)反SINC型濾波器(ISF)對(duì)輸人數(shù)據(jù)流進(jìn)行處理,以校正SINC包絡(luò)造成的失真。而數(shù)/模轉(zhuǎn)換會(huì)在n*SYSCLK±fCARRIER(n=1,2,3)處產(chǎn)生干擾信號(hào),這些干擾信號(hào)可以通過(guò)1個(gè)外接RLC濾波器濾除。一般情況下,使用1個(gè)7階橢圓低通濾波器即可。AD9856提供2路互補(bǔ)的2個(gè)電流輸出,輸出電流的滿(mǎn)額值IOUT范圍是5mA~20mA,可以通過(guò)其25引腳的DAC RSET,來(lái)設(shè)置。其關(guān)系為 RSET="39".936/IOUT

(6)控制單元

AD9856提供了1個(gè)靈活的同步串行通信接口,這個(gè)接口可以讀寫(xiě),AD9856的所有寄存器。控制單元根據(jù)各個(gè)寄存器的內(nèi)容設(shè)置AD9856的工作模式。AD9856還提供了1個(gè)與AD8320(可編程電纜驅(qū)動(dòng)放大器)串行通信的接口。控制單元可以通過(guò)這個(gè)串口直接設(shè)置AD8320的增益。

(7)輸入數(shù)據(jù)模式

AD9856提供了二種輸人數(shù)據(jù)的時(shí)序模式:突發(fā)模式和連續(xù)模式。在突發(fā)模式下.AD9856通過(guò)TxENABLE的上升沿來(lái)保持與輸人數(shù)據(jù)的同步。突發(fā)模式支持全部3種字長(zhǎng)(12bit、6bit和3bit)。對(duì)于連續(xù)模式,TxENABLE可以看成輸入數(shù)據(jù)時(shí)鐘。該信號(hào)除了用來(lái)同步外,還可以指示輸入數(shù)據(jù)是I路還是Q路(1表示I路,O表示Q路)。連續(xù)模式只支持12bit字長(zhǎng)。圖2和圖3分別示出二種輸入模式的時(shí)序關(guān)系,其中INTERNAL I和INTERNAL Q為數(shù)據(jù)分離所產(chǎn)生的并行I和Q數(shù)據(jù)流。

3 在PD雷達(dá)回波模擬器中的應(yīng)用

3.1 硬件組成

本系統(tǒng)由ADI的QDU AD9856、DGA AD8369、TSl01型DSP及Altera公司的EP1K30型FPGA組成,結(jié)構(gòu)框圖如圖4所示。

在圖4中,TS101產(chǎn)生正交I和Q2路雷達(dá)回波數(shù)據(jù),TSl0l通過(guò)外部總線將AD9856和AD8369的配置信息寫(xiě)入EP1K30。由于AD9856要求的配置信息是串行寫(xiě)入的,因此,需在EP1K30內(nèi)將TS101送出的并行指令變?yōu)榇兄噶睿凑誂D9856時(shí)序要求送入AD9856。將AD9856配置好后,TSl01以DMA方式將正交I和Q2路雷達(dá)回波數(shù)據(jù)通過(guò)數(shù)據(jù)總線送至AD9856,AD8369將AD9856產(chǎn)生的中頻模擬信號(hào)放大后,送入下一級(jí)電路處理。

3.2 AD9856串口操作

同步串口包括CS、SYNC I/O、S

CLK、SDIO和SDO 5條信號(hào)線。其中,CS為低有效串口使能信號(hào);SYNC I/O為串口同步恢復(fù)信號(hào),當(dāng)串口失去同步后,可在SYNC I/O上加1個(gè)正脈沖使串口恢復(fù)初始狀態(tài);SCLK為串口的數(shù)據(jù)時(shí)鐘信號(hào);SDIO為雙向數(shù)據(jù)線,當(dāng)串口置于雙線(SCLK和SDIO)方式時(shí),SDIO為雙向數(shù)據(jù)線。當(dāng)置于3線(SCLK、SDIO和SDO)模式時(shí).其輸出功能由SDO替代。對(duì)串口的操作有嚴(yán)格的時(shí)序要求,1個(gè)串口通信周期為指令周期和數(shù)據(jù)讀寫(xiě)周期。在初始狀態(tài),串口等候SCLK(上的8個(gè)上升沿指示的8bit指令,然后進(jìn)行由指令設(shè)定的1-4個(gè)字節(jié)的數(shù)據(jù)讀寫(xiě),讀串口由SCLK下降沿指示,而寫(xiě)串口由SCLK上升沿指示。完成后又等待下1個(gè)周期的到來(lái)。

根據(jù)串口寫(xiě)時(shí)序要求設(shè)計(jì)控制電路,在FPGA中實(shí)現(xiàn)AD9856的串口操作,對(duì)AD8369的控制也在此電路中實(shí)現(xiàn)。控制電路的原理框圖如圖5所示。

用FPGA將DSP輸出的并行指令變換為串行,指令的轉(zhuǎn)換時(shí)必須注意以下幾點(diǎn):

(1)串口支持MSB在前和LSB在前二種格式,通過(guò)寄存器O的第6位設(shè)置,并且對(duì)該位的設(shè)置是立即有效的。即如果當(dāng)前操作對(duì)該位進(jìn)行修改,則下1個(gè)字節(jié)的傳輸就會(huì)采用新的格式。

(2)對(duì)多字節(jié)傳輸?shù)耐ㄐ胖芷冢绻鸐SB在前,寄存器地址遞減;如果LSB在前,寄存器地址遞增。

(3)外部控制器必須與AD9856同步,如果失去同步。可由SYNC I/O重新產(chǎn)生同步,不必對(duì)這個(gè)電路進(jìn)行復(fù)位。

通過(guò)AD9856的串口設(shè)置好工作參數(shù)后,TS101以DMA方式將正交的I和Q2路數(shù)據(jù)交替送入AD9856得到正交上變頻后的模擬信號(hào)。

4 結(jié)束語(yǔ)

本系統(tǒng)利用AD9856實(shí)現(xiàn)正交上變頻,模擬了雷達(dá)回波波形,達(dá)到了預(yù)期的技術(shù)指標(biāo),在實(shí)際工程中運(yùn)行良好。此外,此系統(tǒng)還可以產(chǎn)生通信中常用的2ASK、2FSK和2PSK等信號(hào),試驗(yàn)證明其效果良好。