摘 要: 由于DM9000A需要復(fù)雜的初始化流程,因此多采用ARM或者內(nèi)嵌CPU的FPGA驅(qū)動(dòng),而使用這兩者通常都不能充分利用DM9000A的網(wǎng)絡(luò)帶寬。將DM9000A應(yīng)用在以FPGA器件為核心器件的網(wǎng)絡(luò)相機(jī)系統(tǒng)中。為了提高DM9000A的網(wǎng)絡(luò)發(fā)送帶寬,對(duì)DM9000A在FPGA平臺(tái)上的使用提出兩點(diǎn)改進(jìn),并在應(yīng)用系統(tǒng)中驗(yàn)證了改進(jìn)的可行性。

關(guān)鍵詞: DM9000A;高清網(wǎng)絡(luò)相機(jī);FPGA

1 硬件設(shè)計(jì)

DM9000A是Davicom公司推出的一款高速以太網(wǎng)接口芯片,是完全集成的符合成本效益的單芯片快速以太網(wǎng)MAC控制器,其功耗低,處理性能高,而其操作又非常簡(jiǎn)單,具有通用的處理器接口,可以與多種處理器直接連接,數(shù)據(jù)總線寬度可設(shè)置為8 bit和16 bit,支持3.3 V和5 V電源模式[1]。

EP3C55是Altera公司低成本、低功耗的CycloneⅢ系列FPGA器件,該器件具有5.5萬(wàn)個(gè)IE邏輯單元,2.4 MB的嵌入式RAM資源和312個(gè)硬件乘法器[2]。

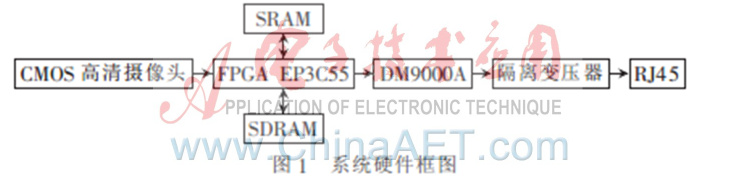

在本設(shè)計(jì)中,EP3C55控制整個(gè)系統(tǒng)的運(yùn)行。EP3C55首先需要完成對(duì)DM9000A的初始化。完成對(duì)CMOS攝像頭的初始化,然后啟動(dòng)圖像采集,對(duì)圖像數(shù)據(jù)進(jìn)行JPEG壓縮,再通過DM9000A發(fā)送至PC,同時(shí)DM9000A還接收從PC發(fā)送過來(lái)的控制數(shù)據(jù)幀,由FPGA負(fù)責(zé)對(duì)數(shù)據(jù)進(jìn)行解析并進(jìn)行相應(yīng)的控制操作,系統(tǒng)的硬件設(shè)計(jì)框圖如圖1所示。

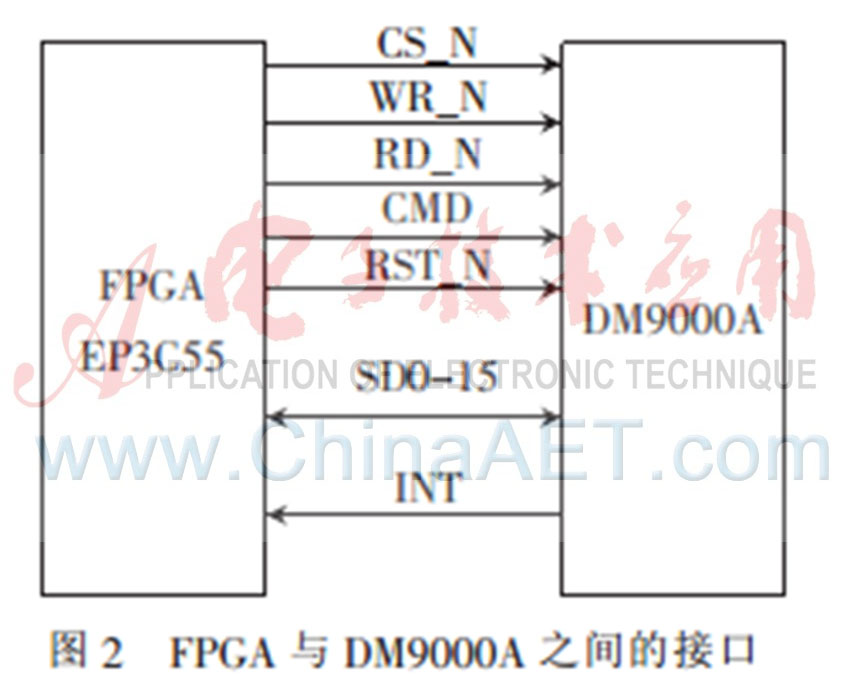

系統(tǒng)中FPGA與DM9000A的接口如圖2所示,DM9000A采用16位總線操作模式,SD0~SD15、CMD、INT、IOR、IOW均與FPGA的通用I/O口相連。

2 對(duì)FPGA操作DM9000A的改進(jìn)

2.1 Nios CPU與硬件模塊切換操作DM9000A

本設(shè)計(jì)使用DM9000A實(shí)時(shí)傳輸JPEG壓縮后的500萬(wàn)像素圖片,需要達(dá)到14幀/s的實(shí)時(shí)速度。為了保證圖像質(zhì)量,壓縮比選擇在25倍左右,通過計(jì)算可知DM9000A的速度需要達(dá)到55 Mb/s左右。

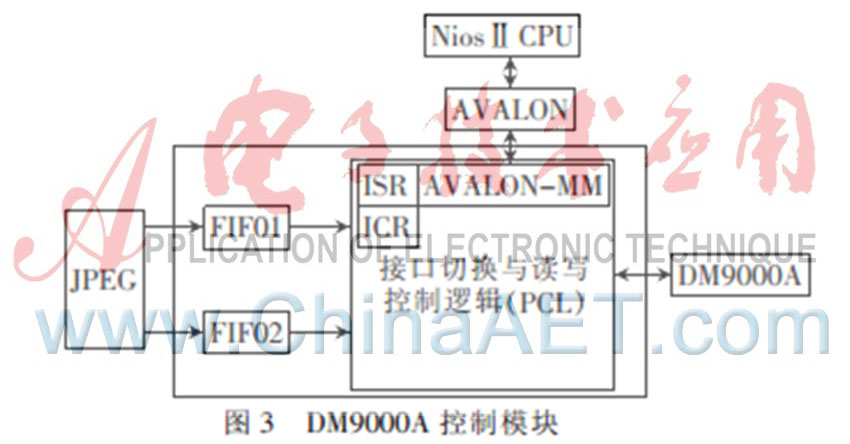

由于DM9000A操作需要一個(gè)復(fù)雜的初始化流程,因此通常在FPGA驅(qū)動(dòng)DM9000A時(shí)均采用如Nios或者M(jìn)icroblaze等FPGA內(nèi)嵌CPU的形式[3-4]。因?yàn)槭褂肍PGA內(nèi)嵌CPU,通常都是使用GPIO模擬DM9000A接口時(shí)序,對(duì)DM9000A進(jìn)行讀寫操作,DM9000A的并口最大支持100 MHz的操作速度,而嵌入CPU的GPIO通常最大頻率也只能達(dá)到1 MHz~2 MHz的頻率,最終導(dǎo)致DM9000A的網(wǎng)絡(luò)速度不會(huì)大于10 Mb/s,所以采用內(nèi)嵌CPU后,雖然提高了對(duì)DM9000A操作的靈活性,但卻大幅度降低了對(duì)DM9000A的操作速度。為了消除該瓶頸,使網(wǎng)絡(luò)速度達(dá)到要求,本文提出了如圖3所示的NiosⅡ嵌入式CPU與硬件邏輯模塊切換操作DM9000A的模式。

圖3所示模塊是一個(gè)自定義的AVALON-MM設(shè)計(jì),由NiosⅡ CPU控制該模塊的各種操作,該模塊定義了一個(gè)狀態(tài)寄存器IMAGE_STATE_REG和一個(gè)控制寄存器IMAGE_CONTROL_REG。32位狀態(tài)寄存器的[4:0]代表FIFO1深度,[5]位代表FIFO1錯(cuò)誤,[6]位代表FIFO2錯(cuò)誤,[7]位代表硬件邏輯一次傳輸完成標(biāo)志,[8:19]代表本次傳輸包序號(hào),[20:31]代表本次傳輸包的有效數(shù)據(jù)長(zhǎng)度。32位的控制寄存器的[0]位控制總線切換,[1]位控制硬件邏輯的發(fā)送使能,[2]位控制讀取FIFO1,[3]位控制復(fù)位FIFO1和FIFO2。

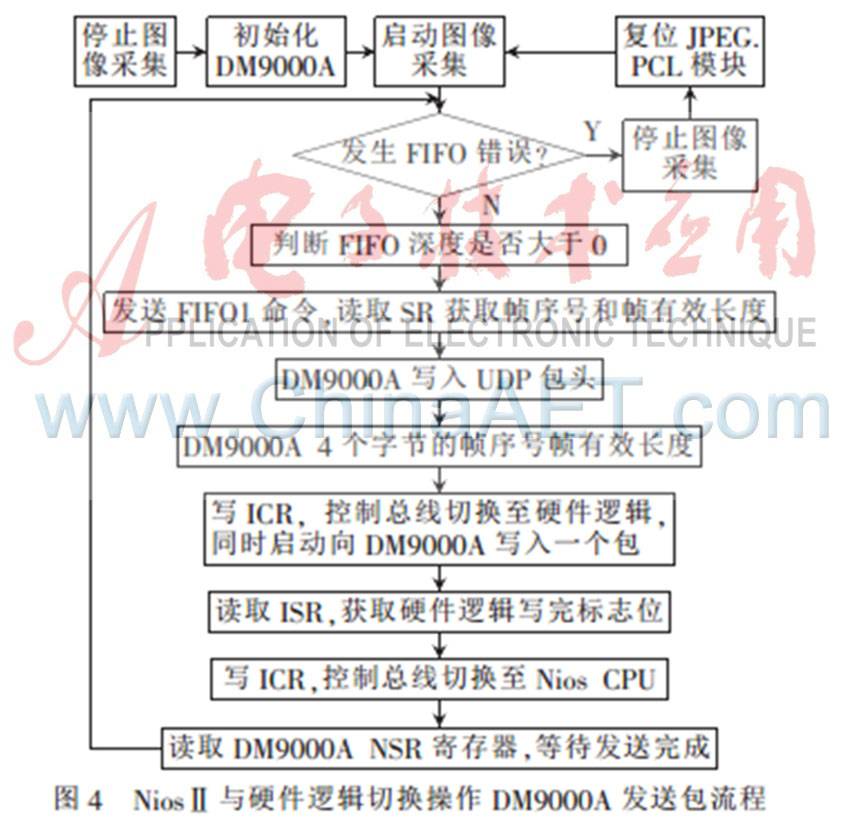

FPGA通過DM9000A發(fā)送出的圖像幀長(zhǎng)度固定為1 442 B,其中42 B為包頭,1 400 B為圖像數(shù)據(jù),而圖像數(shù)據(jù)中最開始的4個(gè)字節(jié)是從ISR讀出來(lái)的圖像幀符號(hào)和有效圖像長(zhǎng)度,JPEG壓縮模塊按照該格式對(duì)壓縮后的數(shù)據(jù)進(jìn)行打包,先往FIFO2中不斷寫入圖像數(shù)據(jù),當(dāng)圖像數(shù)據(jù)滿1 400 B時(shí)即往FIFIO1寫入一個(gè)命令數(shù)據(jù),當(dāng)每一幀圖像的最后一個(gè)包不滿1 400 B時(shí),將向FIFO2中寫0補(bǔ)足1 400 B,同時(shí)在FIFO1中寫入命令數(shù)據(jù)時(shí)指示本包中的有效圖像長(zhǎng)度。CPU初始化DM9000A以及從FIFO1、FIFO2讀出數(shù)據(jù)的具體流程如圖4所示。

使用該方法可以完全清楚因?yàn)樽x寫DM9000A接口引起的網(wǎng)絡(luò)速度瓶頸,然而使用該方法后,DM9000A最大速度還只能達(dá)到50 Mb/s左右,因此又提出如下的改進(jìn)。

2.2 發(fā)送數(shù)據(jù)包程序的優(yōu)化

通常控制DM9000A發(fā)送一包網(wǎng)絡(luò)數(shù)據(jù)的流程是首先向DM9000A緩沖區(qū)寫入數(shù)據(jù),然后寫入本次需要發(fā)送數(shù)據(jù)的長(zhǎng)度至DM9000A寄存器,再啟動(dòng)發(fā)送使能,發(fā)送下一幀數(shù)據(jù)之前首先不斷讀取DM9000A的發(fā)送完成狀態(tài)寄存器。通過分析這種流程發(fā)現(xiàn),向DM9000A緩沖區(qū)寫入數(shù)據(jù)需要大量時(shí)間,另外DM9000A發(fā)送一包數(shù)據(jù)又需要大量時(shí)間,而這兩部分時(shí)間又是完全不重疊的,由此才導(dǎo)致DM9000A速度最大只能達(dá)到50 Mb/s。如何進(jìn)一步提高DM9000A的網(wǎng)絡(luò)速度?通過仔細(xì)查看DM9000A的數(shù)據(jù)手冊(cè)發(fā)現(xiàn),DM9000A支持最多在發(fā)送緩沖區(qū)存放兩幀數(shù)據(jù),DM9000A會(huì)自動(dòng)根據(jù)寫入的先后順序?qū)?shù)據(jù)幀編號(hào),同時(shí)又針對(duì)不同幀的狀態(tài)寄存器。本文發(fā)送的一個(gè)數(shù)據(jù)包長(zhǎng)度為1 400 B,發(fā)送緩沖區(qū)大小為3 KB,因此緩沖區(qū)大小滿足同時(shí)存在兩個(gè)幀的需求,本應(yīng)用中可以采用DM9000A發(fā)送數(shù)據(jù)的同時(shí)寫入數(shù)據(jù),優(yōu)化后的數(shù)據(jù)發(fā)送流程如圖5所示。

使用該優(yōu)化方法后,DM9000A的數(shù)據(jù)發(fā)送帶寬可以穩(wěn)定達(dá)到75 Mb/s,滿足了本設(shè)計(jì)對(duì)網(wǎng)絡(luò)帶寬的需求。

系統(tǒng)采用Altera FPGA EP3C55控制DM9000A以太網(wǎng)控制器實(shí)現(xiàn)壓縮圖像的以太網(wǎng)傳輸,創(chuàng)新性地提出了采用FPGA內(nèi)嵌CPU與硬件邏輯交替控制DM9000A的方式來(lái)提高DM9000A的網(wǎng)絡(luò)帶寬,另外還通過優(yōu)化DM9000A的軟件程序,使得FPGA使用DM9000A發(fā)送網(wǎng)絡(luò)數(shù)據(jù)的帶寬穩(wěn)定達(dá)到75 Mb/s。本系統(tǒng)最終使得DM9000A網(wǎng)絡(luò)部分滿足高清圖像壓縮后實(shí)時(shí)傳輸?shù)男枨螅瑫r(shí)有力地拓寬了FPGA在嵌入式網(wǎng)絡(luò)設(shè)計(jì)方面的應(yīng)用范圍。

參考文獻(xiàn)

[1] DAVICOM Semiconductor Inc. DM9000A技術(shù)手冊(cè)[Z].DVICOM半導(dǎo)體有限公司,2006.

[2] Altera Corporation. CYCLONE III.技術(shù)手冊(cè)[Z].Altera Corporation,2008.

[3] 薛吳,佘勇,姚振東,等,基于MicroBlaze和DM9000A的以太網(wǎng)接口設(shè)計(jì)[J].通信技術(shù),2013,46(2):32-34.

[4] 徐洪建.基于DM9000A的網(wǎng)絡(luò)接口設(shè)計(jì)[J].現(xiàn)代電子技術(shù),2012,35(12):19-21

[5] 徐晶晶.基于FPGA的交通監(jiān)控視頻采集系統(tǒng)研究[D].大連:大連海事大學(xué),2009.