摘 要: 通過在MEMS信號處理電路中設(shè)計一個異步結(jié)構(gòu)的FIFO,可以有效地降低系統(tǒng)對MEMS的頻繁訪問。設(shè)計一個具有多種工作模式的FIFO,可以滿足一些特殊的姿態(tài)檢測需求,更好地滿足系統(tǒng)智能化操作需要。實現(xiàn)了一個具體可行的方案,可以實際應(yīng)用到各種MEMS電路模塊中。

關(guān)鍵詞: MEMS;智能終端;FIFO;同步雙端口RAM

MEMS傳感器是采用微電子和微機械加工技術(shù)制造出來的新型傳感器。目前,加速度計已普遍用于智能終端(如智能手機)中,未來幾年,陀螺儀也將普遍應(yīng)用到智能終端中。同時,組合傳感器,如3軸加速度計+3軸磁力計,3軸加速度計+3軸陀螺儀,甚至9軸組合傳感器未來都會得到廣泛應(yīng)用,相應(yīng)地也會帶來數(shù)據(jù)處理量的增加。目前的加速度計、陀螺儀和磁力計等MEMS電路的數(shù)據(jù)輸出速率一般在幾赫茲到幾百赫茲之間。主系統(tǒng)處理單元一般通過串行通信接口I2C或者SPI訪問MEMS電路來獲取數(shù)據(jù),除了需要實時響應(yīng)的一些數(shù)據(jù)以外,主系統(tǒng)單元有時可能不希望頻繁地用串行接口去檢測MEMS電路狀態(tài),看內(nèi)部數(shù)據(jù)是否已經(jīng)準備好,然后讀取有效數(shù)據(jù),因為這樣會降低整個系統(tǒng)的工作效率。對于類似于智能手機的智能終端而言,隨著功能越來越強大,系統(tǒng)處理的任務(wù)也越來越多,如何平衡將是一個問題。

針對上述情況,本文設(shè)計了一個48 bit數(shù)據(jù)寬度、64級存儲深度的異步FIFO(First In First Out),可以有效解決主系統(tǒng)單元頻繁訪問MEMS電路的問題。這個FIFO具有旁路模式、連續(xù)模式、先入先出模式和中斷模式4種工作模式,在中斷模式下,通過設(shè)置不同的條件,可以在不需要主系統(tǒng)單元干涉的情況下自動抓取一些特殊狀態(tài)的數(shù)據(jù)。這樣可以節(jié)省很多系統(tǒng)資源。

1 FIFO系統(tǒng)設(shè)計

傳統(tǒng)異步FIFO[1-2]采用觸發(fā)器同步異步輸入信號來降低出現(xiàn)亞穩(wěn)態(tài)的幾率,然后地址通過格雷碼編碼方式來消除地址多位變化導(dǎo)致的空滿狀態(tài)誤判,需要用到真正的雙端口RAM。采用觸發(fā)器同步雖然可以降低亞穩(wěn)態(tài)的幾率,但也帶來了時序分析和綜合后仿真的難點。格雷碼帶來了設(shè)計的復(fù)雜性,可以通過時序邏輯的設(shè)計方式,在布局布線時插入時鐘樹來避免空滿狀態(tài)的不定。同時真正的雙端口RAM不是每個集成電路工藝線都支持的,采用偽雙端口RAM更實際,也能使設(shè)計適用范圍更廣泛。

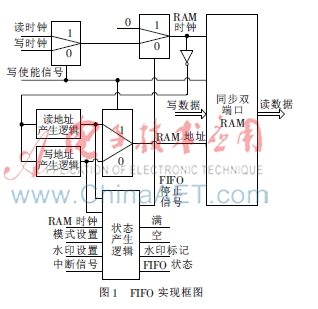

整個系統(tǒng)實現(xiàn)還要包括I2C和SPI接口模塊、信號處理模塊以及中斷檢測模塊,本文僅僅描述FIFO模塊。FIFO模塊的實現(xiàn)框圖如圖1所示。寫時鐘是MEMS數(shù)據(jù)采樣時鐘,讀時鐘是串口I2C或者SPI讀數(shù)據(jù)時鐘。為了消除讀寫同時進行產(chǎn)生的沖突,增加了一個寫使能信號,其與寫時鐘同時由內(nèi)部邏輯產(chǎn)生,寫時鐘比讀時鐘優(yōu)先級高。這樣可能會引入一個問題,那就是讀寫恰好同時進行的時候,讀的數(shù)據(jù)依然是上一個數(shù)據(jù),但可以設(shè)置為先入先出模式,數(shù)據(jù)滿了之后不再更新,這樣就不會有這個問題。模式設(shè)置和水印閾值設(shè)置通過串口I2C或者SPI寫入。同步雙端口RAM采用SMIC 0.18 m工藝Memory Compiler綜合出來的64×48 bit的IP模塊,這是一個偽雙端口RAM,讀寫時鐘是共用的。48 bit數(shù)據(jù)寬度可以同時存儲3個軸的MEMS檢測數(shù)據(jù),每個軸16 bit數(shù)據(jù)寬度,基本可以滿足目前的MEMS精度要求。

2 功能模塊設(shè)計

2.1 讀地址產(chǎn)生邏輯

讀地址產(chǎn)生邏輯,根據(jù)工作模式和FIFO的狀態(tài),生成讀地址指針。假如讀時鐘有效,并且FIFO不為空,則讀地址加1,假如FIFO為空,則讀地址保持不變。在連續(xù)工作模式下,由于數(shù)據(jù)不斷滾動更新,當數(shù)據(jù)滿的情況下,假如寫入有效,讀地址加1,保證讀地址指針指向最先寫入的數(shù)據(jù)地址。

2.2 寫地址產(chǎn)生邏輯

假如寫入有效,寫地址指針自動加1。通過控制RAM時鐘,在先入先出模式下,假如FIFO滿,終止寫入新的數(shù)據(jù)到RAM中,因此寫地址指針不再更新,除非重新使能整個FIFO模塊。

2.3 狀態(tài)生成邏輯

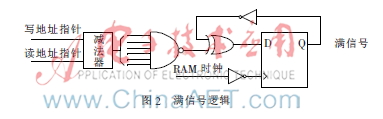

FIFO的狀態(tài)可以直接用寫地址指針減去讀地址指針來獲得,但也需要考慮到當FIFO滿的時候,讀地址指針和寫地址指針是指向同一個地址的,這時候減出來數(shù)據(jù)就為0了。因此需要增加中間寄存器,在未滿的時候輸出減法器的數(shù)值,在滿的時候輸出全1數(shù)值。滿和空狀態(tài)信號、水印標記信號和FIFO停止信號都由時序邏輯生成,滿信號邏輯電路圖如圖2所示,用RAM時鐘的反相信號來觸發(fā)。水印標記可以通過設(shè)置水印的閾值來獲得,閾值范圍可以是0~63。當FIFO的狀態(tài)值超過設(shè)置的閾值,就產(chǎn)生水印標記中斷;當FIFO的狀態(tài)小于設(shè)置的閾值,水印標記中斷就清除,這可以讓主系統(tǒng)根據(jù)應(yīng)用場合靈活選擇。FIFO停止信號有兩種情況,在先入先出模式下,滿了之后產(chǎn)生FIFO停止信號,RAM數(shù)據(jù)停止更新;在中斷模式下,在中斷信號產(chǎn)生之前,不產(chǎn)生FIFO停止信號,中斷信號產(chǎn)生之后,根據(jù)滿狀態(tài)信號產(chǎn)生FIFO停止信號。

3 工作模式

3.1 旁路模式

在旁路模式下,復(fù)位信號有效,F(xiàn)IFO不工作,主系統(tǒng)單元直接讀出ADC輸出的數(shù)據(jù)。

3.2 連續(xù)模式

在連續(xù)模式下,數(shù)據(jù)在FIFO里面不斷更新,相應(yīng)地,讀地址指針和寫地址指針也不斷滾動更新,讀地址指針指向最先輸入的RAM地址。在連續(xù)模式下,假如數(shù)據(jù)滿了之后,寫時鐘有效,讀地址指針和寫地址指針需要同時加1,因為最先的數(shù)據(jù)已經(jīng)被覆蓋了。同時在寫時鐘無效的時候,讀時鐘有效,讀地址指針也要加1。

3.3 先入先出模式

在先入先出模式下,數(shù)據(jù)填充滿了就自動終止,產(chǎn)生滿中斷信號。在沒有讀時鐘的情況下,最終讀地址指針和寫地址指針將會同時指向地址0。相應(yīng)地,在未充滿的情況下,假如讀時鐘有效,最終讀地址指針和寫地址指針會同時指向中間某一個地址。

3.4 中斷模式

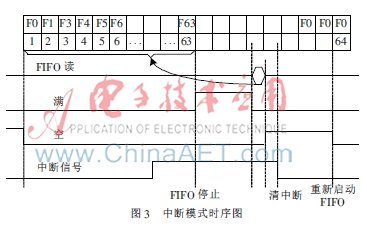

在中斷模式下,數(shù)據(jù)先是以連續(xù)模式工作,假如中斷信號有效,進入先入先出模式,數(shù)據(jù)填充滿了就自動終止。工作時序圖如圖3所示,數(shù)據(jù)在未填充滿的情況下,產(chǎn)生中斷信號,數(shù)據(jù)填充滿了就產(chǎn)生終止信號,滿中斷信號置1,數(shù)據(jù)開始讀出之后,滿中斷信號清0,當數(shù)據(jù)完全讀完后,空中斷信號置1。假如FIFO需要重復(fù)上面的工作流程,需要清中斷,重新啟動FIFO,在數(shù)據(jù)開始重新寫入FIFO時,空中斷信號清0。

與傳統(tǒng)的異步FIFO不同,本文實現(xiàn)了一個更加簡單、并且實際可行的FIFO結(jié)構(gòu),操作靈活可靠。通過在MEMS信號處理電路中加入異步FIFO設(shè)計,可以更好地滿足系統(tǒng)對低功耗和操作靈活性的需求。通過DC綜合并流片驗證,該FIFO電路已經(jīng)應(yīng)用到多個MEMS電路產(chǎn)品中,得到很好的效果。特別對于未來MEMS組合傳感器、數(shù)據(jù)量的增加以及特殊姿態(tài)的處理,引入更多靈活性的FIFO將會帶來更多的優(yōu)越性。

參考文獻

[1] 于海,樊曉椏.基于FPGA異步FIFO的研究與實現(xiàn)[J].微電子學(xué)與計算機,2007(3):210-213.

[2] 劉祥遠,陳書明.一種高性能的異步FIFO結(jié)構(gòu)[J].電子學(xué)報,2007(11):2098-2104.