文獻標識碼: A

文章編號: 0258-7998(2015)02-0123-04

0 引言

隨著對DPA攻擊研究的不斷深入,越來越多的攻擊方法被提出。1999年P(guān)aul Kocher等人在CRYPTO會議上提出了差分功耗分析(Differential Power Analysis,DPA)的攻擊方法[1]。該方法的提出,使得智能卡芯片的安全性受到了極大挑戰(zhàn)[2]。Paul Kocher等人對接近50款產(chǎn)品進行DPA攻擊,均可成功破解密鑰。同時,提出了高階DPA攻擊方法,但并沒有給出攻擊實例。2000年Thomas S. Messerges應用二階DPA攻擊方法,針對實際芯片成功破解了密鑰[3]。接下來的十幾年,很多學者投入到了DPA攻擊方法的研究工作中,有力地促進了該領(lǐng)域的發(fā)展。但是,從上述調(diào)研的情況可以看出,雖然對于DPA攻擊的研究成果很多,但主要集中在方法的改進和優(yōu)化上,對于如何通過提升DPA攻擊方法,從而破解待攻擊設(shè)備的密鑰,在該領(lǐng)域的研究較少。實際上,攻擊方法固然重要,但實驗環(huán)境對于攻擊成功與否也起著舉足輕重的作用。如果實驗環(huán)境設(shè)置不當,可能會導致采集不到有用信號,或者采集到的信號噪聲較大,使得原本可以攻擊成功的設(shè)計也無法攻擊。實驗環(huán)境包含眾多因素,本文主要關(guān)注的是采集環(huán)境,在不同采集參數(shù)情況下,如何影響DPA攻擊結(jié)果。

1 采集參數(shù)概述

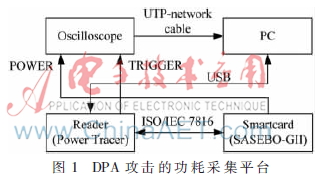

為了分析DPA攻擊中采集參數(shù)如何選擇,首先需要了解DPA攻擊。DPA攻擊是最常用的側(cè)信道攻擊手段之一,它不需要攻擊者了解被攻擊芯片的具體算法實現(xiàn),僅需已知采用哪種算法,并可以采集該算法運行時的功耗信息,即可開展攻擊。在DPA攻擊流程中,對于功耗曲線的采集是本文分析對象,典型的DPA攻擊功耗采集平臺如圖1所示。

采集過程是指示波器采集功耗這一過程,本文主要分析如何選擇該過程中的采集參數(shù)。

2 采集參數(shù)影響分析

DPA攻擊的對象一般為數(shù)字電路,根據(jù)邏輯功能的不同特點,可以分成兩大類,一類為組合邏輯電路,另一類為時序邏輯電路[4]。對DPA攻擊而言,在采集參數(shù)不同時,攻擊組合邏輯電路和時序邏輯電路的結(jié)果也有所不同。下面針對采樣頻率、示波器垂直分辨率、低通濾波3個采集參數(shù),對此問題進行分析。

2.1 采樣頻率對攻擊的影響

根據(jù)奈奎斯特定律,采樣頻率必須大于被采樣信號帶寬的兩倍。因此,針對不同的攻擊對象,采樣頻率也有所不同。開展DPA攻擊需要采集電路的功耗信號,為了滿足奈奎斯特定律,首先需要了解該功耗信號的頻率。根據(jù)時序邏輯和組合邏輯的信號特性,組合邏輯的高頻信號較多,應采用較高的采樣頻率才能保證采集到完整信號;而時序邏輯的頻率較低,根據(jù)系統(tǒng)時鐘頻率的具體大小,采用兩倍系統(tǒng)時鐘頻率的采樣頻率采集信號即可。這樣才能保證采集信號的完整性,有利于提高攻擊效果。

2.2 垂直分辨率對攻擊的影響

垂直分辨率用比特來表示,對于一個8 bit的示波器而言,意味著將信號在垂直方向上分成28份;同理,對于12 bit的示波器,則將信號分成212份。因此,垂直分辨率越高,則示波器上的波形中可以看到的信號細節(jié)越明顯。在攻擊時序邏輯電路時,雖然12 bit示波器比8 bit示波器采集到的信號更加細微,但是對于時序邏輯電路的攻擊并未利用這些較細微的信號,因此,二者差異不大。而攻擊組合邏輯時,需要利用信號的細微變化,理論上,12 bit示波器比8 bit示波器更有利于攻擊。

2.3 低通濾波對攻擊的影響

濾波器的功能就是允許某一部分頻率的信號順利通過,而另外一部分頻率的信號則受到較大抑制,它實質(zhì)上是一個選頻電路。濾波器中,把信號能夠通過的頻率范圍稱為通頻帶或通帶;反之,信號受到很大衰減或完全被抑制的頻率范圍稱為阻帶。低通濾波器就是允許低于截止頻率的信號通過, 但高于截止頻率的信號不能通過的電子濾波裝置。

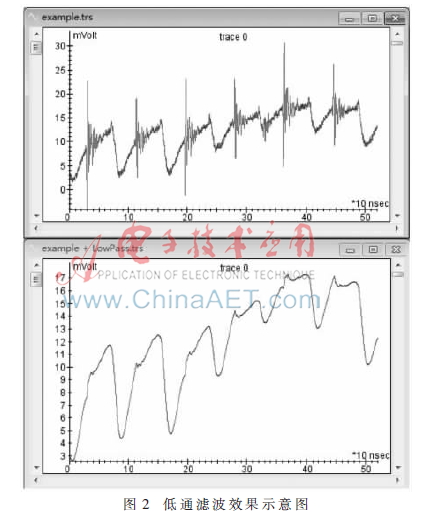

低通濾波效果示意圖如圖2所示,上圖為不加低通濾波器采集的原始信號,可以看到信號內(nèi)包含高頻噪聲及頻率較高的毛刺信號;下圖為加入低通濾波器后再次采集相同信號的波形,可以看到采集的信號中已去除了高頻噪聲,曲線與之前相比更加光滑。如果電路的系統(tǒng)時鐘頻率是低于截止頻率的信號,那么,在采集曲線時加入低通濾波器可以更加有效地去除高頻噪聲,使采集到的信號信噪比更高,更有利于開展DPA攻擊。

3 攻擊實驗

3.1 攻擊對象及實驗環(huán)境描述

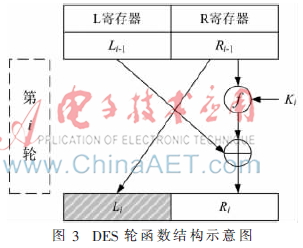

下面開展實際的攻擊實驗,對上述分析的結(jié)論進行驗證。采集選用Lecroy示波器,型號為Wave Runner 66ZI,采集環(huán)境如圖1所示。選擇Riscure公司的Power Tracer作為讀卡器與智能卡通信,該設(shè)備可根據(jù)APDU命令自動向示波器發(fā)送觸發(fā)信號,攻擊對象基于SASEBO-GII開發(fā)板實現(xiàn),開發(fā)板模擬智能卡功能,完成加解密運算,示波器采集加解密過程開發(fā)板上的功耗信息。實驗的攻擊對象是基于SASEBO-GII開發(fā)板實現(xiàn)的無防護DES設(shè)計,時鐘頻率為12 MHz。該DES設(shè)計為64 bit明文、64 bit密鑰的單DES運算。輪函數(shù)的結(jié)構(gòu)如圖3所示,將初始明文的高低32 bit分別寫入L寄存器和R寄存器,執(zhí)行16輪迭代,最后將左右寄存器互換即可得到密文。

為何選擇該設(shè)計作為攻擊對象,主要有以下原因:(1)該設(shè)計沒有防護,攻擊所需的曲線條數(shù)少,有利于提高實驗效率;(2)FPGA的噪聲較小,對于采集到的功耗曲線可以直接開展攻擊,無需進行信號處理操作;(3)對于DES算法,F(xiàn)PGA設(shè)計和ASIC設(shè)計在側(cè)信道攻擊方面具有一致性,因此,以FPGA為例得到的結(jié)論,同樣適用于ASIC。

開展實驗的思路是在分析某一參數(shù)對攻擊影響時,固定其他采集參數(shù),保證其他環(huán)境因素均一致,改變該參數(shù)的設(shè)置,采用相同的攻擊方法,每種設(shè)置攻擊5組曲線,攻擊結(jié)果取5次的平均值。

3.2 采樣頻率比較實驗

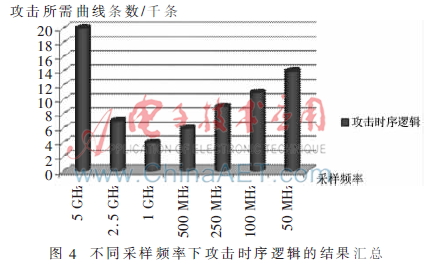

首先,比較不同采樣頻率下采集到的曲線對DPA攻擊影響。當DPA攻擊選取的中間值對應電路中的時序邏輯時,攻擊結(jié)果如圖4所示。

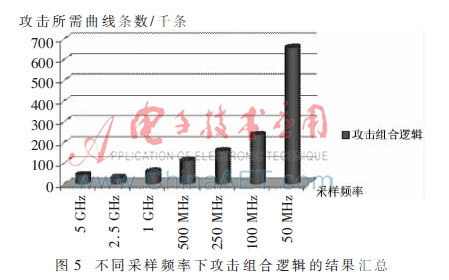

從圖4可以看出,針對不同采樣頻率下采集到的曲線攻擊時序邏輯電路時,1 GHz和500 MHz采樣頻率下的攻擊結(jié)果較好。由于時序邏輯電路的翻轉(zhuǎn)頻率與電路的時鐘頻率相同,本實驗的攻擊對象時鐘頻率為12 MHz,因此,如果采用較低的采樣頻率,對采集信號的完整性不如較高采樣頻率,對攻擊有一定影響。但是如果采用過高的采樣頻率,例如5 GHz,會引入較多噪聲,同樣不利于攻擊。綜上,攻擊時序邏輯電路時,采用1 GHz或者500 MHz的采樣頻率最有利于攻擊。當DPA攻擊選取的中間值對應電路中的組合邏輯時,攻擊結(jié)果如圖5所示。

從圖5中可以看出,較高的采樣頻率更有利于攻擊。由于電路中組合邏輯電路的翻轉(zhuǎn)頻率較高,如果采用較低的采樣頻率不能將組合邏輯電路的功耗信號完整捕捉,因此需要采用較高的采樣頻率。從攻擊結(jié)果看,當攻擊組合邏輯時,應采用2.5 GHz或者5 GHz的采樣頻率采集曲線。

3.3 垂直分辨率比較實驗

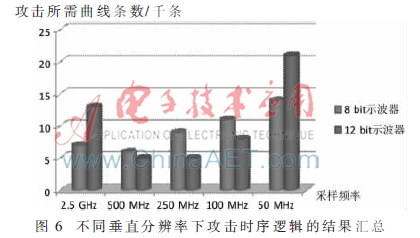

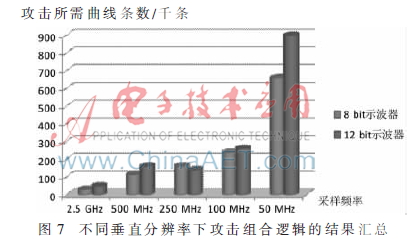

接下來,比較在不同的示波器垂直分辨率下采集到的曲線對DPA攻擊影響。圖6、圖7分別是利用8 bit示波器和12 bit示波器采集曲線攻擊時序邏輯和組合邏輯的攻擊結(jié)果。

無論攻擊時序邏輯還是組合邏輯,從匯總結(jié)果中均不能明顯看出兩種垂直分辨率的示波器哪種更有利于攻擊。當信號的幅值變化比較細微時,12 bit示波器能更好地體現(xiàn)其優(yōu)勢。但是對于目前的攻擊方法,沒有利用到信號中如此細小的差別。

3.4 低通濾波比較實驗

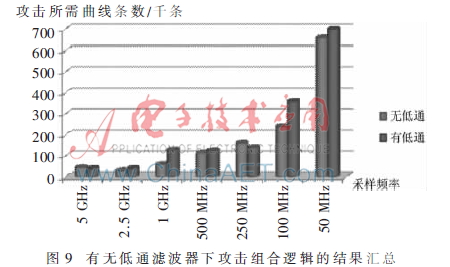

最后,比較在低通濾波對DPA攻擊影響。本實驗以81 MHz低通濾波器為例進行攻擊實驗。圖8、圖9分別是在有無低通濾波器情況下,攻擊時序邏輯和組合邏輯的結(jié)果匯總。

從匯總結(jié)果中可以看出,當攻擊時序邏輯時,使用低通濾波器的攻擊結(jié)果更優(yōu)于未使用低通濾波器。由于攻擊時序邏輯時,主要利用翻轉(zhuǎn)時鐘頻率較低的寄存器功耗,如果采用低通濾波器,可以濾除高頻噪聲,減少噪聲對攻擊的影響,因此,采用低通濾波器攻擊時序邏輯會得到較好的攻擊結(jié)果。當攻擊組合邏輯時,不使用低通濾波器的攻擊結(jié)果略優(yōu)。由于攻擊組合邏輯時,主要利用組合邏輯翻轉(zhuǎn)產(chǎn)生的功耗,而組合邏輯翻轉(zhuǎn)頻率較高,如果采用低通濾波器不僅濾除高頻噪聲,同時可能會將有用的高頻信號濾除,影響攻擊結(jié)果。因此,當攻擊組合邏輯時,不采用低通濾波器效果更佳。

4 結(jié)論

根據(jù)上述理論分析并結(jié)合實驗結(jié)果,可以得到以下結(jié)論:(1)關(guān)于采樣頻率:當攻擊時序邏輯電路時,采樣頻率不宜過高,在本文的研究范圍內(nèi),采用500 MHz或者1 GHz的采樣頻率采集曲線最佳;當攻擊組合邏輯時,可以選取較高的采樣頻率,采用2.5 GHz或者5 GHz的采樣頻率采集曲線最佳。(2)關(guān)于示波器垂直分辨率:基于目前的攻擊方法和文中的攻擊對象,采用8 bit示波器或者12 bit示波器采集曲線對攻擊結(jié)果基本沒有影響。(3)關(guān)于低通濾波器:當攻擊時序邏輯時,應采用低通濾波器;當攻擊組合邏輯時,不采用低通濾波器的攻擊效果更佳。

本文針對采樣頻率、示波器垂直分辨率、低通濾波3個采集參數(shù)進行分析,比較參數(shù)設(shè)置不同時對DPA攻擊的影響。文中首先從理論角度進行分析,根據(jù)各個采集參數(shù)的特性,分析其對DPA攻擊可能產(chǎn)生的影響。接下來開展實際的攻擊實驗,對理論分析結(jié)果進行驗證。但是目前的結(jié)論僅針對FPGA實現(xiàn)的DES設(shè)計,對于其他算法以及其他實現(xiàn)形式的設(shè)計是否適用,還需要開展更多的實驗進行分析驗證。這也是下一步的研究方向,針對其他算法比較不同采集參數(shù)對DPA攻擊的影響,從而得到適用范圍更廣、普適性更強的結(jié)論,通過優(yōu)化采集參數(shù)配置,提高DPA攻擊效率。

參考文獻

[1] KOCHER P,JAFFE J,JUN B.Differential power analysis[C].Proceedings of Advances in Cryptology-CRYPTO′99,Springer-Verlag,1999:388-397.

[2] MANGARD S,OSWALD E,POPP T.Power analysis attacks:Revealing the secrets of smart cards[C].Springer,2007.

[3] MESSERGES T S.Using second-order power analysis to attack DPA resistant software[C].Cryptographic Hardware and Embedded Systems(CHES),2000:238-251.

[4] KANG S M,LEBLEBICI Y.CMOS digital integrated circuits:Analysis and design third edition[M].McGraw-Hill PublishingCo.,2009.