文獻(xiàn)標(biāo)識碼: A

文章編號: 0258-7998(2014)11-0039-04

0 引言

在無線通信系統(tǒng)、高清電視以及其他領(lǐng)域,寬帶低功耗ΣΔ模數(shù)轉(zhuǎn)換器越來越受到人們的歡迎[1]。對于無線窄帶的中頻無線通信系統(tǒng),帶通的ΣΔ調(diào)制器是高精度A/D轉(zhuǎn)換器的最佳選擇[2]。目前關(guān)于ΣΔ帶通調(diào)制器的研究工作大多數(shù)都是集中于傳統(tǒng)結(jié)構(gòu),然而低失真結(jié)構(gòu)能夠?qū)崿F(xiàn)更優(yōu)越的性能。因為低失真結(jié)構(gòu)采用一個信號前饋通路,使得諧振器只處理量化噪聲,這樣就能獲得更高的線性度。另外低失真結(jié)構(gòu)對于諧振器的非線性較傳統(tǒng)結(jié)構(gòu)而言也不敏感[3]。在調(diào)制器電路中采用雙采樣技術(shù)能夠有效地增加系統(tǒng)的過采樣率(OSR),同時并不增加時鐘頻率,這樣能夠降低對運(yùn)算放大器建立時間的要求。目前關(guān)于低失真結(jié)構(gòu)的低通調(diào)制器的研究工作開展較多,而對中頻帶通調(diào)制器而言,報道低失真結(jié)構(gòu)的文獻(xiàn)還較少。低失真的帶通ΣΔ調(diào)制器結(jié)構(gòu)首先在參考文獻(xiàn)[3]中被提出來,但是其并沒有給出其具體實(shí)現(xiàn)方式;參考文獻(xiàn)[4]對這種低失真結(jié)構(gòu)進(jìn)行了研究,但是并沒有對其非理想因素進(jìn)行分析。本文基于一種雙采樣雙延遲諧振器,提出一種低失真中頻帶通sigma-delta調(diào)制器電路,分析了其非理想特性并在MATLAB的Simulink里進(jìn)行建模。通過對比行為級模型仿真結(jié)果和電路的后仿真結(jié)果,驗證了所建立模型的準(zhǔn)確性。本文也對帶通調(diào)制器的穩(wěn)定性進(jìn)行了分析,并給出了電路圖和版圖后仿真結(jié)果。

1 主要非理想特性分析

1.1 模擬開關(guān)熱噪聲和非線性

模擬開關(guān)在導(dǎo)通時會形成一個導(dǎo)通電阻,這個導(dǎo)通電阻將會產(chǎn)生熱噪聲,且會被開關(guān)電容電路采樣到采樣電容上,對輸出信號產(chǎn)生影響。當(dāng)開關(guān)的導(dǎo)通電阻為Ron時,模擬開關(guān)的噪聲功率可以表示為[5]:

式中,Cs為采樣電容值,k為波耳茲曼常數(shù),T為絕對溫度。其非理想模型如圖1所示。

1.2 運(yùn)放熱噪聲

在調(diào)制器系統(tǒng)中,運(yùn)算放大器的噪聲是系統(tǒng)的主要噪聲來源之一。不同于低通調(diào)制器的低頻應(yīng)用,中頻調(diào)制器可以不考慮運(yùn)放的1/f噪聲對系統(tǒng)的影響。常見的運(yùn)放熱噪聲模型如圖2所示。

1.3 諧振器非理想模型

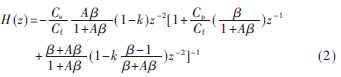

諧振器的非理想特性主要由運(yùn)放的有限直流增益、運(yùn)放有限增益帶寬、寄生電容等因素引起。本設(shè)計的諧振器非理想傳輸函數(shù)可以用下式表示[6]:

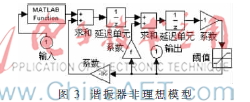

其中,Cs為諧振器的采樣電容,Cf為諧振器的積分電容,Cp為運(yùn)放的輸入端寄生電容,A為運(yùn)放的直流增益,為反饋系數(shù),k為運(yùn)放的有限增益帶寬引起的非理想因子。圖3的非理想諧振器模型中包含了上述的非理想因素。

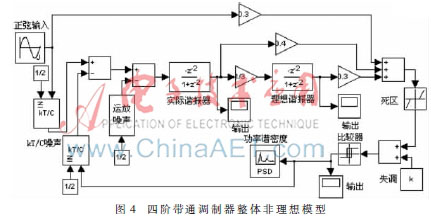

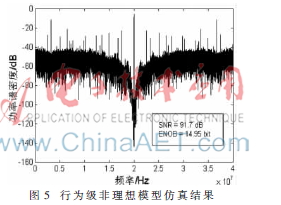

基于低失真帶通調(diào)制器的結(jié)構(gòu)和上面分析的主要非理想特性,建立圖4中的調(diào)制器整體行為級模型,其中還包含了量化器的失調(diào)和死區(qū)特性,以便更準(zhǔn)確地模擬中頻帶通調(diào)制器的行為,為后續(xù)設(shè)計提供指導(dǎo)。當(dāng)采樣頻率為80 MHz、輸入信號20 MHz、信號幅度為-0.915 dBFS時,行為級仿真結(jié)果如圖5所示,顯示該調(diào)制器實(shí)現(xiàn)了91.7 dB的信噪比(SNR)。

2 穩(wěn)定性分析

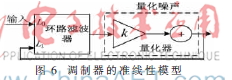

在較低的過采樣率的情況下,如果提高調(diào)制器的階數(shù),相對而言能夠獲得較高的SNR。但是在實(shí)際設(shè)計中,高階的調(diào)制器系統(tǒng)會存在穩(wěn)定性問題。由于量化器的增益是隨輸入信號變化的,所以調(diào)制器實(shí)際上是一種非線性系統(tǒng)。圖6是準(zhǔn)線性的調(diào)制器模型,其中量化器的增益k隨著輸入信號幅度變化而變化,這樣量化器輸出就等效成一個隨輸入信號可變的因子與量化噪聲之和。

圖4中的帶通調(diào)制器的反饋環(huán)路函數(shù)如式(3)所示,因此可以寫出準(zhǔn)線性模型下的量化噪聲傳輸函數(shù),如式(4)所示:

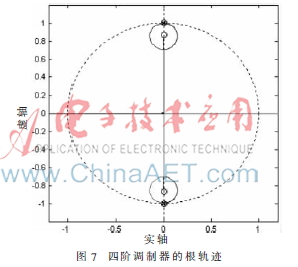

由于量化器的增益是隨著輸入信號幅度的變化而變化的,所以量化器增益的變化會改變系統(tǒng)噪聲傳輸函數(shù)的極點(diǎn)的位置。對于穩(wěn)定的系統(tǒng),極點(diǎn)必須在單位圓內(nèi)部。分析系統(tǒng)的根軌跡一般被用來作為判定系統(tǒng)穩(wěn)定性的一種手段,可以在MATLAB中求出該帶通調(diào)制器的NTF的根軌跡,如圖7所示。當(dāng)k值增大時極點(diǎn)會從實(shí)軸上往單位圓外移動,如上文所述,調(diào)制器能恢復(fù)穩(wěn)定狀態(tài);當(dāng)k值減小時,極點(diǎn)始終處于單位圓內(nèi)。因此可以看出,本設(shè)計的帶通調(diào)制器是無條件穩(wěn)定的。

3 電路設(shè)計和版圖后仿真

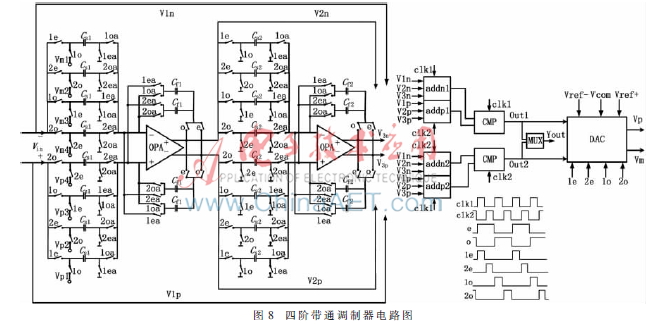

圖8中是基于一個雙采樣技術(shù)的全差分四階帶通ΣΔ調(diào)制器電路。該電路由兩級諧振器、兩路求和電路、兩路比較器以及一位DAC等組成。圖4中的前級比例系數(shù)由諧振器的采樣電容值和積分電容值的比值確定,后級系數(shù)由求和電路的電容比例確定。該調(diào)制器電路的等效采樣時鐘頻率是信號頻率的4倍。諧振器電路在clk1高電平和clk2的高電平分別進(jìn)行采樣和積分。在4項時鐘1e、2e、1o、2o控制下,實(shí)現(xiàn)了兩個采樣周期的延遲,同時實(shí)現(xiàn)了兩次采樣。

由于諧振器在clk1和clk2都進(jìn)行采樣和積分,故降低了一半的采樣頻率,而等效采樣頻率不變。這樣對諧振器電路的建立時間要求就降低了很多,降低了對運(yùn)放的帶寬要求。另外諧振器的輸出擺幅可以通過改變采樣電容和積分電容值的大小來降低,這雖然降低了系統(tǒng)的線性度,但是可以進(jìn)一步降低系統(tǒng)的功耗。該調(diào)制器電路的采樣電容引入的kT/C噪聲是系統(tǒng)的主要噪聲來源。為避免量化誤差,同時考慮到運(yùn)放負(fù)載對功耗和速度的影響,取CS1=0.8 pF。由于后級電路的噪聲可以通過前級抑制,所以第二級諧振器的采樣電容可以大大減小,取CS2=0.2 pF,因此第二級諧振器的負(fù)載電容大大減小,功耗得到優(yōu)化。諧振器的積分電容可以根據(jù)行為級確定的比例系數(shù)來確定。求和電路采用常見的無源開關(guān)電容求和電路來實(shí)現(xiàn),以降低芯片面積,減小功耗。求和電容分別為0.3 pF、0.4 pF、0.3 pF。兩路求和電路的輸出分別送給比較器電路,最后由選擇器將兩路位流合并為一路輸出。

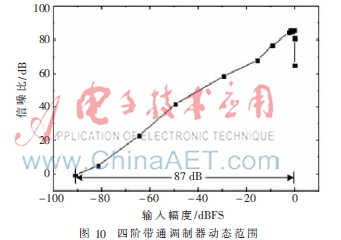

在TSMC 0.18 m工藝下對該全差分調(diào)制器電路進(jìn)行版圖設(shè)計。該調(diào)制器工作在80 MHz的等效采樣頻率下,當(dāng)輸入信號頻率20 MHz、幅度約為-0.915 dBFS時,其輸出位流在MATLAB里經(jīng)過計算繪制的頻譜圖和信號帶寬內(nèi)細(xì)節(jié)圖如圖9所示,SNR為85.5 dB。版圖的后仿真包含了運(yùn)放的有限增益帶寬、非理想開關(guān)、寄生效應(yīng)、建立誤差等非理想效應(yīng),其結(jié)果與行為級建模相比,SNR下降了約6 dB。這可能是由于版圖的不對稱和工藝誤差導(dǎo)致的,但版圖的后仿真結(jié)果和行為級建模仿真結(jié)果基本一致,可以看出前文對調(diào)制器的非理想特性進(jìn)行的行為級建模的準(zhǔn)確性和有效性。通過改變輸入信號幅度,得到的調(diào)制器動態(tài)范圍(DR)如圖10所示,從圖中可以看出,該調(diào)制器在大信號和小信號激勵下都具有良好的穩(wěn)定性。當(dāng)輸入信號幅度增大到一定范圍,諧振器開始過載,輸出諧波失真分量增加。另外諧振器輸出過載也導(dǎo)致了諧振器的傳輸特性發(fā)生變化,從而導(dǎo)致整個調(diào)制器的信號傳輸函數(shù)發(fā)生改變,這些都會降低系統(tǒng)的線性度。從圖10中可以看出系統(tǒng)的DR約為87 dB。

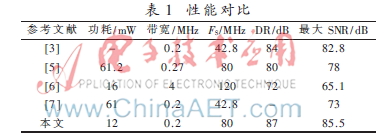

表1將本文的帶通調(diào)制器性能與參考文獻(xiàn)中的進(jìn)行了比較,可見本文設(shè)計的調(diào)制器電路具有功耗低、動態(tài)范圍大、信噪比高的特點(diǎn),適合于高性能低功耗的通信系統(tǒng)應(yīng)用。

4 結(jié)論

本文對一個四階帶通ΣΔ調(diào)制器的非理想特性進(jìn)行了分析并進(jìn)行了建模,利用根軌跡法對調(diào)制器系統(tǒng)的穩(wěn)定性做了分析。在TSMC 0.18 ?滋m工藝下完成了電路和版圖設(shè)計,通過對比版圖的后仿真結(jié)果和調(diào)制器的行為級非理想特性建模結(jié)果可以發(fā)現(xiàn)性能基本一致,說明了建立的行為級非理想模型的準(zhǔn)確性和所設(shè)計電路功能的正確性。

參考文獻(xiàn)

[1] 鄧玉清,唐寧,曹杰.高精度音頻Σ-Δ DAC的設(shè)計[J].電視技術(shù),2011,35(7):56-58.

[2] WAKI N,SATO H,HYOGO A,et al.A low-distortion two-path fourth-order bandpass delta-sigma modulator using horizontal opamp sharing[C].50th Midwest Symposiumon Circuits and Systems,2007:1372-1375.

[3] RUSU A,ISMAIL M.Low-distortion bandpass Σ-Δ modula-tor for wireless radio receivers[J].Electronical Letters,2005,41(19):1044-1046.

[4] XU H L,LIU X W,HUANG F X,et al.Low-distortion bandpass ΣΔ modulator using two-path double-sampling technique[J].IEICE Electronics Express,2014,11(12):1-6.

[5] SUAREZ G,JIMENEZ M,F(xiàn)ERNANDEZ F O.Behavioral modeling methods for switched-capacitor ΣΔ modulators[J].IEEE Trans. on Circuits and Systems,2007,54(6):1236-1244.

[6] TEMES G C.Finite amplifier gain and bandwidth effects in switched-capacitor filters[J].IEEE Journal of Solid-State Circuits,1980,15(3):358-361.

[7] 陳凱,張文俊,余志平.Σ-Δ調(diào)制器的非理想特性建模與驗證[J].微電子學(xué)與計算機(jī),2010,27(5):5-8.