文獻標識碼: A

文章編號: 0258-7998(2014)11-0085-03

0 引言

近年來,隨著航天航空事業(yè)的不斷進步,新型的航天產(chǎn)品(如新一代航天器、運載火箭、衛(wèi)星及航天飛機等)已逐漸問世并向著自動化、智能化的方向發(fā)展,其系統(tǒng)構(gòu)成也變得多元化,對于研究和探索這些先進的技術(shù)所需要采集的參數(shù)不斷增加,因而對于數(shù)據(jù)存儲設(shè)備的存儲容量、速度、質(zhì)量、便攜性及抗沖擊能力的要求也在不斷提高[1]。高速數(shù)據(jù)存儲設(shè)備不僅在航天產(chǎn)品中扮演重要的角色,在民用航空飛機上也是必不可少的一部分,如飛行數(shù)據(jù)記錄器等[2]。

為了滿足飛行數(shù)據(jù)記錄器的高速數(shù)據(jù)存儲需求,本文采用FPGA與DSPIC30F6014A單片機相結(jié)合的方式對數(shù)據(jù)記錄器進行了設(shè)計。這種記錄器既充分發(fā)揮了FPGA并行讀寫大容量Flash數(shù)據(jù)的能力,也充分利用了DSP-IC30F6014A單片機的單指令周期和并口讀寫方式等優(yōu)越性能,通過結(jié)合高速文件管理芯片CH378和大容量Flash芯片,從而實現(xiàn)飛行數(shù)據(jù)的高速U盤存儲功能。這種設(shè)計方法可以有效地提高U盤讀寫數(shù)據(jù)的速度,避免了數(shù)據(jù)丟失現(xiàn)象,并減小了設(shè)備的體積,對體積小、成本低、速度高的飛行數(shù)據(jù)記錄系統(tǒng)設(shè)計具有十分重要的意義。

1 記錄器總體設(shè)計方案

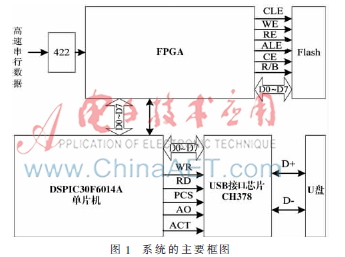

高速數(shù)據(jù)記錄器的系統(tǒng)設(shè)計主要框圖如圖1所示,主要由現(xiàn)場可編程器件FPGA、DSPIC30F6014A單片機、USB接口控制芯片CH378、U盤、數(shù)據(jù)存儲芯片F(xiàn)lash和高速串行數(shù)據(jù)總線422等模塊組成。

整個系統(tǒng)工作過程:首先高速串行數(shù)據(jù)經(jīng)過422總線傳輸給FPGA,然后FPGA對高速數(shù)據(jù)進行串并轉(zhuǎn)換和編幀處理,通過控制Flash實現(xiàn)高速數(shù)據(jù)的大容量緩存功能,并將緩存的數(shù)據(jù)經(jīng)過并口與DSPIC30F6014A進行通信,最后利用DSPIC30F6014A接收來自FPGA的數(shù)據(jù)并通過控制CH378將數(shù)據(jù)存儲到U盤中。

2 系統(tǒng)硬件電路設(shè)計

2.1 FPGA控制模塊

為了解決傳統(tǒng)的高速數(shù)據(jù)記錄系統(tǒng)直接由單片機作為主控制芯片造成的數(shù)據(jù)丟失問題,本設(shè)計選用FPGA作為高速數(shù)據(jù)的緩存控制芯片,以提高系統(tǒng)的可靠性。其中FPGA選用Xilinx公司Spartan-3E系列芯片XC3S500E,該芯片具有功耗低、資源豐富、高性能等特點,其I/O口兼容多種電平標準,有助于與單片機連接通信。內(nèi)部多達360 Kbit的Block RAM,可配置為雙端口RAM,添加必要的控制模塊構(gòu)成高速異步FIFO,為數(shù)據(jù)的寫入及讀取提供足夠的緩沖空間。同時,它具有4個時鐘管理單元,可方便對FPGA的主頻分頻或倍頻,產(chǎn)生不同模塊所需的時鐘信號,并能夠保證這些時鐘信號精確穩(wěn)定。

2.2 DSPIC30F6014A控制模塊

系統(tǒng)選用了高性能的DSPIC30F6014A單片機作為U盤數(shù)據(jù)存儲部分的主控制芯片,該單片機為單指令周期,采用哈佛雙總線結(jié)構(gòu),功耗低,驅(qū)動能力強,并且I/O端口功能強大,其與外部接口交換數(shù)據(jù)的效率非常高[3]。內(nèi)部有8 KB的片內(nèi)RAM,能夠作為高速數(shù)據(jù)的緩存區(qū),其與FPGA和CH378之間的通信都是通過8位并口的方式進行數(shù)據(jù)傳輸?shù)模軌蚝艽蟪潭鹊靥岣咦x寫數(shù)據(jù)的速度。其中DSPIC30F6014A與FPGA的連接示意圖如圖2所示。

2.3 CH378模塊

CH378能夠成為U盤記錄器首選的U盤接口芯片,是因為該芯片具有比CH376更高的通信速度[4],其可實現(xiàn)12 Mb/s全速通信和480 Mb/s高速通信;且在硬件連接方面,提供了高速8位被動并行接口,可直接掛接在單片機等處理器的數(shù)據(jù)總線上。其中CH378與DSPIC30F6014A單片機及U盤的部分引腳連接圖如圖3所示。將TXD引腳接GND,其余引腳懸空,使得CH378被配置為8位并口通信接口。8位并行數(shù)據(jù)線與單片機的RD口連接,CH378的WR#引腳、RD#引腳、PCS#引腳和A0引腳分別與單片機的RC4~RC1引腳相連,實現(xiàn)8位并口通信接口連接。

2.4 Flash模塊

大容量Flash選取了三星公司的NAND Flash K9M-DG08U5M,其內(nèi)部組織形式為16 G×8 bit,即容量為16 GB,與U盤的存儲容量相當,足以滿足海量數(shù)據(jù)緩沖所需的空間;供電電壓與FPGA的供電電壓相同,避免了為其單獨設(shè)計電源的麻煩;有8位數(shù)據(jù)引腳(D7~D0)、片選引腳(CS#)、命令鎖存引腳(CLE)、地址鎖存引腳(ALE)、寫控制引腳(WE)、讀控制引腳(RE)、Flash狀態(tài)引腳(R/B#)、電源及地引腳等,與FPGA的連接非常方便,只需FPGA分配相應(yīng)的引腳與Flash連接即可。

3 記錄器軟件設(shè)計

系統(tǒng)的軟件設(shè)計主要由FPGA和DSPIC30F6014A兩大主控部分組成,其中采用VHDL語言對FPGA的程序進行編寫,其主要實現(xiàn)串行數(shù)據(jù)的接收和處理、Flash數(shù)據(jù)讀寫控制以及與DSPIC30F6014A進行通信等功能;單片機的程序利用C語言進行描述,主要完成對CH378的控制、與FPGA的通信和數(shù)據(jù)傳輸?shù)墓δ堋?/p>

3.1 FPGA模塊程序設(shè)計

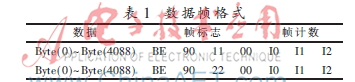

數(shù)據(jù)在存儲時是按照一定的幀格式進行存儲的,本系統(tǒng)設(shè)計的幀格式如表1所示,每一幀數(shù)據(jù)由4 089 B數(shù)據(jù)、4 B幀標志和3 B幀計數(shù)組成,其中幀標志分別為BEH、90H、數(shù)據(jù)流標識(第一路數(shù)據(jù)為11H,第二路數(shù)據(jù)為22H)和一個固定位00H。幀計數(shù)為3個字節(jié)表示,依次先為低位后為高位。

FPGA的主要工作流程圖如圖4所示,F(xiàn)PGA接收來自422總線接口的串行數(shù)據(jù),并對兩路數(shù)據(jù)進行串并轉(zhuǎn)換以及按照一定的數(shù)據(jù)格式進行編幀處理,之后將編幀處理的數(shù)據(jù)存入寫FIFO中,判斷寫FIFO半滿標志位WR_FIFO_HF是否為高電平。若為高電平則開始往Flash中寫入數(shù)據(jù),等到寫完一頁數(shù)據(jù)后,開始檢測單片機的讀數(shù)據(jù)信號是否有效。若有效,將由Flash數(shù)據(jù)讀寫控制模塊讀取Flash中的數(shù)據(jù),并暫存在讀FIFO,由單片機讀取讀FIFO中的數(shù)據(jù)。

3.2 DSPIC30F6014A模塊程序設(shè)計

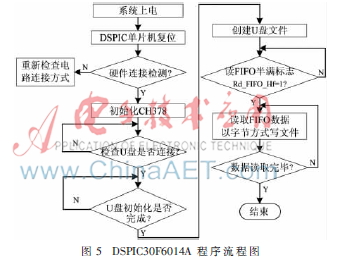

DSPIC30F6014A程序流程圖如圖5所示。系統(tǒng)上電后,首先單片機復位。然后由單片機向CH378發(fā)送硬件連接測試命令CMD_CHECK_EXIST(06H),接著發(fā)送數(shù)據(jù)55H,若硬件連接正常,應(yīng)由CH378返回數(shù)據(jù)AAH,否則說明硬件連接不正常或單片機不工作。測試到CH378連接正常后,初始化CH378,并設(shè)置工作模式為USB主機方式,然后檢測U盤是否連接,如果U盤成功連接并已檢測到,則對U盤進行初始化。初始化成功后,創(chuàng)建文件,檢測FIFO讀半滿標志位是否為1,若為1則將FPGA的讀FIFO中的數(shù)據(jù)通過DSPIC30F6014A的控制以字節(jié)方式寫入U盤文件,數(shù)據(jù)讀取完畢后結(jié)束操作。

4 系統(tǒng)調(diào)試結(jié)果及分析

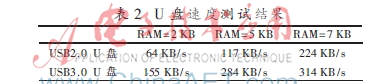

由于U盤的寫數(shù)據(jù)速度會受到U盤的質(zhì)量、單片機的性能等一些因素的影響,因此為了最大程度地提高數(shù)據(jù)記錄器處理數(shù)據(jù)的速度,在具體應(yīng)用之前,對一些性能進行了測試,通過分別往USB2.0和USB3.0的U盤中以字節(jié)方式一次性寫入100 MB的數(shù)據(jù)(其中分別選用單片機的RAM的2 KB、5 KB和7 KB作為數(shù)據(jù)的緩存區(qū)),得到了表2的U盤寫數(shù)據(jù)測試結(jié)果。結(jié)果表明,選用RAM為7 KB并結(jié)合USB3.0的U盤可以極大限度地提高數(shù)據(jù)記錄器處理數(shù)據(jù)的速度。

實驗及調(diào)試過程中,采用以FPGA為控制核心,產(chǎn)生波特率均為460.8 kb/s的422總線串行數(shù)據(jù)作為模擬數(shù)據(jù)源。為了便于分析,數(shù)據(jù)采用遞減的鋸齒波。數(shù)據(jù)存儲完畢后,通過計算機讀取U盤中的數(shù)據(jù),由上位機軟件對文件進行分析和繪圖顯示,圖6為數(shù)據(jù)波形整體圖,圖7為波形拉伸放大后的波形,從圖6和圖7中可以看出波形穩(wěn)定,并無明顯丟數(shù)現(xiàn)象。

將讀出的數(shù)據(jù)在UltraEdit中打開,如圖8所示,并沒有出現(xiàn)數(shù)據(jù)錯誤并且數(shù)據(jù)幀格式正確,說明本電路具有可靠的高速數(shù)據(jù)傳輸性能。

5 結(jié)論

為了滿足目前飛行數(shù)據(jù)記錄器對數(shù)據(jù)的大容量和高速存儲的需求,文中提出了一種基于FPGA和DSPIC-30F6014A的數(shù)據(jù)記錄器設(shè)計方法,并對數(shù)據(jù)寫入U盤的速度進行了測試。結(jié)果表明,高速串行數(shù)據(jù)經(jīng)過數(shù)據(jù)記錄器的一系列處理后,最后以并行數(shù)據(jù)寫入USB3.0 U盤的速度可達到314 KB/s,并且通過上位機分析得知數(shù)據(jù)存儲可靠,并無數(shù)據(jù)丟失現(xiàn)象。該設(shè)備還具有設(shè)備體積小、成本低和便于攜帶等優(yōu)點,很大程度緩解了數(shù)據(jù)存儲的壓力,具有很廣闊的應(yīng)用前景。

參考文獻

[1] 王偉,費益.民用飛機飛行記錄系統(tǒng)研究[J].電光與控制,2013,20(3):73-74.

[2] 盧艷軍,牛闖,張曉東.新型通用飛機機載數(shù)據(jù)記錄儀的研究[J].沈陽航空航天大學學報,2014,31(1):82-83.

[3] 王中華,郭改枝,王筱凱.基于DSPIC30F處理器的多路數(shù)據(jù)采集系統(tǒng)的設(shè)計[J].內(nèi)蒙古師范大學學報,2012,41(6):620-621.

[4] 蔡雪佳,周征翰,伍郁韓.基于USB-Host的大容量數(shù)據(jù)采集方案研究[J].電子設(shè)計工程.2011,19(16):1-3.