文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2015.09.002

中文引用格式: 朱宇. 綜合化航電設(shè)備中數(shù)字交換網(wǎng)絡(luò)系統(tǒng)應(yīng)用需求與實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2015,41(9):10-13.

英文引用格式: Zhu Yu. Application requirements and implementation of data exchange network system in integrated avienics[J].Application of Electronic Technique,2015,41(9):10-13.

0 引言

隨著電子技術(shù)的發(fā)展,航空電子設(shè)備綜合化、集成化的程度越來(lái)越高。高度綜合化航空電子設(shè)備與傳統(tǒng)的分立式航空電子設(shè)備不同,它將機(jī)載傳感器信道按照處理頻段進(jìn)行劃分,對(duì)相同頻段上的信道資源采用通用化模塊設(shè)計(jì)[1]。功能軟件資源亦采用模塊化設(shè)計(jì),駐留在基帶信號(hào)處理模塊上。系統(tǒng)通過(guò)對(duì)信道軟硬件資源進(jìn)行配置及重構(gòu)實(shí)現(xiàn)各項(xiàng)功能線程[2]。

信道資源通用化模塊設(shè)計(jì),必然需要傳感器模擬信號(hào)數(shù)字化不斷前移,信號(hào)采樣頻率越來(lái)越高,導(dǎo)致射頻信道模塊與數(shù)字處理模塊之間傳輸?shù)臄?shù)字信號(hào)速率越來(lái)越高,達(dá)到幾百M(fèi)b/s,甚至超過(guò)1 Gb/s,因此傳統(tǒng)的機(jī)載總線技術(shù),如1553B、VME等已遠(yuǎn)不能滿足高速數(shù)字信號(hào)傳輸?shù)囊蟆?/p>

為滿足綜合化航電系統(tǒng)資源可配置與可重構(gòu)的應(yīng)用需求,多個(gè)通用射頻信道模塊與多個(gè)數(shù)字信號(hào)處理模塊之間需要完成數(shù)據(jù)路由和數(shù)據(jù)交換。數(shù)字交換網(wǎng)絡(luò)系統(tǒng)實(shí)現(xiàn)了通用射頻信道模塊與數(shù)字信號(hào)處理模塊之間的高速數(shù)據(jù)傳輸與數(shù)據(jù)交換功能。

1 綜合化航電系統(tǒng)對(duì)數(shù)字交換網(wǎng)絡(luò)需求

1.1 綜合化航電系統(tǒng)架構(gòu)

綜合化航電系統(tǒng)是一個(gè)基于軟件無(wú)線電技術(shù)的高度綜合化系統(tǒng)。系統(tǒng)包含通信、導(dǎo)航、識(shí)別類別數(shù)十個(gè)傳感器功能。當(dāng)系統(tǒng)需要某項(xiàng)傳感器功能時(shí),與此功能相關(guān)的軟、硬件資源在系統(tǒng)統(tǒng)一調(diào)度下進(jìn)行組合,構(gòu)建成與此功能相關(guān)的從天線、射頻信道、信號(hào)處理、數(shù)據(jù)處理、接口處理的完整鏈路處理通道,同時(shí)通過(guò)加載運(yùn)行相關(guān)的功能軟件,構(gòu)成一個(gè)功能線程,完成該功能項(xiàng)的接收/發(fā)射和信號(hào)/信息處理[3]。

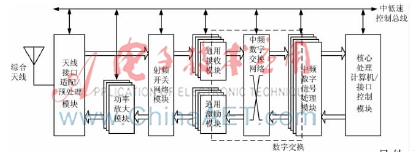

綜合化航電系統(tǒng)模型如圖1所示。

工作原理:傳感器信號(hào)接收時(shí),射頻信號(hào)由綜合天線接收,經(jīng)射頻開(kāi)關(guān)網(wǎng)絡(luò)路由后送入通用接收模塊進(jìn)行下變頻、放大、濾波等處理,再經(jīng)過(guò)A/D采樣數(shù)字化后成為標(biāo)準(zhǔn)數(shù)字中頻信號(hào),送入中頻數(shù)字交換網(wǎng)絡(luò)模塊,經(jīng)路由后送至中頻信號(hào)處理模塊進(jìn)行解調(diào)處理,最后解調(diào)完成的基帶功能數(shù)據(jù)送入核心處理計(jì)算機(jī)/接口控制模塊進(jìn)行處理,組成下行鏈路。

傳感器信號(hào)的發(fā)送為接收過(guò)程的逆過(guò)程,核心處理計(jì)算機(jī)/接口控制模塊輸出的基帶功能數(shù)據(jù)送入中頻信號(hào)處理模塊進(jìn)行調(diào)制,基帶調(diào)制數(shù)據(jù)經(jīng)過(guò)中頻數(shù)字交換網(wǎng)絡(luò)模塊路由后,送入通用激勵(lì)模塊中進(jìn)行D/A變換、上變頻、激勵(lì)后成為射頻信號(hào),將射頻信號(hào)經(jīng)射頻開(kāi)關(guān)網(wǎng)絡(luò)路由后送通用功率放大模塊進(jìn)行功率放大,將功率放大后的射頻信號(hào)經(jīng)天線接口適配模塊送相應(yīng)天線發(fā)射,組成上行鏈路。

1.2 綜合化航電系統(tǒng)對(duì)資源可配置及功能重構(gòu)的需求

一個(gè)典型的飛機(jī)作戰(zhàn)任務(wù)階段可以分為:滑行/起飛、戰(zhàn)術(shù)導(dǎo)航、作戰(zhàn)、歸航、進(jìn)場(chǎng)/著陸。根據(jù)飛機(jī)當(dāng)前任務(wù)階段,所需要的傳感器功能不盡相同[4]。例如:飛行全過(guò)程都需要超短波話音通信功能,精密測(cè)距功能只在進(jìn)場(chǎng)著陸時(shí)使用,航管應(yīng)答功能在除作戰(zhàn)的所有階段均需要使用,而敵我識(shí)別功能只有在作戰(zhàn)階段使用,飛機(jī)處于不同的飛行階段就會(huì)觸發(fā)系統(tǒng)對(duì)硬件資源進(jìn)行配置和重構(gòu),組合出所需的傳感器功能。

系統(tǒng)每一個(gè)通用信號(hào)處理模塊中,都駐留了該信號(hào)處理通道重構(gòu)所需的所有功能軟件,一旦飛行階段發(fā)生變化,通用信號(hào)處理模塊就會(huì)根據(jù)重構(gòu)策略重新加載功能軟件,與其他信道資源共同實(shí)現(xiàn)新功能。例如,作戰(zhàn)模式時(shí),系統(tǒng)占用航管功能處理資源,加載敵我識(shí)別功能軟件,實(shí)現(xiàn)敵我識(shí)別功能;非作戰(zhàn)模式時(shí),系統(tǒng)重新加載航管功能軟件,實(shí)現(xiàn)航管功能。

另外,不同的傳感器功能優(yōu)先級(jí)不同。當(dāng)優(yōu)先級(jí)高的功能鏈路發(fā)生故障被系統(tǒng)監(jiān)測(cè)到,則優(yōu)先級(jí)高的功能會(huì)占用優(yōu)先級(jí)低的功能的資源,系統(tǒng)功能重構(gòu)。例如,飛行全過(guò)程都需要超短波話音通信功能,并且超短波話音通信功能優(yōu)先級(jí)最高,一旦超短波話音功能發(fā)生故障,則超短波話音功能會(huì)搶占其他超短波鏈路資源實(shí)現(xiàn)超短波話音功能。

1.3 數(shù)字交換網(wǎng)絡(luò)系統(tǒng)在綜合化航電設(shè)備中的應(yīng)用

由于綜合化航電設(shè)備對(duì)系統(tǒng)功能重構(gòu)的需求,通用接收模塊A/D采樣后的中頻數(shù)據(jù)可能會(huì)送到不同的通用信號(hào)處理模塊進(jìn)行處理,通用信號(hào)處理模塊發(fā)送的中頻數(shù)據(jù)可能會(huì)送到不同的通用激勵(lì)模塊進(jìn)行處理。這樣在通用射頻信道模塊(通用激勵(lì)、通用接收)與通用數(shù)字信號(hào)處理模塊之間就需要數(shù)字交換網(wǎng)絡(luò)系統(tǒng)來(lái)實(shí)現(xiàn)通用射頻信道模塊數(shù)據(jù)信號(hào)與信號(hào)處理模塊數(shù)據(jù)信號(hào)的動(dòng)態(tài)路由和高速數(shù)據(jù)全交換功能。

2 數(shù)字交換網(wǎng)絡(luò)系統(tǒng)實(shí)現(xiàn)

2.1 數(shù)字交換網(wǎng)絡(luò)系統(tǒng)功能框圖

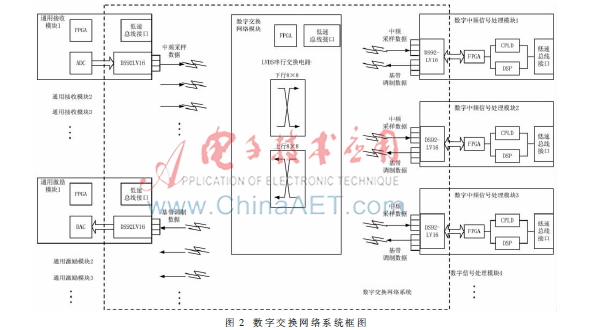

通用接收模塊A/D采樣后并串轉(zhuǎn)換為串行LVDS信號(hào)部分,通用激勵(lì)模塊D/A變換前LVDS信號(hào)串并轉(zhuǎn)換部分、中頻數(shù)字交換網(wǎng)絡(luò)模塊及中頻數(shù)字信號(hào)模塊LVDS信號(hào)接口部分共同構(gòu)成數(shù)字交換網(wǎng)絡(luò)系統(tǒng),如圖2所示。

數(shù)字交換網(wǎng)絡(luò)模塊完成下行8×8(中頻到信號(hào)處理)和上行8×8(信號(hào)處理到中頻)高速LVDS信號(hào)的全交換功能。

2.2 數(shù)字交換網(wǎng)絡(luò)模塊實(shí)現(xiàn)

數(shù)字交換網(wǎng)絡(luò)模塊主要由FPGA功能單元、CAN總線接口單元、下行8×8交換矩陣和上行8×8交換矩陣組成。FPGA功能單元采用Xilinx公司生產(chǎn)的Spartan-3系列FPGA XC3SD3400A-4CS484LI,其中集成了功能強(qiáng)大的32位微處理器軟核MicroBlaze,在其上運(yùn)行數(shù)字交換網(wǎng)絡(luò)模塊的應(yīng)用程序,MicroBlaze處理器通過(guò)OPB總線掛接了商用成熟的SJA1000 IP Core和交換矩陣控制IP Core,SJA1000 IP Core用于實(shí)現(xiàn)CAN總線協(xié)議處理,交換矩陣控制IP Core實(shí)現(xiàn)對(duì)下行8×8交換矩陣和上行8×8交換矩陣的控制。CAN總線接口單元實(shí)現(xiàn)數(shù)字交換網(wǎng)絡(luò)模塊與系統(tǒng)CAN總線接口的功能。FPGA通過(guò)接收系統(tǒng)控制命令,輸出控制信號(hào)實(shí)現(xiàn)對(duì)數(shù)字交換網(wǎng)絡(luò)路由的控制。

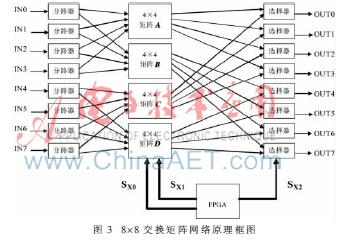

數(shù)字交換網(wǎng)絡(luò)模塊的核心是8×8交換矩陣電路,下行矩陣與上行矩陣設(shè)計(jì)相同,方向相反。交換矩陣采用專用集成電路實(shí)現(xiàn)。目前支持LVDS電平的交換矩陣專用集成電路芯片最大規(guī)模為4×4,方案采用4片4×4的LVDS交換芯片、8片分路器和8片選擇器來(lái)搭建8×8的下行交換矩陣。分路器(Splitters)采用MAXIM公司的MAX9174EUB,最高數(shù)據(jù)率達(dá)800 Mb/s。4×4的交換矩陣(Crosspoint Switch)采用TI公司的SN65LVDT125A實(shí)現(xiàn),最高數(shù)據(jù)速率達(dá)1.5 Gb/s。選擇器(Multiplexers)采用MAXIM公司的MAX9176EUB實(shí)現(xiàn),最高數(shù)據(jù)率達(dá)800 Mb/s。

如圖 3,每個(gè)輸入信號(hào)通過(guò)一個(gè)1分2的分路器將輸入信號(hào)同時(shí)送入2個(gè)4×4的交換矩陣中,其中IN(0~3)被送入矩陣A和矩陣B,IN(4~7)被送入矩陣C和矩陣D。矩陣A的4個(gè)輸出端口和矩陣C的4個(gè)輸出端口一一對(duì)應(yīng)并接在一起得到輸出端口OUT(0..3),矩陣B的4個(gè)輸出端口和矩陣D的4個(gè)輸出端口一一對(duì)應(yīng)并接在一起得到輸出端口OUT(4~7)。對(duì)于輸出信號(hào)并聯(lián)的控制采用一個(gè)2選1的選擇器實(shí)現(xiàn),通過(guò)對(duì)輸出端口使能信號(hào)的控制,保證在任一時(shí)刻并接輸出的信號(hào)只有一個(gè)處于輸出狀態(tài)。

FPGA產(chǎn)生通道選擇信號(hào)SX2、SX1和SX0(X=0,1,…,7)。通過(guò)這8組共24根選擇信號(hào)線,在選擇信號(hào)與通道輸出組合之間形成一一對(duì)應(yīng)的關(guān)系。整個(gè)模塊類似于8個(gè)8選1的數(shù)據(jù)選擇器,對(duì)于任意的一路輸入I(x),通過(guò)對(duì)通道選擇信號(hào)的設(shè)置,使其對(duì)應(yīng)于任意一路輸出O(x),完成數(shù)據(jù)全交換的功能。

2.3 數(shù)字交換網(wǎng)絡(luò)技術(shù)可行性分析

(1)LVDS傳輸技術(shù)適用于系統(tǒng)級(jí)背板傳輸

高速并行數(shù)據(jù)總線之間的串?dāng)_、布線等長(zhǎng)及背板走線規(guī)模等問(wèn)題[5],使得通用信號(hào)處理模塊與通用射頻信道模塊之間無(wú)法采用并行傳輸方式。另外試驗(yàn)表明,LVDS串行傳輸電纜長(zhǎng)度達(dá)到5 m,傳輸速度仍超過(guò)1 Gb/s[6],滿足系統(tǒng)720 Mb/s的速率要求。因此LVDS串行傳輸技術(shù)在傳輸方式和傳輸速率上滿足系統(tǒng)設(shè)計(jì)需求。

(2)強(qiáng)實(shí)時(shí)傳輸與交換

數(shù)字交換網(wǎng)絡(luò)傳輸?shù)闹蓄l信號(hào)數(shù)據(jù)流需要數(shù)據(jù)傳輸?shù)膹?qiáng)實(shí)時(shí)性以及延遲確定性,否則將會(huì)導(dǎo)致功能信號(hào)的失真。LVDS傳輸技術(shù)將中頻數(shù)字信號(hào)直接串并轉(zhuǎn)換進(jìn)行傳輸,無(wú)協(xié)議封裝和解析的開(kāi)銷,滿足系統(tǒng)強(qiáng)實(shí)時(shí)傳輸及傳輸延遲確定的要求,并且,傳輸通道的切換依靠交換節(jié)點(diǎn)芯片自身電氣特性,切換延遲小于10 ns,遠(yuǎn)遠(yuǎn)高于其他網(wǎng)絡(luò)交換技術(shù)。

(3)高性能與低成本

LVDS傳輸技術(shù)1 Gb/s的傳輸速率遠(yuǎn)遠(yuǎn)高于RS-422/485、ARINC-429等串行傳輸方式規(guī)定的傳輸速率[7],同時(shí),與RapidIO、FC等高性能傳輸方式相比,LVDS傳輸技術(shù)在體積、功耗和成本等方面開(kāi)銷要小得多。

3 測(cè)試驗(yàn)證

3.1 數(shù)據(jù)傳輸功能及誤碼率測(cè)試

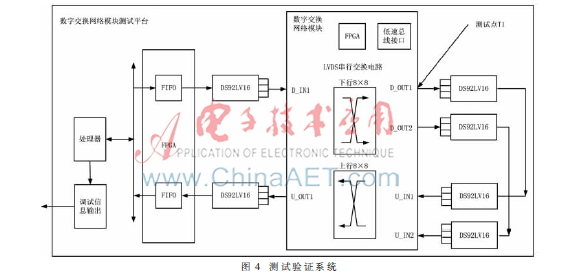

在系統(tǒng)上按照?qǐng)D4搭建測(cè)試驗(yàn)證環(huán)境,使用測(cè)試平臺(tái)上的處理器構(gòu)造16位周期數(shù)據(jù),并存入FPGA發(fā)送FIFO中,F(xiàn)PGA以50 MHz的頻率將FIFO中的數(shù)據(jù)向DS92LV16發(fā)送,并串轉(zhuǎn)換后送入數(shù)字交換網(wǎng)絡(luò)模塊D_IN1,默認(rèn)輸出通道為D_OUT1,在測(cè)試平臺(tái)上進(jìn)行回還后輸入U(xiǎn)_IN1,默認(rèn)輸出為U_OUT1,通過(guò)串并轉(zhuǎn)換后送入FPGA的接收FIFO中。處理器讀取接收FIFO的周期數(shù)據(jù)與發(fā)送的周期數(shù)據(jù)進(jìn)行比較,并將比較結(jié)果由調(diào)試端口輸出。

通過(guò)測(cè)試,實(shí)際傳輸數(shù)據(jù)大小為1.7×1010 bit,錯(cuò)誤位數(shù)為0,因此證明數(shù)字交換網(wǎng)絡(luò)系統(tǒng)在傳輸速率為800 Mb/s時(shí),誤碼率小于1×10-10,滿足系統(tǒng)720 Mb/s的傳輸速率要求。

3.2 通道切換功能測(cè)試

通過(guò)系統(tǒng)CAN總線下發(fā)下行鏈路通道切換指令,將下行鏈路默認(rèn)通道D_IN1-->D_OUT1輸出切換為D_IN1-->D_OUT2,測(cè)試平臺(tái)處理器無(wú)法接收到回環(huán)測(cè)試數(shù)據(jù)。再通過(guò)系統(tǒng)CAN總線下發(fā)上行鏈路通道切換指令,將上行鏈路默認(rèn)通道U_IN1-->U_OUT1輸出切換至U_IN2-->U_OUT1,測(cè)試平臺(tái)處理器重新接收到回環(huán)測(cè)試數(shù)據(jù),說(shuō)明數(shù)字交換網(wǎng)絡(luò)系統(tǒng)通道切換功能正常。

4 結(jié)論

本文介紹的數(shù)字交換網(wǎng)絡(luò)系統(tǒng)很好地滿足了綜合化航電設(shè)備系統(tǒng)資源可配置、系統(tǒng)功能重構(gòu)的需求,是綜合化航電設(shè)備的重要組成部分。同時(shí),介紹的數(shù)字交換網(wǎng)絡(luò)技術(shù)作為一種高性價(jià)比的背板高速數(shù)據(jù)交換技術(shù),還可以應(yīng)用于其他類似通用化、模塊化設(shè)計(jì)的無(wú)線電通信系統(tǒng)中。

參考文獻(xiàn)

[1] 何志強(qiáng).綜合化航空電子系統(tǒng)發(fā)展歷程及重要支撐技術(shù)[J].電訊技術(shù),2004(4):1-5.

[2] 茅成.綜合通信導(dǎo)航識(shí)別系統(tǒng)中的多鏈路超短波通信的實(shí)現(xiàn)[J].電訊技術(shù)2009(8):59-64.

[3] 施剛,錢泰來(lái).綜合化航空電子的系統(tǒng)管理技術(shù)[J].計(jì)算機(jī)工程,2008(S1):43-45.

[4] 郭柳柳,甄國(guó)涌,劉東海.基于LVDS傳輸電纜均衡器的可靠性分析[J].電子技術(shù)應(yīng)用,2014(10):40-42.

[5] 嚴(yán)俊.特種任務(wù)飛機(jī)綜合航空電子與任務(wù)系統(tǒng)體系結(jié)構(gòu)研究[J].航空電子技術(shù),2012(4):10-15.

[6] 邱偉.機(jī)載電子設(shè)備間高速數(shù)據(jù)傳輸研究[J].現(xiàn)代電子技術(shù),2014(12):35-36.

[7] 王康,郭志勇.基于FPGA的低成本長(zhǎng)距離高速傳輸系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2010(10):12-15.