文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2015.10.001

中文引用格式: 黃樂(lè)天,周在龍,王君實(shí),等. 片上網(wǎng)絡(luò)故障模型及容錯(cuò)設(shè)計(jì)方法合理性分析[J].電子技術(shù)應(yīng)用,2015,41(10):7-12,16.

英文引用格式: Huang Letian,Zhou Zailong,Wang Junshi,et al. Rationality analyzing of fault model and fault tolerance design method for network on chip[J].Application of Electronic Technique,2015,41(10):7-12,16.

0 引言

以2000年由瑞典皇家理工學(xué)院Hemani、Janstch等人首先在論文中明確定義了“Network on Chip”的概念為標(biāo)志[1],片上網(wǎng)絡(luò)正式成為一個(gè)研究領(lǐng)域已經(jīng)15年了。自該領(lǐng)域誕生之初起,片上網(wǎng)絡(luò)的可靠性設(shè)計(jì)就被作為一個(gè)重要問(wèn)題被各國(guó)研究者所重視。Benini和Micheli分析了片上通信網(wǎng)絡(luò)的分層模型并且給出了每層模型應(yīng)該具備的功能時(shí),明確提出了可靠性設(shè)計(jì)的需求[2]。片上網(wǎng)絡(luò)的可靠性問(wèn)題隨著集成電路工藝的進(jìn)步和片上網(wǎng)絡(luò)互聯(lián)規(guī)模的擴(kuò)大變得日趨嚴(yán)重。一方面集成電路工藝在向納米級(jí)演進(jìn)的過(guò)程中,由于加工精度、功耗密度、集成規(guī)模等因素而導(dǎo)致工藝誤差、老化、單粒子翻轉(zhuǎn)等問(wèn)題日益嚴(yán)重,從而導(dǎo)致器件的故障概率極大增加。另一方面隨著片上網(wǎng)絡(luò)規(guī)模的擴(kuò)大而導(dǎo)致的總元件數(shù)量的上升,導(dǎo)致片上網(wǎng)絡(luò)中故障發(fā)生的總量急劇上升。因此通過(guò)合理的容錯(cuò)設(shè)計(jì)方法提升片上網(wǎng)絡(luò)的可靠性成為片上網(wǎng)絡(luò)進(jìn)一步發(fā)展過(guò)程中繞不開(kāi)的一大難題。

集成電路的故障類(lèi)型依據(jù)其發(fā)生頻率和產(chǎn)生條件可以劃分為臨時(shí)性故障(Transient Fault)、間歇性故障(Intermittent Fault)以及永久性故障(Permanent Fault)三類(lèi)[3]。參考文獻(xiàn)[4]中總結(jié)了多種不同的物理效應(yīng)和三類(lèi)故障的對(duì)應(yīng)關(guān)系。臨時(shí)性故障主要由于孤立事件翻轉(zhuǎn)(Single Event Upset,SEU和Single Event Transient,SET)以及電子系統(tǒng)內(nèi)部噪聲引起。此類(lèi)故障的主要特點(diǎn)是臨時(shí)出現(xiàn)且發(fā)生位置隨機(jī)分布,與外界環(huán)境和工作條件關(guān)系不大。與臨時(shí)性故障相對(duì)應(yīng)的是永久性故障,主要由工藝誤差、老化、電遷移等原因引起的元器件損傷造成。永久性故障一旦發(fā)生將永久存在,且故障的總量將隨著集成電路使用時(shí)間的增加而持續(xù)增大。永久故障的位置分布有一定的隨機(jī)性,但由老化、電遷移等原因引起的永久性故障則在一定程度上受溫度、功耗密度等內(nèi)外部環(huán)境因素的影響。間歇性故障介于臨時(shí)性故障和永久性故障之間,主要是由于不同因素而導(dǎo)致的時(shí)序問(wèn)題而誘發(fā)。雖然某些因老化等因素導(dǎo)致的間歇性故障會(huì)隨著集成電路使用時(shí)間的增加而退化為永久性故障,但更多的間歇性故障則是由于特定時(shí)刻串?dāng)_(Crosstalk)、溫度變化(Temperature Variation)、電壓緊急(Voltage Emergency)等內(nèi)外部環(huán)境因素造成的時(shí)序問(wèn)題而引發(fā)。因而這些時(shí)序問(wèn)題發(fā)生的時(shí)間和概率雖然也呈現(xiàn)出一定的隨機(jī)性,但卻更容易發(fā)生在集成電路中關(guān)鍵路徑(Critical Path)和受環(huán)境因素影響更大的區(qū)域。由于間歇性故障和臨時(shí)性故障均不會(huì)持續(xù)發(fā)生,在以往的一些研究中通常將其歸為一類(lèi)故障加以研究[5]。但隨著集成電路工藝的進(jìn)步和低壓/近閾值集成電路設(shè)計(jì)方法的興起,間歇性故障由于其發(fā)生概率極大提升而成為了一個(gè)重要問(wèn)題[6],近年來(lái)針對(duì)這類(lèi)故障的研究明顯增加。

由于集成電路故障成因和類(lèi)型的研究大多屬于器件和工藝層面的研究?jī)?nèi)容,在研究容錯(cuò)設(shè)計(jì)時(shí)通常需要根據(jù)設(shè)計(jì)目標(biāo)的特點(diǎn)將其抽象為特定的故障模型以便深入研究。在抽象的過(guò)程中將不可避免地簡(jiǎn)化故障的某些特征,而不合理的特征取舍可能導(dǎo)致基于此模型的容錯(cuò)設(shè)計(jì)研究出現(xiàn)偏差,進(jìn)而設(shè)計(jì)出容錯(cuò)效率較低的硬件結(jié)構(gòu)或出現(xiàn)過(guò)度設(shè)計(jì)(Over Design)。對(duì)于片上網(wǎng)絡(luò)而言,故障可以在數(shù)據(jù)鏈路層、網(wǎng)絡(luò)層和傳輸層分別被抽象為不同的模型。數(shù)據(jù)鏈路層主要將故障抽象為鏈路上信號(hào)的阻塞(Stuck-at)和翻轉(zhuǎn)(Upset)[7]。網(wǎng)絡(luò)層的故障模型主要為自適應(yīng)容錯(cuò)路由研究服務(wù),傳統(tǒng)上將故障劃分為鏈路故障和路由器故障[8]。在傳輸層的故障模型則主要是考慮數(shù)據(jù)包內(nèi)容錯(cuò)誤或完全丟失[9]。這些模型在很大程度上降低了容錯(cuò)設(shè)計(jì)的復(fù)雜度,但相應(yīng)的也隱藏了一些關(guān)鍵特性。但更為嚴(yán)重的是,這些模型大多直接借鑒傳統(tǒng)的計(jì)算機(jī)/通信網(wǎng)絡(luò)故障模型,對(duì)片上網(wǎng)絡(luò)的特異性沒(méi)有給予足夠的體現(xiàn)。造成這種情況的部分原因是因?yàn)槠暇W(wǎng)絡(luò)在研究的初期大多以架構(gòu)設(shè)計(jì)、拓?fù)浞治觥⒙酚伤惴ㄑ芯康认鄬?duì)高層次的研究為主,與之相伴的容錯(cuò)設(shè)計(jì)研究也大多采用相對(duì)粗糙的模型。

隨著片上網(wǎng)絡(luò)研究的全面成熟和片上多核技術(shù)的普及,片上網(wǎng)絡(luò)已經(jīng)從系統(tǒng)結(jié)構(gòu)設(shè)計(jì)層面轉(zhuǎn)向?qū)崿F(xiàn)與應(yīng)用層面。自2007年Tilera公司推出了基于片上網(wǎng)絡(luò)互聯(lián)結(jié)構(gòu)的64核處理器Tile64[10]起,基于片上網(wǎng)絡(luò)的多核處理器芯片日漸增多。多倫多大學(xué)ABDELFATTAH M S等人于2014年發(fā)布了面向現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)的嵌入式片上網(wǎng)絡(luò)[11]則標(biāo)志著片上網(wǎng)絡(luò)開(kāi)始被用于多核處理器芯片以外其他類(lèi)型的芯片中。而在這一過(guò)程中片上網(wǎng)絡(luò)的實(shí)現(xiàn)結(jié)構(gòu)也日益明確,多數(shù)關(guān)鍵模塊的實(shí)現(xiàn)形式已有一些基本定論。因此我們有條件重新思考在當(dāng)前和未來(lái)集成電路工藝條件下片上網(wǎng)絡(luò)故障模型的合理性,從而得到更加合理、可行、適用的故障模型,為進(jìn)一步提升容錯(cuò)設(shè)計(jì)的容錯(cuò)效率并減少過(guò)度設(shè)計(jì)帶來(lái)的額外開(kāi)銷(xiāo)奠定基礎(chǔ)。同時(shí)正確地分析導(dǎo)致故障行為的物理效應(yīng),也將有助于設(shè)計(jì)合理的容錯(cuò)方案。本文將分別對(duì)現(xiàn)有片上網(wǎng)絡(luò)故障模型和容錯(cuò)設(shè)計(jì)方法的合理性進(jìn)行初步分析,為從事片上網(wǎng)絡(luò)容錯(cuò)設(shè)計(jì)的相關(guān)研究者提供參考。

1 片上網(wǎng)絡(luò)故障模型合理性分析

傳統(tǒng)的片上網(wǎng)絡(luò)故障模型在片上網(wǎng)絡(luò)容錯(cuò)設(shè)計(jì)的研究中曾發(fā)揮過(guò)重要作用,但隨著片上網(wǎng)絡(luò)的發(fā)展以及實(shí)用化程度的提高,片上網(wǎng)絡(luò)故障模型與實(shí)際的片上網(wǎng)絡(luò)故障行為之間的差距日益明顯。因此需要從造成片上網(wǎng)絡(luò)故障行為集成電路物理效應(yīng)出發(fā),重新審視片上網(wǎng)絡(luò)故障模型的合理性。

1.1 傳輸層故障模型分析

傳統(tǒng)網(wǎng)絡(luò)的傳輸層故障模型主要分為數(shù)據(jù)包內(nèi)容錯(cuò)誤與數(shù)據(jù)包完全丟失。其中數(shù)據(jù)包丟失是傳統(tǒng)網(wǎng)絡(luò)傳輸層所要解決的主要問(wèn)題。造成傳統(tǒng)網(wǎng)絡(luò)中傳輸層數(shù)據(jù)包丟失的主要原因包括:

(1)數(shù)據(jù)包內(nèi)容錯(cuò)誤超過(guò)底層協(xié)議可以恢復(fù)的極限而被底層硬件(如網(wǎng)卡等)直接丟棄而造成的數(shù)據(jù)包丟失;

(2)數(shù)據(jù)報(bào)頭錯(cuò)誤導(dǎo)致錯(cuò)誤的傳輸,如IP報(bào)頭、TCP報(bào)頭校驗(yàn)錯(cuò)誤時(shí)數(shù)據(jù)包會(huì)被丟棄而造成數(shù)據(jù)包丟失;

(3)由于傳輸過(guò)程中鏈路擁塞而導(dǎo)致數(shù)據(jù)包超過(guò)生存時(shí)間而被丟棄。

由于數(shù)據(jù)包內(nèi)容成果底層協(xié)議可以恢復(fù)的極限這一問(wèn)題和底層故障概率以及容錯(cuò)設(shè)計(jì)能力有關(guān),傳統(tǒng)網(wǎng)絡(luò)中數(shù)據(jù)包由于傳輸距離較遠(yuǎn)而容易出現(xiàn)錯(cuò)誤,而片上網(wǎng)絡(luò)底層的故障概率卻并不一定很高。對(duì)這一問(wèn)題的具體探討將在1.3節(jié)中再詳細(xì)討論。

相比于傳統(tǒng)網(wǎng)絡(luò),片上網(wǎng)絡(luò)的傳輸層故障有其不同的特征。相對(duì)于傳統(tǒng)網(wǎng)絡(luò),片上網(wǎng)絡(luò)的規(guī)模偏小且拓?fù)浣Y(jié)構(gòu)相對(duì)固定,因而在設(shè)計(jì)之初可以通過(guò)多種仿真方法對(duì)片上網(wǎng)絡(luò)的傳輸帶寬作較為精確的分析。同時(shí)由于片上網(wǎng)絡(luò)所承載的是多處理器核心之間傳輸?shù)男畔ⅲ捎谛畔鬏攲?shí)時(shí)性要求較高而導(dǎo)致?lián)砣苊馐瞧暇W(wǎng)絡(luò)設(shè)計(jì)優(yōu)化過(guò)程中必須要考慮的重要問(wèn)題。因此由于鏈路擁塞而丟棄數(shù)據(jù)包這種行為通常在片上網(wǎng)絡(luò)中并不被允許,因而這一故障原因在片上網(wǎng)絡(luò)中并不存在。

與傳統(tǒng)網(wǎng)絡(luò)大多采用串行傳輸方式不同,片上網(wǎng)絡(luò)基本是基于Flit的并行傳輸方式,通常在首個(gè)Flit中包含地址、控制等重要信息。由于采用并行傳輸?shù)姆椒ǎ煌奈煌ǔ2捎貌煌奈锢磉B線(xiàn)傳輸并獨(dú)立地存儲(chǔ)于不同的存儲(chǔ)單元中,因此針對(duì)重要信息的位所用物理連線(xiàn)和存儲(chǔ)單元可以采用有別于普通位的保護(hù)措施以加強(qiáng)。如對(duì)地址信息采用性能更強(qiáng)的糾錯(cuò)編碼,控制信號(hào)采用三模冗余(TMR)等[12],這些鏈路層容錯(cuò)措施將有效降低甚至消除由于報(bào)頭錯(cuò)誤而導(dǎo)致的數(shù)據(jù)包丟失的問(wèn)題。

綜上,在一個(gè)容錯(cuò)設(shè)計(jì)合理的片上網(wǎng)絡(luò)中,傳輸層故障模型中的數(shù)據(jù)包丟失故障可以基本忽略。因此需要充分地分析底層設(shè)計(jì)的容錯(cuò)能力以確定正確傳輸層故障模型是否需要考慮丟包故障。

1.2 網(wǎng)絡(luò)層故障模型分析

在過(guò)去10多年片上網(wǎng)絡(luò)容錯(cuò)路由的研究通常面向由永久性故障引起的片上網(wǎng)絡(luò)路由節(jié)點(diǎn)或鏈路功能性問(wèn)題,通常認(rèn)為由于制造缺陷、老化等原因造成的晶體管失效是導(dǎo)致永久性故障的主要原因。在傳統(tǒng)網(wǎng)絡(luò)的網(wǎng)絡(luò)層故障模型中,故障一般被分為鏈路故障和路由節(jié)點(diǎn)故障以方便容錯(cuò)路由算法的研究。在早期的片上網(wǎng)絡(luò)容錯(cuò)路由的研究中也普遍地采用了這樣的劃分方法,這一時(shí)期片上網(wǎng)絡(luò)的研究大多停留在架構(gòu)設(shè)計(jì)與分析的層面。但隨著Intel等公司先后發(fā)布了一系列基于片上網(wǎng)絡(luò)的多核處理器芯片[13]之后,片上網(wǎng)絡(luò)的硬件實(shí)現(xiàn)結(jié)構(gòu)日益明確,相應(yīng)的網(wǎng)絡(luò)層故障模型也需要革新。

傳統(tǒng)網(wǎng)絡(luò)中路由節(jié)點(diǎn)故障可能由多種原因?qū)е拢缏酚善鞯碾娫词?dǎo)致其因斷電而無(wú)法工作,整個(gè)路由器的功能將完全喪失而導(dǎo)致與其相連的鏈路均處于斷開(kāi)狀態(tài)。片上網(wǎng)絡(luò)路由節(jié)點(diǎn)與傳統(tǒng)網(wǎng)絡(luò)路由節(jié)點(diǎn)不同的是其功能完全由晶體管組成的邏輯電路實(shí)現(xiàn),而晶體管并不會(huì)出現(xiàn)大面積同時(shí)失效的情況。因此,如果單個(gè)晶體管的失效不會(huì)導(dǎo)致整個(gè)片上網(wǎng)絡(luò)路由節(jié)點(diǎn)的功能完全喪失,則片上網(wǎng)絡(luò)路由節(jié)點(diǎn)故障實(shí)質(zhì)上并不存在。

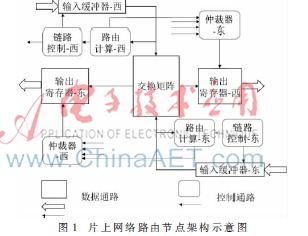

一個(gè)典型的片上網(wǎng)絡(luò)路由節(jié)點(diǎn)硬件實(shí)現(xiàn)結(jié)構(gòu)如圖1所示。

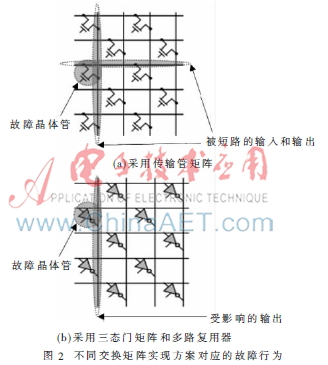

從圖1中可以看出其數(shù)據(jù)通路(Data path)可劃分為輸入緩沖器、交換矩陣、輸出寄存器等三個(gè)部分。其中輸入緩沖器中任何晶體管失效最多只能導(dǎo)致與自身相關(guān)的輸入鏈路出現(xiàn)故障,輸出寄存器中任何晶體管失效同樣最多只能導(dǎo)致與自身相關(guān)的輸出鏈路失效。因而這兩部分任意晶體管失效均無(wú)法造成整個(gè)路由節(jié)點(diǎn)出現(xiàn)工作不正常的情況而導(dǎo)致路由節(jié)點(diǎn)故障。交換矩陣中的故障行為和其具體的實(shí)現(xiàn)結(jié)構(gòu)有關(guān),參考文獻(xiàn)[14]中給出了三種不同的交換矩陣實(shí)現(xiàn)方式,可以分別由傳輸管矩陣、三態(tài)門(mén)矩陣以及標(biāo)準(zhǔn)CMOS邏輯門(mén)實(shí)現(xiàn)的多路復(fù)用器。傳輸管矩陣和三態(tài)門(mén)矩陣相比于標(biāo)準(zhǔn)的CMOS邏輯門(mén)的多路復(fù)用器而言雖然具有更小的面積和更低的功耗,但由于這兩種方案均存在延遲難以確定、驅(qū)動(dòng)能力偏弱、可能由于控制信號(hào)的時(shí)序問(wèn)題而產(chǎn)生臨時(shí)性的短路等問(wèn)題而在實(shí)際的芯片中較少采用。采用傳輸管矩陣構(gòu)建交換矩陣時(shí),若某個(gè)傳輸管由于某種原因處于導(dǎo)通狀態(tài),則至少有一對(duì)輸入線(xiàn)與輸出線(xiàn)處于短路狀態(tài),如圖 2(a)所示。處于這種狀態(tài)的交換矩陣不但影響故障傳輸管所在的輸出,還有可能通過(guò)短接的輸入線(xiàn)影響到其他輸出的電平。而采用的三態(tài)門(mén)矩陣和標(biāo)準(zhǔn)CMOS邏輯門(mén)的多路復(fù)用器構(gòu)建的交換矩陣由于其單向傳輸?shù)奶匦裕瑒t只會(huì)影響到故障所在的輸出,如圖2(b)所示。由此可見(jiàn),在不采用傳輸管矩陣構(gòu)建交換矩陣時(shí),單個(gè)晶體管的失效只影響其所在的輸出端口,而不會(huì)波及其余輸出端口。因而在大多數(shù)不采用傳輸管實(shí)現(xiàn)交換矩陣的路由節(jié)點(diǎn)中,數(shù)據(jù)通路上任意位置出現(xiàn)單個(gè)晶體管失效均可以被等效為輸入鏈路故障或輸出鏈路故障,而不會(huì)出現(xiàn)路由節(jié)點(diǎn)功能整體失效的情況。

在對(duì)路由節(jié)點(diǎn)的架構(gòu)分析中,路由節(jié)點(diǎn)控制通路(Control path)故障通常被認(rèn)為會(huì)導(dǎo)致路由節(jié)點(diǎn)整體功能失效。這是因?yàn)榧軜?gòu)設(shè)計(jì)人員在仿真中習(xí)慣于調(diào)用同樣的功能函數(shù)來(lái)模擬各個(gè)輸入和輸出鏈路的路由、仲裁等功能。但在實(shí)際的路由節(jié)點(diǎn)硬件結(jié)構(gòu)中,路由計(jì)算單元通常與輸入緩沖器配對(duì)實(shí)現(xiàn),而仲裁電路則通常與輸出寄存器配對(duì)實(shí)現(xiàn)。這樣設(shè)計(jì)的原因是可以保證多個(gè)輸入輸出鏈路可以同時(shí)完成路由計(jì)算/仲裁的工作,從而最大限度地利用硬件并行工作的特性提升包交換的速度。參考文獻(xiàn)[15]中給出了路由計(jì)算模塊和仲裁模塊實(shí)現(xiàn)的示意圖,從中可以較為明確地獲悉這種配對(duì)的特性。因此,當(dāng)某個(gè)路由計(jì)算單元中晶體管失效而導(dǎo)致該單元工作不正常時(shí),可以認(rèn)為與之配對(duì)的輸入緩沖器工作不正常而將其等價(jià)為輸入鏈路故障。而當(dāng)某個(gè)仲裁模塊中晶體管失效而導(dǎo)致該單元工作不正常時(shí)也可以認(rèn)為與之配對(duì)的輸出寄存器工作不正常而等效為輸出鏈路故障。因此,在一般情況下路由節(jié)點(diǎn)控制邏輯中單個(gè)晶體管失效也不會(huì)造成其整體功能失效。隨著失效晶體管數(shù)量的增加,可能出現(xiàn)多條輸入/輸出鏈路故障,從而使得節(jié)點(diǎn)大部分功能喪失。此時(shí)可以將多條鏈路故障等效為路由節(jié)點(diǎn)故障。

結(jié)合上面的分析可以得出這樣的結(jié)論,在使用常規(guī)的片上網(wǎng)絡(luò)路由器硬件結(jié)構(gòu)設(shè)計(jì)方案時(shí),單個(gè)或少量的晶體管失效通常不會(huì)引起路由節(jié)點(diǎn)整體功能的失效或故障。這些故障基本可以被等效為鏈路故障而非路由節(jié)點(diǎn)故障。但隨著一些新的仲裁方法或路由算法的提出,其對(duì)應(yīng)的電路結(jié)構(gòu)可能會(huì)發(fā)生一些變化而導(dǎo)致出現(xiàn)路由節(jié)點(diǎn)故障的可能,但出現(xiàn)這種故障的可能性需要進(jìn)一步探討。針對(duì)一個(gè)具體的片上網(wǎng)絡(luò)設(shè)計(jì)其容錯(cuò)方案時(shí)對(duì)片上網(wǎng)絡(luò)路由節(jié)點(diǎn)的具體電路結(jié)構(gòu)進(jìn)行適當(dāng)?shù)姆治觯纯梢源_定是否有必要采用路由節(jié)點(diǎn)故障模型。目前大部分容錯(cuò)路由的研究者已經(jīng)開(kāi)始更傾向于使用鏈路故障模型而非路由節(jié)點(diǎn)故障模型。

1.3 鏈路層故障模型分析

鏈路層故障模型主要考慮由于數(shù)據(jù)在傳輸過(guò)程中某些比特位的翻轉(zhuǎn)、呆滯等現(xiàn)象造成該位出現(xiàn)錯(cuò)誤。造成鏈路層故障的物理效應(yīng)有很多。元件老化、電遷移效應(yīng)、制造誤差等原因造成的某位信號(hào)線(xiàn)短路或斷路可以被認(rèn)為是鏈路層的永久性故障,單粒子翻轉(zhuǎn)效應(yīng)等影響存儲(chǔ)單元狀態(tài)而造成數(shù)據(jù)錯(cuò)誤可以被認(rèn)為是鏈路層的臨時(shí)性故障,電壓緊急、串?dāng)_(Crosstalk)等在特定的外部環(huán)境或特定工作狀態(tài)下引起的數(shù)據(jù)錯(cuò)誤可以被認(rèn)為是鏈路層的間歇性故障。因而鏈路層故障實(shí)際包含了臨時(shí)性故障、間歇性故障和永久性故障三種不同的故障分類(lèi)。這三種故障在鏈路層雖然故障行為表現(xiàn)相近,但由于其成因的區(qū)別導(dǎo)致使用鏈路層故障模型時(shí)其故障概率和故障注入方式有所區(qū)別。

臨時(shí)性故障由于是由單粒子翻轉(zhuǎn)等原因引起的,其發(fā)生時(shí)間和位置均近似呈隨機(jī)分布。因此針對(duì)臨時(shí)性故障的鏈路層故障模型可以視為以一定的概率隨機(jī)在更改任意位置、任意信號(hào)線(xiàn)的值,并不需要對(duì)故障的注入做特殊的處理。發(fā)生間歇性故障則明顯的受到環(huán)境以及具體硬件結(jié)構(gòu)的影響,其發(fā)生的時(shí)間和位置存在一定的規(guī)律性,但故障是否發(fā)生仍然具有一定的隨機(jī)性。永久性故障根據(jù)其產(chǎn)生原因不同,故障出現(xiàn)的規(guī)律也有較大區(qū)別。由加工誤差引起的永久性故障在分布時(shí)具有隨機(jī)性,但由于老化引起的永久性故障則明顯與環(huán)境有關(guān),因而其空間位置的分布不是完全隨機(jī)的。所以鏈路層間歇性故障和永久性故障的發(fā)生概率和空間分布問(wèn)題是一個(gè)需要討論的問(wèn)題。

首先對(duì)鏈路層間歇性故障的發(fā)生概率和空間分布加以討論。串?dāng)_(Crosstalk)被認(rèn)為是引起鏈路層間歇性故障的一個(gè)重要因素。一般認(rèn)為由于信號(hào)線(xiàn)上特定的信號(hào)跳變引起某些信號(hào)變化延遲,若恰好與時(shí)鐘抖動(dòng)等因素相配合則容易導(dǎo)致該信號(hào)被保存為一個(gè)錯(cuò)誤的值,從而引發(fā)故障。一般片上網(wǎng)絡(luò)容錯(cuò)設(shè)計(jì)研究者在考慮串?dāng)_引起的間歇性故障時(shí),通常習(xí)慣于從信號(hào)跳變過(guò)程本身去加以考慮,通過(guò)編碼或其他方式改變跳變的圖案(Pattern)來(lái)對(duì)其加以避免[16]。但實(shí)際上串?dāng)_本身是否會(huì)發(fā)生其實(shí)需要一定的外部條件,同時(shí)其是否會(huì)引起故障實(shí)際上更取決于其是否真正破壞了數(shù)字集成電路的時(shí)序。要發(fā)生串?dāng)_通常需要信號(hào)線(xiàn)線(xiàn)距和線(xiàn)長(zhǎng)均滿(mǎn)足一定的條件,因而可能發(fā)生串?dāng)_的位置通常在兩個(gè)路由節(jié)點(diǎn)之間的互聯(lián)線(xiàn)上而非其內(nèi)部連線(xiàn)。但從參考文獻(xiàn)[17]中明確給出的路由節(jié)點(diǎn)中各級(jí)流水線(xiàn)延遲的情況來(lái)看,在鏈路傳輸(Link Transmission,LT)即兩個(gè)路由節(jié)點(diǎn)之間信號(hào)傳輸階段的延遲要遠(yuǎn)遠(yuǎn)小于其他級(jí)流水線(xiàn)。換言之,在常規(guī)拓?fù)浣Y(jié)果中鏈路傳輸本身并不處于關(guān)鍵路徑(Critical Path)上。因而不管是否出現(xiàn)因?yàn)榇當(dāng)_而導(dǎo)致信號(hào)延遲的情況,在鏈路傳輸階段的時(shí)序余量可以充分保證被下一級(jí)路由節(jié)點(diǎn)接收的信號(hào)處于穩(wěn)定狀態(tài)。但對(duì)于某些面向特定應(yīng)用的非規(guī)則片上網(wǎng)絡(luò)而言[18],在網(wǎng)絡(luò)中存在一定的長(zhǎng)走線(xiàn),因而可能由于延遲較大而容易受到串?dāng)_的影響。造成間歇性故障的其他因素諸如電壓緊急、溫度等同樣導(dǎo)致特定位置的信號(hào)出現(xiàn)故障,通常這些故障更多出現(xiàn)在關(guān)鍵路徑上。在設(shè)計(jì)階段雖然設(shè)計(jì)者無(wú)法準(zhǔn)確地預(yù)知所有故障發(fā)生的位置與概率,但卻可以通過(guò)對(duì)設(shè)計(jì)方案進(jìn)行仿真與分析確定容易發(fā)生故障的薄弱環(huán)節(jié),從而合理地設(shè)置和使用鏈路層故障模型。

鏈路層永久性故障的發(fā)生概率和空間分布同樣有一定規(guī)律可循。由于老化引起的永久性故障與老化條件有關(guān),因而分析并確定容易引起老化的環(huán)境因素對(duì)確定這類(lèi)故障發(fā)生的概率和空間分布是有很大幫助的。溫度是引起晶體管老化的重要原因,對(duì)于集成電路的溫度分布可以在設(shè)計(jì)階段即通過(guò)一系列的熱仿真得到。而由于工藝誤差或制造過(guò)程引起的永久性故障比較難以精確建模,但可以通過(guò)分析電路模塊的規(guī)模簡(jiǎn)單等效得到,在此不再贅述。

2 容錯(cuò)設(shè)計(jì)方法合理性分析

片上網(wǎng)絡(luò)的容錯(cuò)設(shè)計(jì)方法已有相當(dāng)數(shù)量的論文討論,但這些論文通常只注重介紹容錯(cuò)方法本身,而對(duì)容錯(cuò)設(shè)計(jì)方法的使用前提與使用場(chǎng)景缺乏深入分析與討論。這一現(xiàn)象導(dǎo)致容錯(cuò)設(shè)計(jì)方法的合理性存在較大問(wèn)題,因而本文結(jié)合之前對(duì)故障模型的分析對(duì)容錯(cuò)設(shè)計(jì)方法的合理性進(jìn)行必要的分析。

2.1 基于離線(xiàn)測(cè)試的容錯(cuò)方法

基于離線(xiàn)測(cè)試的容錯(cuò)方法是一種最基本的容錯(cuò)方法,其目的在于提高芯片的良品率。較為典型的基于離線(xiàn)測(cè)試的容錯(cuò)方法即為片上網(wǎng)絡(luò)自適應(yīng)路由。大多數(shù)自適應(yīng)路由都是在故障狀態(tài)已知的前提下,通過(guò)外部所給出的故障信息按自適應(yīng)路由算法調(diào)整信息的傳輸路徑以避開(kāi)出現(xiàn)故障的鏈路或路由節(jié)點(diǎn)。

按具備自適應(yīng)路由能力的路由節(jié)點(diǎn)對(duì)故障信息的知曉程度不同,自適應(yīng)路由可分為基于全局信息的自適應(yīng)路由算法、基于局部信息的自適應(yīng)路由算法和基于本地信息的自適應(yīng)路由算法三類(lèi)。基于全局信息的自適應(yīng)路由算法需要使用整個(gè)網(wǎng)絡(luò)的各個(gè)資源的狀態(tài)信息。當(dāng)然,一個(gè)路由器需要確切知曉網(wǎng)絡(luò)中所有資源的狀態(tài)信息非常困難,代價(jià)非常高。因而此類(lèi)算法常采用空間迭代,使得每個(gè)路由器獲得等價(jià)的全局信息,如Q-Routing[19]。基于局部信息的自適應(yīng)路由算法需要路由節(jié)點(diǎn)知曉臨近節(jié)點(diǎn)的信息,F(xiàn)oN[20]以及FRR[21]是此類(lèi)算法的典型代表。相比于全局信息,獲取局部信息的代價(jià)要小很多。此類(lèi)自適應(yīng)路由算法也一直在優(yōu)化故障信息傳輸?shù)拈_(kāi)銷(xiāo)。基于本地信息的自適應(yīng)路由算法則只關(guān)注與路由節(jié)點(diǎn)相連的鏈路或節(jié)點(diǎn)的狀態(tài),Gradient算法[22]就是該類(lèi)算法的代表。這三類(lèi)算法中雖然基于全局信息的自適應(yīng)路由算法效果最好,但由于其信息傳播開(kāi)銷(xiāo)最大而較少有人研究。基于本地信息的自適應(yīng)路由算法性能提升受到較大限制而導(dǎo)致優(yōu)化空間較小,但在故障概率較低的情況下已經(jīng)足以滿(mǎn)足設(shè)計(jì)需求。基于局部信息的自適應(yīng)路由算法是前幾年研究的熱點(diǎn),其難點(diǎn)在于平衡信息傳播開(kāi)銷(xiāo)、算法復(fù)雜度等多方面的因素。

在傳統(tǒng)的自適應(yīng)路由方法的研究論文中幾乎不曾提及如何檢測(cè)并確定某條鏈路或路由節(jié)點(diǎn)已處于故障狀態(tài),其通常認(rèn)為故障信息已經(jīng)確認(rèn)并作為已知前提開(kāi)展研究。因而,離線(xiàn)測(cè)試作為一種基本的檢測(cè)手段可以直接與這些自適應(yīng)路由算法相配合作為提高良品率的方法。但需要注意的是離線(xiàn)測(cè)試只能針對(duì)出廠后的芯片加以檢測(cè),因而主要檢測(cè)由于生產(chǎn)加工問(wèn)題而引起故障。這類(lèi)故障的成因、分布及其行為在前文已有分析。在選擇或設(shè)計(jì)合理的自適應(yīng)路由算法時(shí)應(yīng)對(duì)其充分加以考慮,避免使用與之不相符合的故障模型或錯(cuò)誤估計(jì)故障概率。

2.2 基于在線(xiàn)測(cè)試的容錯(cuò)方法

與基于離線(xiàn)測(cè)試的容錯(cuò)方法不同,基于在線(xiàn)測(cè)試的容錯(cuò)方法往往需要與一定的在線(xiàn)測(cè)試手段相配合。首先通過(guò)在線(xiàn)測(cè)試確定故障的位置或發(fā)生的概率,再采取相應(yīng)的方法繞開(kāi)或替換故障單元以達(dá)到容錯(cuò)的目的。

基于編碼的在線(xiàn)檢測(cè)方法是開(kāi)銷(xiāo)較小、實(shí)現(xiàn)也較為方便的一種。這種方法通過(guò)檢錯(cuò)或糾錯(cuò)編碼檢測(cè)傳輸過(guò)程中數(shù)據(jù)出現(xiàn)的錯(cuò)誤。但由于糾錯(cuò)編碼同時(shí)也具備錯(cuò)誤數(shù)據(jù)恢復(fù)的功能,因而在大多數(shù)研究中把這類(lèi)方法歸結(jié)于容錯(cuò)方法而非在線(xiàn)檢測(cè)方法。但實(shí)際上合理運(yùn)用糾錯(cuò)或檢錯(cuò)編碼并與測(cè)試數(shù)據(jù)注入方法配合是可以達(dá)到在線(xiàn)檢測(cè)效果的,在后文中將對(duì)此做一定的分析。基于編碼的方法可以很方便地與重傳機(jī)制相配合構(gòu)成較為高效的混合糾錯(cuò)重傳機(jī)制(hybrid FEC/ARQ)[23],該方法對(duì)于臨時(shí)性故障的容錯(cuò)效果較好。但使用混合糾錯(cuò)重傳機(jī)制會(huì)導(dǎo)致比較大硬件開(kāi)銷(xiāo)和傳輸延遲,因而通常被用于傳輸層容錯(cuò)。

按照特定的規(guī)則向網(wǎng)絡(luò)注入專(zhuān)門(mén)的測(cè)試數(shù)據(jù)包,可以根據(jù)包的到達(dá)情況和接受到的數(shù)據(jù)對(duì)片上網(wǎng)絡(luò)的鏈路和路由節(jié)點(diǎn)加以檢測(cè)。與基于編碼的方法不同的是,由于發(fā)送的數(shù)據(jù)包內(nèi)容是確定的,可以在接收端通過(guò)比對(duì)檢測(cè)出鏈路中多個(gè)數(shù)據(jù)故障。由于其傳輸路徑可以提前設(shè)置,可以對(duì)路由節(jié)點(diǎn)中不同的傳播路徑加以測(cè)試[24]。使用特定的測(cè)試數(shù)據(jù)包不但可以判斷鏈路層故障引起的數(shù)據(jù)錯(cuò)誤,還可以通過(guò)數(shù)據(jù)包能否正常地通過(guò)特定的傳輸路徑來(lái)判斷路由節(jié)點(diǎn)中某些控制邏輯是否出錯(cuò)。當(dāng)測(cè)試出路由節(jié)點(diǎn)的問(wèn)題后將其映射為鏈路故障模型,再配合自適應(yīng)路由算法即可以實(shí)現(xiàn)網(wǎng)絡(luò)層容錯(cuò)設(shè)計(jì)。采用專(zhuān)門(mén)測(cè)試數(shù)據(jù)包的另外一個(gè)優(yōu)點(diǎn)在于通過(guò)統(tǒng)計(jì)已到達(dá)數(shù)據(jù)包的錯(cuò)誤概率,在明確數(shù)據(jù)包傳輸路徑的基礎(chǔ)上可以求解出不同鏈路或傳輸路徑上包的錯(cuò)誤概率,進(jìn)而對(duì)于診斷間歇性故障有極大的好處。

在線(xiàn)測(cè)試的另外一種方式是采用在線(xiàn)的內(nèi)建自測(cè)試(BIST)電路。這類(lèi)在線(xiàn)測(cè)試方法需要針對(duì)片上網(wǎng)絡(luò)設(shè)計(jì)專(zhuān)門(mén)的電路測(cè)試電路[25],并用適當(dāng)?shù)姆椒▽⒈粶y(cè)電路與其他的部分電路隔離。采用內(nèi)建自測(cè)試電路可以在更細(xì)粒度的層面檢測(cè)故障,有利于采用更細(xì)粒度的錯(cuò)誤恢復(fù)機(jī)制。但內(nèi)建自測(cè)試電路測(cè)試的規(guī)模與其測(cè)試粒度有關(guān),測(cè)試粒度越細(xì)則電路復(fù)雜度和規(guī)模越大。近年來(lái)將內(nèi)建自測(cè)試電路用于片上網(wǎng)絡(luò)容錯(cuò)設(shè)計(jì)的研究者主要把精力放在如何平衡在線(xiàn)檢測(cè)性能、粒度和代價(jià)。

2.3 基于糾錯(cuò)和硬件冗余的容錯(cuò)方法

糾錯(cuò)與硬件冗余從本質(zhì)上來(lái)說(shuō)屬于同一類(lèi)方法。糾錯(cuò)依靠傳輸更多的信息使得數(shù)據(jù)錯(cuò)誤可以被修復(fù),硬件冗余則通過(guò)在網(wǎng)絡(luò)中增加更多的硬件資源以使當(dāng)部分硬件出現(xiàn)故障時(shí)片上網(wǎng)絡(luò)仍然可以正常運(yùn)行。在傳輸更多信息時(shí)必然涉及到使用更多的硬件資源如連線(xiàn)或存儲(chǔ)單元來(lái),因而也是一種意義上硬件冗余。嚴(yán)格意義上說(shuō),片上網(wǎng)絡(luò)自適應(yīng)路由算法就是利用了片上網(wǎng)絡(luò)互聯(lián)資源的硬件冗余來(lái)達(dá)到容錯(cuò)目的。

糾錯(cuò)的效果與糾錯(cuò)編碼的復(fù)雜度以及傳輸過(guò)程中出現(xiàn)錯(cuò)誤的概率有關(guān)。在端到端傳輸?shù)腻e(cuò)誤概率顯然大于在兩個(gè)路由節(jié)點(diǎn)之間傳輸?shù)腻e(cuò)誤概率。因而在兩個(gè)路由節(jié)點(diǎn)之間才有糾錯(cuò)編碼的效果顯然好于端到端傳輸,但后者的面積、延遲、功耗等開(kāi)銷(xiāo)要遠(yuǎn)遠(yuǎn)小于前者[26]。各種開(kāi)銷(xiāo)的增加實(shí)際上會(huì)導(dǎo)致片上網(wǎng)絡(luò)的整體性能下降,在很多時(shí)候使得容錯(cuò)設(shè)計(jì)失去了原本的意義。換言之,如果主動(dòng)降低片上網(wǎng)絡(luò)的性能如運(yùn)行速度等,往往可以使得間歇性故障概率下降而在使用端到端糾錯(cuò)達(dá)到同樣的效果。這方面的研究目前尚缺乏比較全面和深入的分析。

3 結(jié)語(yǔ)

本文結(jié)合片上網(wǎng)絡(luò)的硬件實(shí)現(xiàn)結(jié)構(gòu)和先進(jìn)工藝集成電路物理效應(yīng)對(duì)片上網(wǎng)絡(luò)存在的故障行為進(jìn)行了總結(jié),分別就傳輸層、網(wǎng)絡(luò)層和鏈路層的故障模型進(jìn)行了詳細(xì)的分析。通過(guò)分析表明現(xiàn)有的故障模型是存在一定的適用范圍的。在此基礎(chǔ)上對(duì)不同故障模型所適用的應(yīng)用場(chǎng)景也進(jìn)行了歸納總結(jié)。在分析故障模型的基礎(chǔ)上對(duì)現(xiàn)有的片上網(wǎng)絡(luò)容錯(cuò)方法進(jìn)行了總結(jié),對(duì)其合理性和應(yīng)用方法作了初步分析。從本文的研究可以看出,片上網(wǎng)絡(luò)容錯(cuò)設(shè)計(jì)雖然經(jīng)過(guò)多年的發(fā)展已經(jīng)取得了長(zhǎng)足的進(jìn)步,但目前各個(gè)研究點(diǎn)還相對(duì)孤立而未形成全面完善的解決方案或研究結(jié)論。片上網(wǎng)絡(luò)容錯(cuò)設(shè)計(jì)還有賴(lài)于各國(guó)研究者的進(jìn)一步大力研究。

參考文獻(xiàn)

[1] HEMANI A,JANTSCH A,KUMAR S,et al.Network on chip:An architecture for billion transistor era[C].In Proceedings of 18th conference of Norchip,2000:1-8.