由于芯片每秒需要處理的計(jì)算越來(lái)越多,其設(shè)計(jì)變得越來(lái)越復(fù)雜,與此同時(shí),確保芯片中大量數(shù)據(jù)的及時(shí)傳輸也面臨著重大挑戰(zhàn)。Sondrel 解釋說(shuō),設(shè)計(jì)者通常會(huì)忽略至關(guān)重要的數(shù)據(jù)流方面,因?yàn)樨?fù)責(zé)這一任務(wù)的片上網(wǎng)絡(luò) (NoC) 設(shè)計(jì)十分復(fù)雜,并且由于存在許多極端情況,所以難以驗(yàn)證性能需求是否在所有情況下都得以滿足。這就導(dǎo)致片上網(wǎng)絡(luò)只能傳輸次優(yōu)數(shù)據(jù),且片上系統(tǒng) (SoC) 難以實(shí)現(xiàn)。

Sondrel 工程總監(jiān) Ben Fletcher 解釋說(shuō):“片上網(wǎng)絡(luò)的性能必須與片上系統(tǒng)的計(jì)算部分匹配。片上網(wǎng)絡(luò)的作用是以足夠快的速度提供輸入數(shù)據(jù),保持芯片上的計(jì)算 IP 以最大容量運(yùn)行,并存儲(chǔ)輸出數(shù)據(jù),從而防止系統(tǒng)阻塞。我們使用 Arteris? FlexNoC? IP 作為片上系統(tǒng)的片上網(wǎng)絡(luò)通信骨干技術(shù),它使我們能夠在更短的時(shí)間內(nèi)設(shè)計(jì)出更復(fù)雜的芯片。”

為什么選擇 FlexNoc?

他發(fā)現(xiàn)使用 FlexNoC 互連技術(shù)帶來(lái)諸多優(yōu)勢(shì)。第一個(gè)優(yōu)勢(shì)便是面積和芯線數(shù)的減少。這一優(yōu)勢(shì)通過(guò)利用傳輸層的封包和序列化能力實(shí)現(xiàn),片上網(wǎng)絡(luò)設(shè)計(jì)師因此能夠在不縮減性能的前提下精確控制片上網(wǎng)絡(luò)中可以減少芯線數(shù)和面積的部分。第二個(gè)優(yōu)勢(shì)是降低功耗。通過(guò)配置跨時(shí)鐘域和門(mén)控時(shí)鐘支持等電源管理功能可以將功耗控制在指定預(yù)算范圍內(nèi)。第三個(gè)優(yōu)勢(shì)是物理意識(shí)設(shè)計(jì)的實(shí)現(xiàn)。由于片上網(wǎng)絡(luò)設(shè)計(jì)方法從設(shè)計(jì)初便將片上系統(tǒng)的平面布局和任何物理設(shè)計(jì)限制考慮在內(nèi),因此設(shè)計(jì)團(tuán)隊(duì)能夠向后端團(tuán)隊(duì)交付一個(gè)保證滿足時(shí)序要求的網(wǎng)表。第四個(gè)優(yōu)勢(shì)是 FlexNoc 先進(jìn)的配置工具和優(yōu)秀的 UI。FlexNoc 所提供的用于生成性能良好、時(shí)序清晰互連的工具套件簡(jiǎn)單易學(xué),對(duì)片上網(wǎng)絡(luò)設(shè)計(jì)者而言非常容易上手,從而能夠提高生產(chǎn)率。

片上網(wǎng)絡(luò)有什么作用?

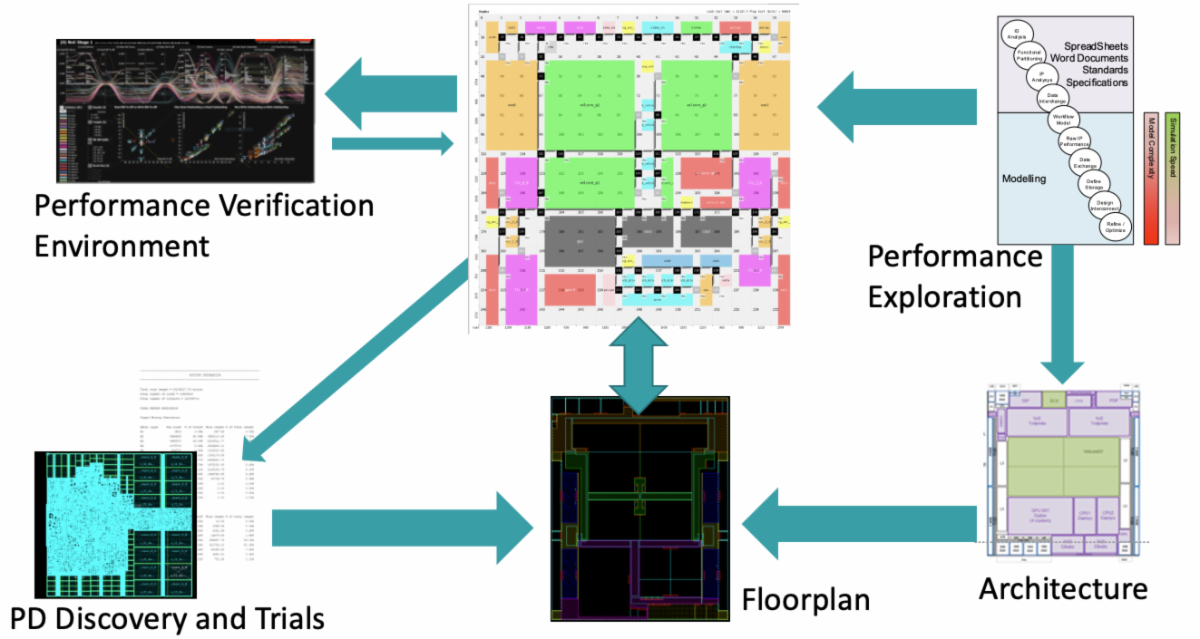

片上網(wǎng)絡(luò)會(huì)與片上系統(tǒng)中幾乎所有部分互連,與芯片的平面布局、架構(gòu)、功能需求、啟動(dòng)、安全、安防等方面有著內(nèi)在聯(lián)系。Ben Fletcher 提醒道:“這意味著在項(xiàng)目整個(gè)生命周期,平面布局很可能會(huì)出現(xiàn)變化,因此需要對(duì)片上網(wǎng)絡(luò)作出更改。相應(yīng)更改又會(huì)影響平面布局,形成反饋回路,從而造成延遲和成本超支。”“憑借多年設(shè)計(jì)大型復(fù)雜片上系統(tǒng)的經(jīng)驗(yàn),我們開(kāi)發(fā)了許多使我們能夠在項(xiàng)目初期進(jìn)行性能探索和驗(yàn)證的技術(shù)。通過(guò)盡早明確需求并快速驗(yàn)證片上網(wǎng)絡(luò)的變更是否滿足相應(yīng)需求,我們能夠明確平面布局和片上網(wǎng)絡(luò)設(shè)計(jì),減少不必要的設(shè)計(jì)更改,從而降低風(fēng)險(xiǎn)和額外成本。”

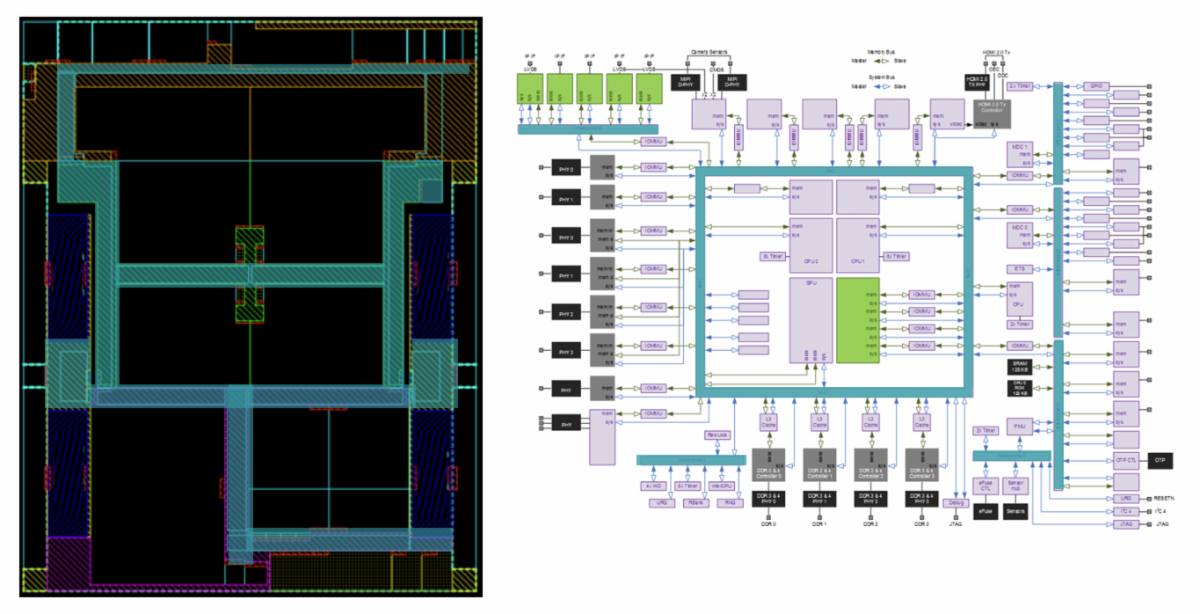

平面布局中左側(cè)藍(lán)色區(qū)域和右側(cè)藍(lán)色區(qū)域的片上網(wǎng)絡(luò)示例

圖例右側(cè)功能框圖上的片上網(wǎng)絡(luò)看似簡(jiǎn)單——只是有著很多連接部分,然而,左側(cè)的平面布局顯示,為實(shí)現(xiàn)高時(shí)鐘速度和在芯片中傳輸大量數(shù)據(jù),它占據(jù)了相當(dāng)大的區(qū)域,且布局復(fù)雜,同時(shí)與 IP 功能區(qū)塊分散的物理位置相連接,這也是使時(shí)序收斂變得困難的地方。

平面布局優(yōu)先還是片上網(wǎng)絡(luò)優(yōu)先?

通常情況下,設(shè)計(jì)者首先會(huì)從平面布局或片上網(wǎng)絡(luò)開(kāi)始芯片設(shè)計(jì)過(guò)程,這便會(huì)導(dǎo)致前面提到的反饋回路。Sondrel 的方法通過(guò)在設(shè)計(jì)階段一開(kāi)始進(jìn)行性能探索來(lái)避免這種情況發(fā)生,通過(guò)明確性能需求來(lái)確定和測(cè)試架構(gòu),減少更改概率,并相應(yīng)明確平面布局和片上網(wǎng)絡(luò)的設(shè)計(jì)。性能探索解決了只單獨(dú)驗(yàn)證 IP 功能區(qū)塊的典型問(wèn)題。這種驗(yàn)證方式未能將 IP 功能區(qū)塊間的交互作用考慮在內(nèi)。芯片上的 IP 功能區(qū)塊越多,就越難以理解它們之間的所有依賴關(guān)系,而這些依賴關(guān)系可能對(duì)芯片性能有著關(guān)鍵影響。例如,主/從接口可能不匹配、共享內(nèi)存沖突、時(shí)鐘偏移等。更多詳情請(qǐng)參見(jiàn) Sondrel 的白皮書(shū)“復(fù)雜片上系統(tǒng)建模和設(shè)計(jì)的 10 大切實(shí)有效的步驟”(網(wǎng)址:www.sondrel.com/solutions/white-paper)

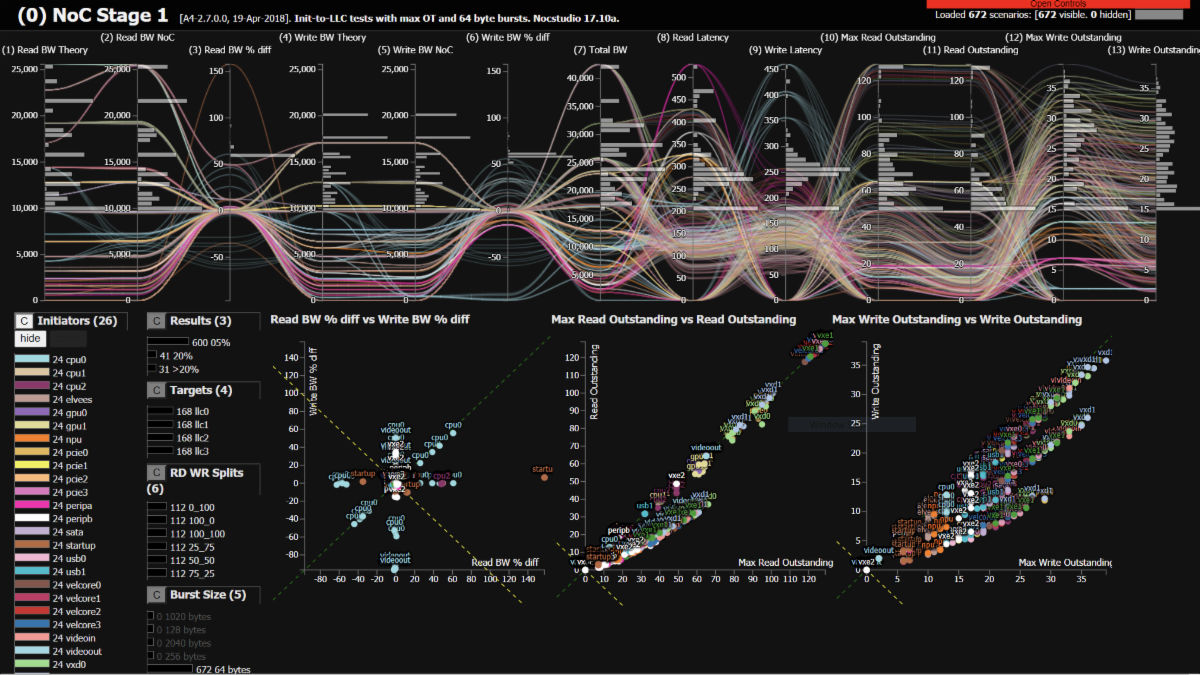

完成性能探索并確定性能需求后,便有了配置片上網(wǎng)絡(luò)的充足信息。我們需要一種方法來(lái)根據(jù)這些需求測(cè)試生成的 RTL,以確定需求滿足程度,然后實(shí)施快速迭代以達(dá)到所需的性能水平。為此,Sondrel 開(kāi)發(fā)了一個(gè)名為“性能驗(yàn)證環(huán)境”的專有測(cè)試平臺(tái)。該平臺(tái)使用可合成的 RTL 而非近似模型,且處理器和子系統(tǒng)替換為 Python 代碼中定義的處理器。這就使得內(nèi)存映射的總線通信量在 Python 中生成并通過(guò)片上網(wǎng)絡(luò)驅(qū)動(dòng),從而能夠快速掌握當(dāng)前的設(shè)計(jì)進(jìn)展情況以及所作更改對(duì)數(shù)據(jù)通信量的優(yōu)化情況。更多詳細(xì)信息,請(qǐng)參見(jiàn) Sondrel 的白皮書(shū)“性能驗(yàn)證環(huán)境與 RTL 比較”(網(wǎng)址:http://www.sondrel.com/solutions/white-papers)

這些快速迭代使我們能夠快速探索片上網(wǎng)絡(luò)配置,找到合適的解決方案,并應(yīng)用到平面布局設(shè)計(jì)過(guò)程中,以便隨后協(xié)同優(yōu)化片上網(wǎng)絡(luò)和平面布局。這樣能夠更快地實(shí)現(xiàn)穩(wěn)定狀態(tài),從而降低項(xiàng)目風(fēng)險(xiǎn)。

芯片規(guī)格可能會(huì)隨市場(chǎng)需求變化,而這一建模過(guò)程可以整體進(jìn)行更新,無(wú)需從頭開(kāi)始,因此能夠通過(guò)循證數(shù)據(jù)了解修改后的芯片設(shè)計(jì)是否滿足新的需求。

關(guān)于 Sondrel

Sondrel 成立于 2002 年,是集成電路各階段設(shè)計(jì)方面值得信賴的合作伙伴。在定義和設(shè)計(jì)專用集成電路方面的咨詢能力屢獲殊榮,為其將設(shè)計(jì)轉(zhuǎn)化為經(jīng)過(guò)測(cè)試的批量封裝硅芯片的一站式服務(wù)提供了有力補(bǔ)充。整個(gè)供應(yīng)鏈流程的單點(diǎn)聯(lián)系,確保風(fēng)險(xiǎn)低,上市時(shí)間快。Sondrel 總部位于英國(guó),其通過(guò)在中國(guó)、印度、法國(guó)、摩洛哥和北美的辦事處,為全球客戶提供支持。