摘 要: 簡單介紹I2C總線協(xié)議,用Altera公司的FPGA(現(xiàn)場可編程門陣列)芯片設計I2C總線接口控制器,用于控制EEPROM(帶電可擦寫可編程只讀存儲器)的讀寫操作。

關鍵詞: I2C總線;FPGA;EEPROM

0 引言

隨著電子技術快速發(fā)展,有許多的IC需要相互之間進行通信。為此,Philips公司開發(fā)了一種性能優(yōu)越的雙向兩線串行總線I2C(Inter-Integrated Circuit)總線。進行FPGA設計時經(jīng)常需要與外圍提供I2C接口的芯片進行通信,雖然市場上有專門的I2C總線接口芯片,但是大多性能指標固定、功能單一、使用不方便。根據(jù)I2C總線協(xié)議和其電路的電氣特性,在Altera公司的EP4CE10F17C8N型號的FPGA芯片上可以方便地實現(xiàn)I2C總線接口,進而實現(xiàn)EEPROM的讀寫操作。

1 I2C總線原理概述

I2C總線有兩條串行總線,一條是串行時鐘線(SCL),一條是串行數(shù)據(jù)線(SDA),連接到總線上的每個器件既可以作為發(fā)送器又可以作為接收器,且每個器件都有唯一的地址識別。主機主要負責產(chǎn)生時鐘、初始化發(fā)送和終止發(fā)送等操作。從機則是被主機尋址的器件。典型的連接在I2C總線上的器件有LCD、EEPROM等。總線的啟動信號條件是當SCL為高電平時,SDA由高變?yōu)榈停煌V箺l件是當SCL為高電平時,SDA電平由低變高。數(shù)據(jù)的變化只能發(fā)生在SCL為低電平期間[1]。

2 EEPROM讀寫控制器模塊的設計與實現(xiàn)

在進行數(shù)據(jù)傳輸時,讀寫控制器首先產(chǎn)生一個啟動信號(當SCL為高電平時,SDA由高變?yōu)榈停又l(fā)送控制字(即I2C總線器件的特征編碼和3 bit EEPROM的芯片地址)以及寫狀態(tài)R/W位為0到總線上。這里的總線器件特征碼為1010,而3 bit EEPROM的芯片地址為000。接著主控制器釋放總線,等待EEPROM發(fā)出的應答信號,由于采用的EEPROM型號是24LC64,因此在控制器收到應答后,將首先發(fā)送EEPROM高字節(jié)的存儲單元地址,當控制器再次收到應答后繼續(xù)發(fā)送EEPROM低字節(jié)的存儲單元地址,當控制器再次收到應答后,判斷是讀還是寫,如果是寫操作,則控制器發(fā)送數(shù)據(jù)字節(jié),并把數(shù)據(jù)寫入被尋址的存儲單元,EEPROM再次發(fā)送應答信號,讀寫控制器收到應答信號后,產(chǎn)生停止信號。如果之前判斷出是讀操作,則控制器會在收到應答后產(chǎn)生一個重復起始條件,緊接著寫入讀控制字10100001,這里的最后一位1表示讀操作,前面的1010000和之前說的一樣,是器件特征編碼1010和3 bit EEPROM芯片地址000。當控制器再次收到應答后會產(chǎn)生一個釋放總線的動作,把總線留給EEPROM,控制器負責接收EEPROM發(fā)出的數(shù)據(jù)。當控制器接收完數(shù)據(jù)后會占用總線,并發(fā)出一個非應答信號,表示數(shù)據(jù)收到,最后控制器再產(chǎn)生停止信號,停止本次傳輸。模塊的主狀態(tài)機如圖1所示。

這里寫入的地址是2 B的地址,且分兩次寫,因為此EEPROM的地址是16 bit的。

2.1 控制器的總線時鐘SCL產(chǎn)生

由于FPGA開發(fā)板的時鐘是50 MHz,這里先將輸入的50 MHz時鐘進行分頻產(chǎn)生400 kHz時鐘,利用400 kHz的時鐘去產(chǎn)生總線時鐘SCL。具體方法是:在400 kHz時鐘的下降沿對SCL進行翻轉(zhuǎn)操作,這樣能很好地實現(xiàn)I2C總線時序要求。這里生成的SCL是200 kHz時鐘。其Verilog代碼如下:

always@(negedge clk_400k or negedge rst_n)

begin

if(!rst_n)

scl<=0;

else

scl<=~scl;

end

時序圖如圖2所示。

由圖2可知,在SCL為高電平時,SDA由高變低會產(chǎn)生一個開始信號,而在SCL為高電平時,SDA由低變高會產(chǎn)生一個停止信號,而數(shù)據(jù)的改變只能在SCL為低電平期間發(fā)生,在SCL為高電平時,數(shù)據(jù)要保持穩(wěn)定。數(shù)據(jù)采樣時使用400 kHz時鐘的上升沿采樣,并且是在SCL為高電平時才能采數(shù)據(jù),因為這時的數(shù)據(jù)穩(wěn)定。

2.2 I2C總線數(shù)據(jù)輸入輸出

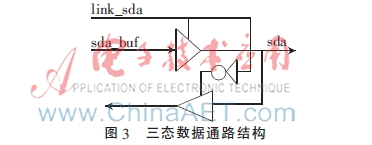

電路的輸出采用三態(tài)數(shù)據(jù)通路設計,如圖3所示。

其Verilog代碼如下:

assign sda=link_sda?sda_buf:1′bz;

由圖3可知,sda的I/O類型為inout,當開關link_sda為1時,讀寫控制器上的數(shù)據(jù)可以發(fā)送到sda上,實現(xiàn)控制器占用總線進行寫操作,當link_sda為0時,輸出為高阻態(tài),而此時外部的sda上的數(shù)據(jù)可以讀進來,實現(xiàn)了控制器釋放總線,將總線交由從機EEPROM,進而可將EEPROM發(fā)出的數(shù)據(jù)讀進來[2]。

數(shù)據(jù)的輸出涉及并串轉(zhuǎn)換,因為數(shù)據(jù)寄存器中的數(shù)據(jù)是8 bit,而I2C總線上傳輸?shù)臄?shù)據(jù)sda為1 bit,其Verilog代碼如下:

if(count1<8)

begin

data<={data[6:0],data[7]};

sda_buf<=data[7];

count1<=count1+1;

state<=t2;

end

設計采用循環(huán)移位的方式將8 bit的并行data數(shù)據(jù)一位一位地移到sda_buf線上送出去。

相反,I2C總線數(shù)據(jù)的輸入涉及串轉(zhuǎn)并操作,Verilog代碼如下:

if(count1 <8)

begin

link_sda <= 0;//讀寫控制器釋放總線

if(scl)

begin

data<={data[6:0],sda};//串轉(zhuǎn)并

count1<=count1+1;

state<=r2;

end

end

3 仿真驗證

仿真平臺的搭建如圖4所示。

由圖4可知,電路的仿真驗證模塊分為I2C接口控制器模塊、ROM模塊、地址發(fā)生器模塊、按鍵模塊、EEPROM模塊和數(shù)碼管顯示模塊。其中,按鍵模塊用于產(chǎn)生I2C接口控制器的讀寫操作信號;地址發(fā)生器模塊用于產(chǎn)生ROM和I2C接口控制器的地址信息;ROM模塊中事先存儲了一定量的數(shù)據(jù),并將這些數(shù)據(jù)發(fā)送給I2C接口控制器,用來寫入EEPROM;I2C接口控制器負責EEPROM的讀寫操作;數(shù)碼管顯示模塊負責將讀寫控制器從EEPROM中讀出的數(shù)據(jù)顯示出來,用來查看數(shù)據(jù)是否正確。

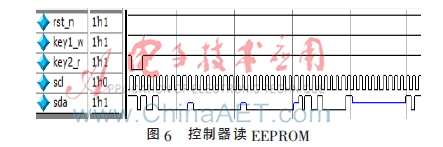

電路的仿真波形如圖5、圖6所示。

由圖5可知,在寫EEPROM操作時,讀寫控制器在開始信號后首先寫入1 B的控制字10100000(前面的1010是器件特征碼,000表示EEPROM的芯片地址,最后一位0表示寫操作),緊接著控制器釋放總線,等待EEPROM給它的應答。因為仿真只是模擬,并沒有接入EEPROM,所以應答位呈現(xiàn)高阻態(tài)。在應答的后面就是高字節(jié)的地址,等到再次收到應答信號時,控制器繼續(xù)發(fā)送低字節(jié)的地址位。這里的地址為0000_0000_0000_ 0000,共2 B,等再次收到應答信號時,控制器會發(fā)送單字節(jié)的數(shù)據(jù)0000_0001,將其寫入相應的存儲空間上。收到來自EEPROM的應答后,控制器產(chǎn)生停止信號,結(jié)束操作。圖6是控制器讀EEPROM操作,它與寫操作不同的是在寫入控制字和高低字節(jié)地址后,控制器會產(chǎn)生新的啟動信號,緊接著寫入1010_0001,最后的1表示是讀操作,這時控制器會釋放總線,等收到應答后繼續(xù)釋放總線,以讀取EEPROM中的數(shù)據(jù);1 B的數(shù)據(jù)收完后,控制器產(chǎn)生一個非應答信號并緊接著產(chǎn)生停止信號,表示讀數(shù)據(jù)任務結(jié)束。

4 結(jié)論

利用I2C總線協(xié)議設計出EEPROM讀寫控制器,與專用的I2C接口芯片相比,有配置靈活、使用方便、可移植性強的特點,除了滿足EEPROM的讀寫操作,還可滿足其他I2C總線器件的讀寫要求。電路仿真完成后,在FPGA上成功實現(xiàn)EEPROM的讀寫操作,通信正常,滿足要求。

參考文獻

[1] Philips Semiconductors. The I2C-bus Specification Version 2.1[Z]. 2000.

[2] 夏宇聞.Verilog數(shù)字系統(tǒng)設計教程[M].北京:北京航空航天大學出版社,2013.