摘 要: 設(shè)計了一種基于現(xiàn)場可編程邏輯器件的線陣CCD實時圖像采集系統(tǒng)。系統(tǒng)采用線陣CCD TCD2252D作為圖像傳感器,使用CCD專用信號處理芯片AD9826對CCD信號去噪并實現(xiàn)高速A/D轉(zhuǎn)換,同時用USB接口芯片完成CCD數(shù)據(jù)的傳輸,最后在上位機顯示采集的圖像數(shù)據(jù)。整個系統(tǒng)由基于Verilog的CCD驅(qū)動模塊、CCD輸出信號處理模塊、雙口RAM緩存模塊、USB接口控制模塊等組成,結(jié)合上位機模塊實現(xiàn)對CCD輸出圖像的準(zhǔn)確采集、顯示和保存。實驗結(jié)果表明,該系統(tǒng)能實時采集和顯示圖像信息,USB傳輸速度可達28 MB/s,系統(tǒng)實時性好。

關(guān)鍵詞: 實時采集;電荷耦合器件;現(xiàn)場可編程邏輯器件;信號處理

0 引言

目前,隨著科學(xué)研究和工業(yè)生產(chǎn)的需要,越來越多的場合需要實時高速的圖像采集處理系統(tǒng)。線陣CCD作為一種光電轉(zhuǎn)換圖像傳感器,它利用光電轉(zhuǎn)換原理將圖像光信號轉(zhuǎn)換為電信號,經(jīng)過預(yù)處理和A/D轉(zhuǎn)換后變?yōu)閿?shù)字信號,通過一種上位機通信方式,可在邏輯器件的控制下實現(xiàn)對圖像數(shù)據(jù)的采集傳輸,并在PC端進行后續(xù)處理。利用CCD采集圖像具有檢測精度高、處理速度快、抗干擾能力強、運行穩(wěn)定等優(yōu)點,其已廣泛應(yīng)用于圖像采集、非接觸式測量和實時監(jiān)控等諸多領(lǐng)域[1]。

CCD器件的正常工作需要外加驅(qū)動時序脈沖,時序脈沖的產(chǎn)生方法有很多種,如數(shù)字電路驅(qū)動法、單片機驅(qū)動法、EPROM驅(qū)動法。雖然這些方法都可以產(chǎn)生時序脈沖,但是電路設(shè)計的難度大,兼容性差。本文直接使用FPGA來產(chǎn)生時序脈沖。FPGA高速、并行等優(yōu)勢使系統(tǒng)的設(shè)計非常靈活;FPGA的資源豐富,尤其是內(nèi)部存儲資源,可作為CCD數(shù)據(jù)的緩存,能夠大大簡化系統(tǒng)硬件電路的設(shè)計。

本文設(shè)計了一種基于FPGA的線陣CCD實時圖像采集系統(tǒng),它采用FPGA+USB的平臺結(jié)構(gòu),以線陣CCD作為圖像傳感器,使用CCD專用信號處理芯片AD9826對CCD信號去噪并實現(xiàn)高速A/D轉(zhuǎn)換,同時用USB接口芯片完成CCD數(shù)據(jù)的傳輸,最后在上位機上顯示采集的圖像數(shù)據(jù)。

1 系統(tǒng)設(shè)計方案

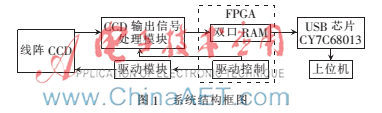

系統(tǒng)主要由CCD驅(qū)動模塊、信號處理模塊、數(shù)據(jù)緩存模塊、雙口RAM緩存模塊、USB接口模塊和上位機模塊等組成,系統(tǒng)結(jié)構(gòu)框圖如圖1所示。上電后,線陣CCD圖像傳感器在FPGA的驅(qū)動下接收前端圖像信息,將光信號轉(zhuǎn)換成電信號輸出;然后,模數(shù)轉(zhuǎn)換器AD9826對CCD輸出信號作相關(guān)雙采樣并轉(zhuǎn)換成數(shù)字信號,F(xiàn)PGA配置內(nèi)部雙口RAM作為數(shù)字信號的緩存區(qū);最后,USB接口控制芯片把數(shù)字信號傳輸?shù)缴衔粰C,在VS2008環(huán)境下開發(fā)上位機應(yīng)用程序,實現(xiàn)圖像數(shù)據(jù)的實時顯示和存儲,以便后續(xù)數(shù)據(jù)處理。

1.1 主控制器FPGA

FPGA是整個系統(tǒng)的核心,只有深入了解其內(nèi)部結(jié)構(gòu),才能有效利用它。FPGA能夠用較少資源實現(xiàn)較高的性能和更多的功能,滿足低成本要求。本設(shè)計中的FPGA采用Altera公司的Cyclone IV系列的EP4CE6E22C8,其內(nèi)部具有6 272個邏輯單元,30個M9K內(nèi)存單元,270 Kbit嵌入式存儲器,2個鎖相環(huán),92個用戶I/O,可自由分配其功能與外部電路的連接。在該系統(tǒng)中,F(xiàn)PGA主要負責(zé)CCD的驅(qū)動控制、AD9826的采樣控制、雙口RAM的配置以及對USB接口芯片的控制。經(jīng)過資源估算,該FPGA完全可以實現(xiàn)系統(tǒng)的功能。

1.2 CCD驅(qū)動模塊

線陣CCD是采集系統(tǒng)的重要器件,完成光信號向電信號的轉(zhuǎn)換。本文采用的線陣CCD是東芝公司生產(chǎn)的TCD2252D。TCD2252D是一款高靈敏度、低暗電流的雙溝道彩色線陣CCD,它由光敏區(qū)、轉(zhuǎn)移柵、模擬移位寄存器及信號輸出單元組成。該器件包含3列2 700有效像元的光敏二極管,分別采集紅綠藍三色,最小像素單元尺寸為 ,相鄰光敏列間距為64

,相鄰光敏列間距為64 [2]。

[2]。

在線陣CCD圖像采集應(yīng)用中,CCD對驅(qū)動時序要求較為嚴(yán)格,只有精確的時序驅(qū)動才能保證CCD輸出正確的像素信號。所以在CCD的應(yīng)用中,首先要設(shè)計滿足時序要求的驅(qū)動電路。根據(jù)芯片手冊,該器件工作在5 V驅(qū)動脈沖、12 V電源條件下,其中6路驅(qū)動脈沖分別是轉(zhuǎn)移脈沖SH、二相驅(qū)動脈沖F1和F2、采樣保持脈沖SP、復(fù)位脈沖RS和箝位脈沖CP。

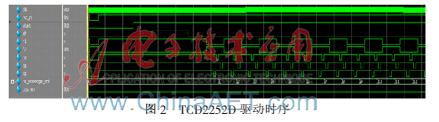

圖2所示為TCD2252D驅(qū)動時序仿真波形,這六路驅(qū)動時序有著嚴(yán)格的時序關(guān)系。轉(zhuǎn)移脈沖SH高電平期間驅(qū)動脈沖F1必須為高電平,而且SH的下降沿必須對應(yīng)F1的高電平才能保證光敏區(qū)的信號電荷向模擬移位寄存器并行轉(zhuǎn)移。驅(qū)動脈沖F1和F2是兩個占空比為1∶2、頻率為0.5 MHz且極性相反的方波脈沖;SP、RS、CP均是占空比為1∶8、頻率為1 MHz的方波脈沖。SH脈沖的周期決定了光積分時間的長短。由于CCD正常輸出時會有76個啞元像素和2 700個有效像素,所以在一個行周期內(nèi)至少要有2 776個RS脈沖,從而可以計算出每次光積分所需的時間為TSH>2 776TRS=2 776  。為了保證后續(xù)AD9826對CCD信號的有效采樣,在仔細分析CCD輸出信號特點后,設(shè)置一個RS上升沿計數(shù)器,當(dāng)該計數(shù)器計數(shù)到64時置1,AD9826開始對CCD有效輸出信號進行相關(guān)雙采樣。

。為了保證后續(xù)AD9826對CCD信號的有效采樣,在仔細分析CCD輸出信號特點后,設(shè)置一個RS上升沿計數(shù)器,當(dāng)該計數(shù)器計數(shù)到64時置1,AD9826開始對CCD有效輸出信號進行相關(guān)雙采樣。

TCD2252D需要5 V的CMOS驅(qū)動電平,但FPGA輸出為3.3 V的TTL電平,因此需要使用電平轉(zhuǎn)換電路增強FPGA輸出信號的驅(qū)動能力。TI公司研發(fā)的電平轉(zhuǎn)換芯片SN74LVC4245能實現(xiàn)8位總線的3.3 V和5 V邏輯電平的雙向轉(zhuǎn)換,工作頻率高達10 MHz,能滿足本系統(tǒng)CCD驅(qū)動頻率1 MHz的要求。

1.3 信號處理模塊

由于CCD輸出的是帶有暗電流噪聲和輸出放大器復(fù)位脈沖串?dāng)_的模擬信號,因此必須進行信號處理才能為后續(xù)電路使用[3]。本系統(tǒng)中,使用ADI公司生產(chǎn)的專用CCD信號處理芯片AD9826,該芯片集成16位ADC,速度可達15 MS/s。作為模數(shù)轉(zhuǎn)換芯片,其片內(nèi)集成相關(guān)雙采樣(Correlated Double Sampler,CDS)等多種功能電路,提高了信號預(yù)處理的質(zhì)量,簡化了電路的設(shè)計。

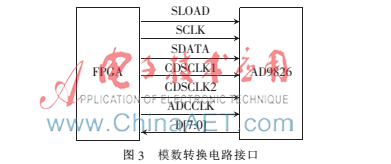

AD9826由VINR、VNG、VINB三路獨立采樣通道電路組成,每個采樣通道都由輸入箝位電路、相關(guān)雙采樣電路、偏移DAC和可編程增益放大器組成,并通過多路復(fù)用(MUX)接入一個16位模數(shù)轉(zhuǎn)換器,采樣輸出信號通過8位并行數(shù)據(jù)總線分時輸出16位數(shù)據(jù)。此處系統(tǒng)設(shè)計只取一路線陣CCD輸出,選擇VINR紅色通道作為信號輸入,采用單通道CDS和16 bit轉(zhuǎn)換模式。CCD輸出R信號經(jīng)過隔直電容,將有效信號耦合輸入到AD9826中VINR通道采樣,其他兩個通道要做接地處理,以防止對VINR通道產(chǎn)生干擾,如圖3所示。

AD9826的工作模式可通過三線雙向串行接口(SCLK、SLOAD、SDTATA)配置內(nèi)部寄存器來設(shè)定。串行時鐘SCLK最高頻率為10 MHz,系統(tǒng)采用5 MHz頻率,由主時鐘50 MHz分頻可得。CCD輸出信號幅值為0~4 V,不需要AD9826內(nèi)部增益放大。

AD9826工作在單通道CDS工作模式下,CDS電路在每一像素周期內(nèi)對輸入的CCD信號采樣兩次。CDSCLK1的下降沿采樣參考信號,CDSCLK2的下降沿采樣有效信號。CDS電路輸出的是兩次采樣值之差,消除了噪聲,此時信號即為有效視頻信號。

分析CCD輸出信號特點,F(xiàn)PGA內(nèi)部產(chǎn)生AD9826的工作時序,確保對CCD輸出信號的正確采樣。CCD連續(xù)輸出2 700個有效像素單元信號之前,先輸出64個啞元信號,此處在CCD第64個復(fù)位脈沖上升沿到來后FPGA設(shè)置采樣使能信號cds_en有效。考慮到單通道CDS模式下,模數(shù)轉(zhuǎn)換的數(shù)據(jù)會延遲3個采樣時鐘周期輸出,在第2 768個復(fù)位脈沖上升沿后拉低采樣使能cds_en,這樣才能采集到完整的2 700個CCD像素信號。由于TCD2252D輸出像元頻率為1 MHz,AD9826的相關(guān)雙采樣時鐘CDSCLK1、CDSCLK2和采樣時鐘ADCLK都設(shè)置為1 MHz。

1.4 數(shù)據(jù)緩存模塊

數(shù)據(jù)緩存模塊的功能是保證數(shù)據(jù)采集與傳輸?shù)倪B續(xù)性。由于USB接口芯片的傳輸速率和A/D轉(zhuǎn)換后的數(shù)據(jù)速率不同步,需要在兩者之間增加一個數(shù)據(jù)緩存單元。目前常用的數(shù)據(jù)緩存器件有SRAM、雙口RAM、FIFO等。高速數(shù)據(jù)采集系統(tǒng)中,常使用異步FIFO進行數(shù)據(jù)緩存,但只能對FIFO順序地讀/寫數(shù)據(jù)。當(dāng)需要存取特定單元的數(shù)據(jù)而非全部存儲空間時,系統(tǒng)的靈活性大大降低。因此本設(shè)計采用雙口RAM進行數(shù)據(jù)緩存,較好地解決了時鐘不匹配的問題。

為了有效利用FPGA片內(nèi)資源,簡化電路設(shè)計,本文在FPGA內(nèi)部定制雙口RAM來緩存模數(shù)轉(zhuǎn)換后的數(shù)字信號。EP4CE6E22C8內(nèi)部集成了30個M4K RAM塊,足夠CCD輸出一幀圖像數(shù)據(jù)(2 700×16 bit)的緩存。此處在FPGA內(nèi)部配置深度為4 096、位寬為16 bit的雙口RAM。寫時鐘和AD9826的采樣時鐘ADCLK一致,寫地址計數(shù)到2 699時,開始讀RAM。讀時鐘與寫USB端點FIFO的時鐘IFCLK一致,保證數(shù)據(jù)傳輸?shù)耐暾院头€(wěn)定性。

1.5 USB接口模塊

USB接口模塊的功能是將FPGA內(nèi)部緩存的圖像數(shù)據(jù)讀出來,傳輸給上位機。USB電路設(shè)計的主要對象是USB接口控制芯片。目前,市場上多家半導(dǎo)體廠商提供USB接口控制芯片。本系統(tǒng)采用Cypress公司的EZ-USB FX2系列USB接口控制芯片CY7C68013來傳輸圖像數(shù)據(jù)。CY7C68013是一款具有USB2.0協(xié)議的微控制處理器,最高傳輸速率可達480 Mb/s,其片內(nèi)集成USB2.0收發(fā)器、增強型的8051控制器、智能串行接口引擎(SIE)、4 KB的FIFO存儲器和可編程I/O接口。

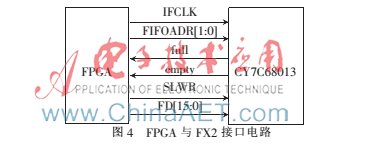

由于FX2芯片集成度高,用戶在不熟悉復(fù)雜的USB底層協(xié)議的情況下也可以順利開發(fā)USB接口設(shè)備。FX2有Slave FIFO和GPIF兩種接口方式。此處采用Slave FIFO接口方式進行數(shù)據(jù)通信。在該模式下,F(xiàn)PGA作為主機,與USB通信傳輸數(shù)據(jù)不經(jīng)過CPU的控制,而是經(jīng)過芯片內(nèi)部端點FIFO來傳輸,傳輸速度和CPU使用率更高。CY7C68013與FPGA的接口電路如圖4所示,CY7C68013的并行數(shù)據(jù)引腳和控制狀態(tài)引腳直接與FPGA接口相連即可。

USB接口設(shè)計主要是設(shè)計FPGA對USB接口芯片的邏輯控制[4]。FX2工作于Slave FIFO模式時,F(xiàn)PGA可以像對普通FIFO一樣對FX2中端點的數(shù)據(jù)緩沖區(qū)進行讀寫。FPGA提供給芯片普通的時序信號、握手信號、讀寫信號和輸出允許信號。本系統(tǒng)FX2工作于同步寫方式,接口時鐘由FPGA提供。當(dāng)SLWR有效時,F(xiàn)D總線上的數(shù)據(jù)在每個時鐘信號IFCLK上升沿時被寫入FIFO。

FPGA程序中采用狀態(tài)機實現(xiàn)同步寫Slave FIFO方式,狀態(tài)描述如下:(1)IDLE:總線空閑,當(dāng)雙口RAM中存儲的數(shù)據(jù)達到設(shè)定深度時,寫事件發(fā)生,轉(zhuǎn)到狀態(tài)state1;(2)state1:指向IN FIFO端口,激活FIFOADR[1:0],選擇端點6,然后轉(zhuǎn)向狀態(tài)state2;(3)state2:判斷FIFO“滿”標(biāo)志FLAGB的狀態(tài),如果為假,即FIFO不滿,則轉(zhuǎn)向狀態(tài)state3,否則停留在該狀態(tài);(4)state3:寫數(shù)據(jù)到總線上,激活SLWR,寫數(shù)據(jù)到FIFO并增加FIFO指針,然后轉(zhuǎn)向狀態(tài)state4;(5)state4:檢測是否有更多的數(shù)據(jù)要寫,如果有則轉(zhuǎn)向狀態(tài)state2,否則轉(zhuǎn)向狀態(tài)IDLE。

1.6 上位機模塊

上位機用來檢測USB設(shè)備的連接狀態(tài),顯示采集到的CCD數(shù)據(jù)。上位機采集有兩個采集模式:實時采集模式連續(xù)地接收來自CCD的圖像數(shù)據(jù)并顯示;單幀采集模式單次接收來自CCD的圖像數(shù)據(jù)并顯示。保存數(shù)據(jù)將當(dāng)前顯示的一幀像素數(shù)據(jù)保存在安裝目錄下。

正常情況下,系統(tǒng)的USB設(shè)計包括三個方面的程序設(shè)計:固件程序設(shè)計、設(shè)備驅(qū)動程序設(shè)計和上位機應(yīng)用程序設(shè)計[5]。Cypress公司為開發(fā)者提供了完善的軟件開發(fā)工具包,開發(fā)者只需在官方例程固件框架上修改TD_Init函數(shù)即可變?yōu)樽约旱墓碳劣赨SB驅(qū)動程序可以使用工具包自帶的通用驅(qū)動程序,只需將驅(qū)動引導(dǎo)文件中對應(yīng)的VID和PID修改成與固件一致即可。上位機程序在VS2008環(huán)境下開發(fā),用戶可以使用CYIOCTL控制函數(shù)類和CyAPI控制函數(shù)類來實現(xiàn)對USB設(shè)備讀取數(shù)據(jù)。

2 實驗分析

在室光條件下,系統(tǒng)以線陣CCD作為圖像傳感器,采集外界圖像信息。當(dāng)雙口RAM中一幀數(shù)據(jù)存儲完信號和讀使能信號有效時,USB接口芯片開始傳輸CCD圖像數(shù)據(jù),送給上位機顯示。圖5為線陣CCD傳感器部分遮光時采集到的一幀圖像,圖中低電平為CCD被遮部分的光強分布。由采集到的數(shù)據(jù)和上位機顯示可以看出采集系統(tǒng)能夠?qū)崿F(xiàn)CCD數(shù)據(jù)的實時采集。

3 結(jié)論

本文設(shè)計了基于FPGA的線陣CCD實時采集系統(tǒng),以線陣CCD作為圖像傳感器,使用CCD專用信號處理芯片AD9826對CCD信號去噪并實現(xiàn)高速A/D轉(zhuǎn)換,同時用USB接口芯片完成CCD數(shù)據(jù)的傳輸,最后在上位機上顯示采集的圖像數(shù)據(jù)。系統(tǒng)采用集成了相關(guān)雙采樣、可編程增益放大器的專用CCD處理芯片,而不是像以往那樣采用分立元件搭建模擬處理電路,并且充分利用FPGA內(nèi)部RAM作數(shù)據(jù)緩存,簡化了電路設(shè)計,減小了功耗,增加了系統(tǒng)的靈活性。系統(tǒng)擴展性較強,適用于機器視覺、非接觸測量等領(lǐng)域。

參考文獻

[1] 王慶有.CCD應(yīng)用技術(shù)[M].天津:天津大學(xué)出版社,2000.

[2] 陸榮鑑,陳豐饒.基于CPLD的彩色線陣CCD在木板色選系統(tǒng)中的應(yīng)用[J].機電工程,2012(6):737-740.

[3] 黃濤,廖勝,韓維強.基于AD9978A雙通道的CCD相機設(shè)計[J].電子技術(shù)應(yīng)用,2013,39(3):57-60.

[4] 辛鳳艷,孫曉曄.基于FPGA和線陣CCD的高速圖像采集系統(tǒng)[J].計算機技術(shù)與發(fā)展,2012(8):205-207,212.

[5] 薛圓圓,趙建領(lǐng).USB應(yīng)用開發(fā)寶典[M].北京:人民郵電出版社,2011.