摘 要: USB3.0幀同步電路設(shè)計(jì)的關(guān)鍵在于高速率下串行數(shù)據(jù)流的幀定位與數(shù)據(jù)對(duì)齊,需同時(shí)兼顧高效率和低功耗。使用Verilog HDL描述語(yǔ)言設(shè)計(jì)了一種基于多相位和并行檢測(cè)技術(shù)的幀同步電路,重點(diǎn)對(duì)并行檢測(cè)電路進(jìn)行分析和優(yōu)化。該電路在ISE中編譯和仿真,結(jié)合數(shù)據(jù)進(jìn)行分析,并將仿真結(jié)果進(jìn)行比較驗(yàn)證,證明該電路能滿(mǎn)足幀同步的速率和時(shí)序要求。

關(guān)鍵詞: USB3.0;多相位技術(shù);并行檢測(cè);幀同步;Verilog HDL

0 引言

近年來(lái),USB(通用串行總線(xiàn))作為一種標(biāo)準(zhǔn)的傳輸接口[1],應(yīng)用十分廣泛。從2008年11月首次發(fā)布USB3.0規(guī)范以來(lái),在快速存儲(chǔ)、大數(shù)據(jù)高速傳輸?shù)阮I(lǐng)域都出現(xiàn)了USB3.0[2]的身影,延續(xù)USB2.0時(shí)代的輝煌,繼續(xù)展現(xiàn)出強(qiáng)大的競(jìng)爭(zhēng)力。與USB2.0高速版本的設(shè)計(jì)[3]相比,USB3.0的復(fù)雜度大大增加,尤其是5 Gb/s的差分傳輸速率成為設(shè)計(jì)者重點(diǎn)考慮的問(wèn)題之一。高速率、低功耗是當(dāng)前芯片設(shè)計(jì)的主流趨勢(shì),在提高器件工作頻率的情況下,更需要有效地控制功耗。本文將介紹多相位技術(shù)在USB3.0幀同步系統(tǒng)設(shè)計(jì)中的應(yīng)用,通過(guò)對(duì)并行檢測(cè)電路的優(yōu)化,實(shí)現(xiàn)系統(tǒng)復(fù)雜度、實(shí)用性以及功耗方面的平衡。

1 接收電路的功能與分析

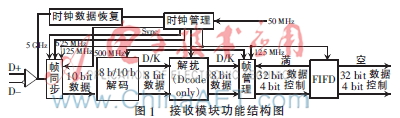

USB3.0接收部分的功能結(jié)構(gòu)如圖1所示。

為了抑制共模干擾,USB3.0的數(shù)據(jù)采用差分輸入,經(jīng)過(guò)雙端轉(zhuǎn)單端電路,分為兩路送入時(shí)鐘數(shù)據(jù)恢復(fù)(Clock Data Recovery,CDR)模塊和串轉(zhuǎn)并模塊。

CDR模塊完成從串行數(shù)據(jù)流中提取時(shí)鐘信號(hào)的功能,送至?xí)r鐘管理模塊,得到625 MHz、500 MHz和125 MHz時(shí)鐘信號(hào)供其他模塊使用。

幀同步模塊完成對(duì)高速串行數(shù)據(jù)流的并行低速化,通過(guò)并行檢測(cè)幀定界符得到幀同步信號(hào),同時(shí)控制時(shí)鐘管理模塊的時(shí)鐘輸出,完成數(shù)據(jù)的對(duì)齊處理,經(jīng)過(guò)彈性緩沖模塊得到500 MHz、10 bit的并行數(shù)據(jù)流。

幀同步模塊輸出的并行數(shù)據(jù)流先后通過(guò)8 b/10 b解碼模塊、解擾模塊得到500 MHz、8 bit數(shù)據(jù)流與控制信號(hào);通過(guò)位寬拼接處理最終得到125 MHz、36 bit的數(shù)據(jù)流(其中包含32 bit數(shù)據(jù)和4 bit控制位)寫(xiě)入數(shù)據(jù)FIFO,供LINK層讀取使用。

2 幀同步模塊的設(shè)計(jì)及要點(diǎn)

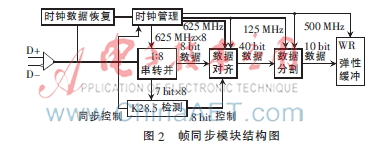

幀同步模塊是接收模塊的難點(diǎn),主要由以下功能模塊組成:多相位串轉(zhuǎn)并模塊、并行幀定界符檢測(cè)模塊、并行數(shù)據(jù)流對(duì)齊模塊、彈性緩沖模塊。各大模塊及相關(guān)時(shí)鐘結(jié)構(gòu)電路如圖2所示。其中,串轉(zhuǎn)并模塊和并行檢測(cè)模塊是本設(shè)計(jì)的優(yōu)化重點(diǎn)。電路選用XLINX公司的Virtex-5芯片作為設(shè)計(jì)與測(cè)試平臺(tái)。

2.1 基于多相位技術(shù)的串轉(zhuǎn)并模塊設(shè)計(jì)

傳統(tǒng)的低速串轉(zhuǎn)并電路采用移位寄存器實(shí)現(xiàn),電路的功耗與工作時(shí)鐘成線(xiàn)性關(guān)系。USB3.0的輸入信號(hào)高達(dá)5 Gb/s,移位寄存器產(chǎn)生的功耗很大,并且工藝要求很高,而0.15 m CMOS工藝條件只能達(dá)到3.0 Gb/s的頻率,繼續(xù)提升工作頻率極易引起電路的不穩(wěn)定。因此,有效地降低器件工作時(shí)鐘頻率,在降低器件功耗和降低生產(chǎn)工藝要求方面具有重要意義,同時(shí)對(duì)相同工藝下提升器件的性能也非常有效。

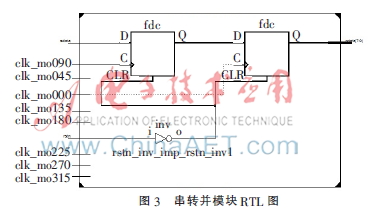

多相位技術(shù)的原理為:利用PLL將CDR恢復(fù)得到的f頻率時(shí)鐘分成多個(gè)頻率為f/N,彼此相位間隔為360°/N的時(shí)鐘信號(hào),利用這N個(gè)時(shí)鐘對(duì)串行數(shù)據(jù)流進(jìn)行分時(shí)采樣,在相移為0°的f/N頻率時(shí)鐘同步下,合并為N bit的數(shù)據(jù)。這種技術(shù)的優(yōu)勢(shì)在于:在不增加原有功能復(fù)雜度的情況下,利用PLL降低CMOS器件的運(yùn)行時(shí)鐘,從而降低功耗。PLL的引入,能夠一定程度上改善恢復(fù)時(shí)鐘的抖動(dòng)。在PLL設(shè)計(jì)中,當(dāng)分頻值N取2的冪次方時(shí),可有效簡(jiǎn)化設(shè)計(jì),在此N取2^3=8。

使用Verilog HDL[4]語(yǔ)言對(duì)1:8多相位串轉(zhuǎn)并模塊進(jìn)行描述,部分關(guān)鍵代碼為:

always@(posedge clk_XXX or negedge rstn)begin

if(!rstn)pdata[n]<=1′b0;

else pdata[n]<=sdata_i;

end

其中clk_XXX代表clk_000~clk_315這8個(gè)相位間隔為45°的時(shí)鐘。采樣得到的數(shù)據(jù)以8 bit為單位送入并行檢測(cè)模塊。

經(jīng)過(guò)ISE綜合后模塊非常簡(jiǎn)潔,RTL電路如圖3所示。

2.2 優(yōu)化并行幀定界符檢測(cè)模塊設(shè)計(jì)

根據(jù)USB3.0規(guī)范,傳輸?shù)臄?shù)據(jù)采用控制碼K28.5作為幀定界符。它的特殊性在于:在所有選定使用的控制碼與數(shù)據(jù)碼中,有且只有K28.5存在5個(gè)連續(xù)的高電平信號(hào)‘1’。因此,許多采用8 b/10 b編碼的傳輸系統(tǒng)都將其作為幀定界符。在傳輸?shù)臄?shù)據(jù)流中,檢測(cè)到“001111010”就可以判定新一幀的開(kāi)始。

USB3.0發(fā)送部分的數(shù)據(jù)經(jīng)過(guò)8 b/10 b編碼后,數(shù)據(jù)塊由8 bit為單位轉(zhuǎn)換為10 bit為單位,常用的做法為:接收端在f/10的工作時(shí)鐘驅(qū)動(dòng)下,并行檢測(cè)10個(gè)相鄰位置的10 bit數(shù)據(jù)。通過(guò)并行的方式,從而降低電路的運(yùn)行速度要求,實(shí)際是以空間換時(shí)間的思想。雖然電路工作頻率降低,但整體功耗因電路規(guī)模的相應(yīng)增大而沒(méi)有減小。

通過(guò)對(duì)并行檢測(cè)電路的分析可以發(fā)現(xiàn):假定串轉(zhuǎn)并模塊采用1:N結(jié)構(gòu),并行檢測(cè)模塊對(duì)M bit數(shù)據(jù)塊進(jìn)行檢測(cè),檢測(cè)單元的規(guī)模為N×M bit。在并行度M bit相同條件下,N越大,需要的邏輯運(yùn)算單元就越多。串轉(zhuǎn)并模塊選擇1:8的比例,不僅可以簡(jiǎn)化PLL設(shè)計(jì),同時(shí)也能降低邏輯運(yùn)算單元的消耗。

其次,減少檢測(cè)數(shù)據(jù)塊的并行度M也是重要途徑。根據(jù)K28.5的特點(diǎn),在數(shù)據(jù)正確傳輸?shù)那疤嵯轮恍铏z測(cè)其中7 bit,即“0011111”或者“1111101”[5]就能判定為K28.5碼。取M=7 bit,則只需要8×7=56 bit邏輯運(yùn)算單元,相比未優(yōu)化前的10×10=100 bit邏輯運(yùn)算單元減少44%,簡(jiǎn)化了電路的結(jié)構(gòu),能夠一定程度地提升器件的運(yùn)行效率。

2.3 并行數(shù)據(jù)流對(duì)齊模塊設(shè)計(jì)

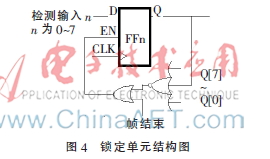

并行檢測(cè)模塊檢測(cè)到幀定界符后,需通過(guò)鎖定單元[6]鎖定當(dāng)前的數(shù)據(jù)流分塊方式,鎖定單元結(jié)構(gòu)設(shè)計(jì)如圖4所示。

鎖定機(jī)構(gòu)的工作原理為:當(dāng)某一檢測(cè)單元成功檢測(cè)到幀定界符K28.5的前7 bit,便可推斷數(shù)據(jù)流3 bit后即為實(shí)際所需數(shù)據(jù)流的起始位置,鎖定單元在下一時(shí)鐘沿鎖定當(dāng)前檢測(cè)結(jié)果不再更改,并根據(jù)鎖定的結(jié)果在對(duì)應(yīng)位置每次取出10 bit并行數(shù)據(jù)送至下級(jí)電路,直到檢測(cè)到當(dāng)前幀結(jié)束或者復(fù)位解除鎖定。

鎖定單元關(guān)鍵代碼如下所示:

wire comma_detect[n]=detect_data_X==7′b1111100;

always@(posedge clk or negedge rstn)begin

if(!rstn)

comma_lock[n]<=1′b0;

else if((!(|comma_lock[7:0]))|fram_end)

comma_lock[n]<=comma_detect[n];

else

comma_lock[n]<=comma_lock[n];

end

其中,n為0~7,detect_data_X表示第0~7個(gè)檢測(cè)單元。

由于串轉(zhuǎn)并模塊輸出為8 bit并行數(shù)據(jù),根據(jù)USB3.0規(guī)范,實(shí)際送入彈性緩沖須為10 bit,因此需要使用位寬轉(zhuǎn)換電路對(duì)數(shù)據(jù)流位寬進(jìn)行轉(zhuǎn)換。方法為:將8 bit位寬拼接成40 bit位寬,通過(guò)判斷鎖定單元輸出的comma_lock信號(hào),重新選取對(duì)齊后的40 bit,最后分割成實(shí)際需要的10 bit位寬輸出。

3 仿真及驗(yàn)證

編寫(xiě)test bench,改變串行數(shù)據(jù)流中K28.5的位置,模擬發(fā)送數(shù)據(jù)幀,在ISim中對(duì)設(shè)計(jì)的電路進(jìn)行仿真驗(yàn)證,仿真波形如圖5所示。

經(jīng)過(guò)8組不同位置數(shù)據(jù)(在此只貼出2個(gè)結(jié)果)的對(duì)比可以看出,在不同的數(shù)據(jù)流中,幀定界符K28.5的位置總能夠被正確檢測(cè),通過(guò)數(shù)據(jù)對(duì)齊模塊后成功分離出后續(xù)模塊所需10 bit并行數(shù)據(jù),結(jié)果完全正確,且滿(mǎn)足運(yùn)行500 MHz的運(yùn)行速度要求。

4 結(jié)論

多相位技術(shù)能夠顯著降低器件的工作頻率,從而減少功耗,同時(shí)也可以降低制造器件的工藝難度;并行處理技術(shù)是當(dāng)前高速電路發(fā)展的趨勢(shì),合理地利用編碼自身特點(diǎn),進(jìn)行針對(duì)性的優(yōu)化,能夠使電路更加簡(jiǎn)潔,運(yùn)行速度更快。這兩者對(duì)于提高器件的性能而言,都具有十分重要的現(xiàn)實(shí)意義。

參考文獻(xiàn)

[1] Don Anderson Dave Dzatko.USB系統(tǒng)體系(第二版)[M].北京:中國(guó)電力出版社,2003.

[2] Hewlett-Packard Company, Intel, et al. Universal serial bus 3.0 specification Revision1.0[R]. USA: Hewlett-Packard Company. 2008.

[3] 王永,白雪飛,方毅,等.基于UTMI協(xié)議的USB2.0收發(fā)器邏輯電路設(shè)計(jì)[J].微型機(jī)與應(yīng)用,2014,33(10):13-15,19.

[4] 夏字聞.Verilog數(shù)字系統(tǒng)設(shè)計(jì)(第二版)[M].北京:北京航空航天大學(xué)出版社,2008.

[5] 楊卿.RapidIO高速互聯(lián)接口的設(shè)計(jì)研究與應(yīng)用[D].成都:電子科技大學(xué),2009.

[6] 劉昭,金德鵬,曾烈光.基于連續(xù)性判別的并行幀同步系統(tǒng)[J].電子學(xué)報(bào),2005,33(7):1177-1182.