摘要:通過對北斗導(dǎo)航電文BCH糾錯編譯碼方式的深入理解和研究,提出了一種基于并行數(shù)據(jù)處理的BCH譯碼器的設(shè)計方案。該方案利用FPGA對BCH電文進行并行處理,在一個時鐘周期內(nèi)實現(xiàn)電文譯碼,提高了BCH解碼模塊的譯碼效率;同時給出了系統(tǒng)各個模塊的Modelsim仿真結(jié)果與分析,驗證了設(shè)計的可行性。本設(shè)計對提高接收機的基帶數(shù)據(jù)處理性能有一定的參考和指導(dǎo)意義。

關(guān)鍵詞:北斗導(dǎo)航電文;BCH譯碼;并行處理;譯碼效率

0引言

北斗衛(wèi)星導(dǎo)航系統(tǒng)是中國正在實施的自主發(fā)展、獨立運行的全球衛(wèi)星導(dǎo)航系統(tǒng),是繼美國的全球定位系統(tǒng)(GPS)、俄羅斯的格洛納斯衛(wèi)星導(dǎo)航系統(tǒng)(GLONASS)之后第三個成熟的衛(wèi)星導(dǎo)航系統(tǒng)[1]。2013年12月,《北斗系統(tǒng)公開服務(wù)性能規(guī)范(10版)》和《北斗系統(tǒng)空間信號接口控制文件(20版)》正式發(fā)布,意味著北斗衛(wèi)星導(dǎo)航系統(tǒng)對區(qū)域提供的服務(wù)正式進入規(guī)范標準階段。其中空間信號接口控制文件對北斗衛(wèi)星導(dǎo)航系統(tǒng)的目標和B1I、B2I信號結(jié)構(gòu)進行了詳細定義[2]。

隨著北斗系統(tǒng)的不斷完善以及應(yīng)用的深入,用戶對北斗接收機的性能要求越來越高。為了提高接收機性能,設(shè)計方案必須考慮處理器的資源、速度以及存儲空間等參數(shù)。如果接收機的大部分基帶信號能夠通過FPGA并行處理,那么對提高接收機的性能就具有非常大的意義。本文根據(jù)北斗導(dǎo)航電文BCH譯碼原理,提出了一種基于并行數(shù)據(jù)處理的快速BCH譯碼方式,并在FPGA系統(tǒng)上實現(xiàn),提高了譯碼器效率。通過Modelsim對系統(tǒng)模塊的功能仿真驗證了設(shè)計的可行性,該設(shè)計方案具有一定的工程應(yīng)用參考價值。

1導(dǎo)航電文糾錯編碼數(shù)據(jù)格式

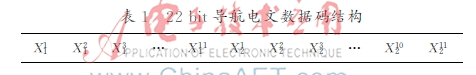

導(dǎo)航電文采取BCH(15,11,1)碼加交織方式進行糾錯[3]。BCH碼位長為15 bit,信息位11 bit,糾錯能力1 bit,其生成多項式為g(X)=X4+X+1。一組22 bit的導(dǎo)航電文數(shù)據(jù)碼(表1所示),進入糾錯編碼系統(tǒng)后,按照每11 bit順序分成兩組后進行BCH(15,11,1)編碼、交織操作,輸出30 bit的交織編碼。

每兩組 BCH(15,11,1)碼按比特交錯方式組成30 bit碼長的交織碼,30 bit碼長的交織碼編碼結(jié)構(gòu)如表2所示。

表1和表2中:Xji為信息位,i表示第i組 BCH碼,j表示第i組 BCH 碼中的第j個信息位;Pmi為校驗位,i表示第i組BCH 碼;m 表示第i組BCH 碼中的第m個校驗位。

2導(dǎo)航電文糾錯譯碼原理

接收機接收到數(shù)據(jù)碼信息后按每1 bit順序進行串/并變換,然后進行 BCH(15,11,1)糾錯譯碼,再對交織部分按每11 bit順序進行并/串變換,組成22 bit信息碼,其譯碼流程如圖1所示。

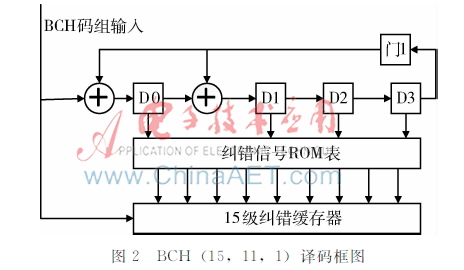

BCH(15,11,1)譯碼框圖如圖2所示,其中,初始時移位寄存器清零,BCH 碼組逐位輸入到除法電路和15級糾錯緩存器中,當BCH 碼的15位全部輸入后,糾錯信號ROM表利用除法電路的4級移位寄存器的狀態(tài)D3、D2、D1、D0 查表,得到15位糾錯信號與15級糾錯緩存器里的值模二加,最后輸出糾錯后的信息碼組[2,4]。糾錯信號的ROM表詳見參考文獻[2]。

3并行數(shù)據(jù)處理的糾錯譯碼系統(tǒng)設(shè)計

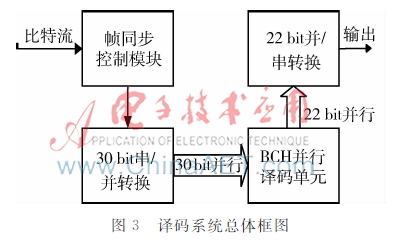

3.1系統(tǒng)總體方案

從傳統(tǒng)的北斗導(dǎo)航電文BCH(15,11,1)譯碼原理(圖2所示)可知,BCH譯碼器每一個時鐘周期只處理一位碼字,需采用頻繁的循環(huán)移位實現(xiàn)譯碼,如果碼組多了,將占用大量CPU資源并影響接收機對信號實時處理的要求[5]。鑒于傳統(tǒng)譯碼方式的缺點,將圖2所示原理框圖進行改進,提出并行處理的一種運算方法。改進的糾錯譯碼系統(tǒng)總體框圖如圖3所示。

考慮到數(shù)據(jù)是以數(shù)據(jù)流的格式輸入到糾錯譯碼系統(tǒng)中,所以直接將數(shù)據(jù)流給并行數(shù)據(jù)處理的譯碼單元并不現(xiàn)實。因此在單元前級加一級30 bit的串/并轉(zhuǎn)換模塊,將串行數(shù)據(jù)流轉(zhuǎn)換成并行數(shù)據(jù);為保證輸出同樣是數(shù)據(jù)流格式,譯碼單元后級再加一級22 bit的并/串轉(zhuǎn)換模塊。在實際應(yīng)用過程中,為使信號保持同步狀態(tài),需要加入幀同步模塊。并行處理的BCH譯碼系統(tǒng),先將輸入的30 bit的交織碼數(shù)據(jù)流進行30 bit的串/并轉(zhuǎn)換,輸出30位并行的數(shù)據(jù)后輸入BCH譯碼單元進行并行譯碼,在一個時鐘周期輸出22 bit的導(dǎo)航電文信息碼進行后面的導(dǎo)航解算。

3.2BCH并行譯碼單元設(shè)計

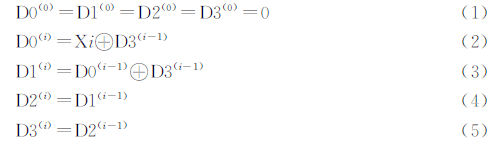

假設(shè)BCH譯碼模塊(如圖2所示)輸入的15比特碼為:{X1、X2、X3、X4…X13、X14、X15},那么根據(jù)圖2的數(shù)據(jù)流動形式,BCH碼與糾錯信號標識{D3、D2、D1、D0}之間的關(guān)系可以表示為:

從最高位X1~X15順序移位,最終得到BCH碼對應(yīng)的糾錯標識信號{D3D2D1D0},上式中從i=1開始迭代運算,最后當i=15時,可以分別得到D3、D2、D1、D0的表達式[2,6]:

![JFSJOJO61CQD])R9M5UGFK3.png JFSJOJO61CQD])R9M5UGFK3.png](http://files.chinaaet.com/images/2016/03/02/6359254870573900004319377.png)

其中X1 X2…X14 X15表示15 bit的BCH碼組。⊕代表模2加運算。

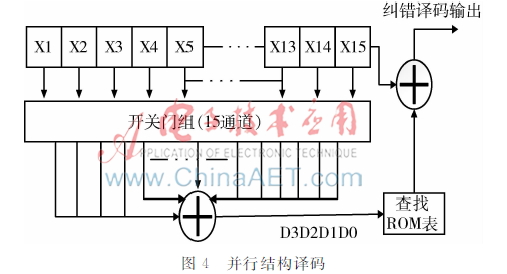

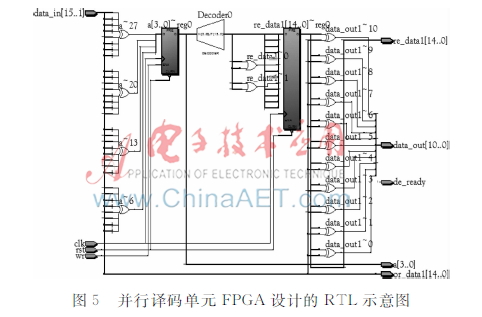

圖4并行結(jié)構(gòu)譯碼根據(jù)式(6)~(9),將圖2的譯碼框圖結(jié)構(gòu)等效為圖4所示并行數(shù)據(jù)處理的譯碼結(jié)構(gòu)框圖[7]。模塊輸入端數(shù)據(jù)采用15位的并行數(shù)據(jù)輸入,在15位的數(shù)據(jù)輸入之后,經(jīng)過15通道的開關(guān)門組對輸入的數(shù)據(jù){X1、X2、X3…X14、X15}進行選擇后進行模2運算得到相應(yīng)的D3、D2、D1、D0值;其次根據(jù)糾錯標識信號D3D2D1D0查找糾錯標識信號對應(yīng)的ROM表,得到15位的糾錯信號;最后將所得15位糾錯信號與輸入的15位數(shù)據(jù)碼進行模2運算后輸出糾錯譯碼。在FPGA系統(tǒng)中,該譯碼單元可以在一個周期內(nèi)算出D3 D2 D1 D0,大大提高了運算速度。圖5是并行譯碼單元的電路RTL視圖。

4設(shè)計結(jié)果與仿真

本設(shè)計采用Verilog語言[8],在Quartus II 110開發(fā)軟件平臺下完成,仿真軟件為Quartus II 110自帶的Modelsim 66d版本。

4.130 bit串/并轉(zhuǎn)換器仿真

本設(shè)計30 bit串/并轉(zhuǎn)換器目的在于將輸入的一字數(shù)據(jù)流形式的30 bit交織編碼轉(zhuǎn)換成30 bit的并行數(shù)據(jù)輸出。模塊的Modelsim仿真圖如圖6所示。

在系統(tǒng)時鐘上升沿時將實際記錄的衛(wèi)星電文以數(shù)據(jù)流的形式從data_in輸入,在完成30 bit的導(dǎo)航電文字段接收后,由data_out并行輸出30 bit數(shù)據(jù),同時在輸出數(shù)據(jù)使能dout_en產(chǎn)生脈沖。

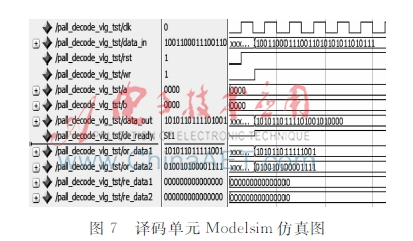

4.2并行數(shù)據(jù)譯碼單元仿真

并行數(shù)據(jù)譯碼單元根據(jù)圖4原理設(shè)計。實際設(shè)計中將兩路的并行譯碼單元結(jié)構(gòu)進行優(yōu)化和合并,設(shè)計出支持30 bit的輸入的并行譯碼單元,能夠?qū)崿F(xiàn)將30 bit并行輸入的數(shù)據(jù)碼進行22 bit BCH譯碼輸出。其中30 bit交織碼的解交織過程在模塊內(nèi)部實現(xiàn)。模塊的Modelsim仿真圖如圖7所示。

將實際測試得到的一個完整無誤碼的30 bit北斗導(dǎo)航電文字段作為仿真測試數(shù)據(jù)源并行輸入。如圖7所示,在一個時鐘周期內(nèi),譯碼單元將并行30 bit數(shù)據(jù)解交織為or_data1和or_data2的兩路15 bit數(shù)據(jù),并根據(jù)本文設(shè)計的并行譯碼器分別計算出兩路信號的糾錯標識信號a、b。由于輸入數(shù)據(jù)不存在誤碼,糾錯標識信號和糾錯信號re_data1、re_data2均為0,直接由兩路數(shù)據(jù)中的11 bit信息位拼接得到22 bit數(shù)據(jù)輸出data_out。

將輸入信號的X61位信息取反得到具有1 bit誤碼的導(dǎo)航電文字段。根據(jù)表1、表2可知,誤碼出現(xiàn)在第一組BCH碼的第6個信息位。由圖8仿真結(jié)果可以看出,其中第一組信號糾錯標識變成1010,通過查找ROM表發(fā)現(xiàn)第一組BCH的第六位數(shù)據(jù)存在錯誤,進行糾錯得到的BCH譯碼結(jié)果為:data_out=1010110111101001010000,與圖7譯碼結(jié)果一樣,證明實現(xiàn)糾錯功能。

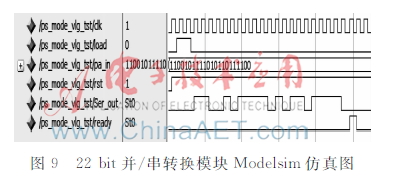

4.322 bit并/串轉(zhuǎn)換器仿真

將譯碼單元的輸出22 bit數(shù)據(jù)進行并/串轉(zhuǎn)換為數(shù)據(jù)流輸出到后級進行電文解算。若后級的處理器支持并行數(shù)據(jù)的輸入,則并/串轉(zhuǎn)換模塊可以省去。模塊的Modelsim仿真結(jié)果如圖9所示。

北斗GEO衛(wèi)星信號每比特電文長2 ms,一個導(dǎo)航字持續(xù)60 ms,非GEO衛(wèi)星信號每比特電文長20 ms,一個導(dǎo)航字持續(xù)600 ms。傳統(tǒng)譯碼器需要時刻記錄導(dǎo)航電文比特流,通過復(fù)雜的移位實現(xiàn)譯碼,因此一臺12路跟蹤通道的接收機需要12路獨立譯碼器。而本文設(shè)計的并行譯碼器譯碼周期短,只需在各通道增加串并轉(zhuǎn)換模塊和狀態(tài)選擇機制即可實現(xiàn)譯碼器的分時復(fù)用,提高了譯碼器使用效率。傳統(tǒng)接收機和并行譯碼接收機的性能對比如表3所示。

5結(jié)論

經(jīng)過仿真測試,驗證了本文提出的基于FPGA的北斗導(dǎo)航電文譯碼器設(shè)計方案的可行性。該方案采用并行處理方式,在保證譯碼準確率的前提下有效提高了譯碼器的工作效率。此外,該譯碼器采用模塊化設(shè)計,易于集成至接收機中,對北斗接收機譯碼模塊設(shè)計有一定的參考意義。

參考文獻

[1] 邢金清,陳泓吉.北斗衛(wèi)星導(dǎo)航系統(tǒng)現(xiàn)狀及發(fā)展意義[J].黑龍江科技信息,2015(13):97.

[2] 中國衛(wèi)星導(dǎo)航系統(tǒng)管理辦公室.北斗衛(wèi)星導(dǎo)航系統(tǒng)空間信號接口控制文件公開服務(wù)信號(2.0版)[Z].2013.

[3] 寧楠,鮑慧,宋文妙,等.一種基于FPGA的糾錯編譯碼器的設(shè)計與實現(xiàn)[J].通信技術(shù),2008,41(8):95-97,100.

[4] 王迪,郝士琦,朱斌,等.“北斗”2代B1I信號導(dǎo)航電文分析[J].航天電子對抗,2013,29(6):30-32.

[5] 連帥,閆利軍,孫科,等.北斗2代衛(wèi)星導(dǎo)航電文糾錯校驗設(shè)計與仿真[J].計算機測量與控制,2010,18(10):2344-2347.

[6] 藺曉龍,何文濤,徐建華,等.多模 GNSS接收機中BCH(15,11,1)并行解碼算法[J].微電子學與計算機,2014(2):50-53.

[7] 金婕,于敦山.高速并行BCH譯碼器的VLSI設(shè)計[J].北京大學學報(自然科學版),2009,45(2):233-237.

[8] 夏宇聞. Verilog數(shù)字系統(tǒng)設(shè)計教程[M].北京:北京航空航天大學出版社, 2008.