徐成強(qiáng), 何小海, 卿粼波, 吳小強(qiáng)

(四川大學(xué) 電子信息學(xué)院 圖像信息研究所,四川 成都 610065)

摘要:設(shè)計(jì)并實(shí)現(xiàn)了一種基于FPGA硬件平臺(tái)的Bayer到RGB格式圖像數(shù)據(jù)轉(zhuǎn)換實(shí)時(shí)采集顯示系統(tǒng)。該系統(tǒng)能夠?qū)η岸?a class="innerlink" href="http://forexkbc.com/tags/Camera Link" title="Camera Link" target="_blank">Camera Link接口的CMOS相機(jī)采集的分辨率為1 920×1 080、幀率100 f/s以上的Bayer格式圖像進(jìn)行實(shí)時(shí)處理,并且將處理得到的RGB彩色圖像數(shù)據(jù)通過DVI顯示器以60 f/s的幀率實(shí)時(shí)顯示。根據(jù)FPGA并行處理能力強(qiáng)的特點(diǎn),采用像素矩陣模板實(shí)現(xiàn)了Bayer到RGB的彩色圖像插值算法,實(shí)現(xiàn)了高分辨率、高幀率彩色圖像的實(shí)時(shí)采集顯示。

關(guān)鍵詞:FPGA;Bayer濾波;DVI顯示;Camera Link

0引言

中央高校基本科研業(yè)務(wù)費(fèi)(2015SCU04A11)高分辨率、高幀率圖像的實(shí)時(shí)處理在軍事、通信、航天航空、醫(yī)學(xué)等領(lǐng)域有著越來越廣泛的應(yīng)用[1],RGB彩色圖像是計(jì)算機(jī)、攝像機(jī)等設(shè)備最常采用的色彩空間,并且彩色圖像更有利于進(jìn)行觀察與分析。在圖像的實(shí)時(shí)處理過程中,圖像數(shù)據(jù)量大,要求的運(yùn)算速率高[2],因此選用善于高速并行處理大量數(shù)據(jù)的FPGA作為處理器是非常合適的。本文選用自主設(shè)計(jì)的以Xilinx公司Virtex5系列的xc5vfx70t芯片為核心的14層硬件平臺(tái)。xc5vfx70t的最高運(yùn)行頻率為550 MHz,片內(nèi)時(shí)鐘、slice、存儲(chǔ)等可用資源非常豐富,因此用于實(shí)現(xiàn)分辨率為1 920×1 080、幀率為100 f/s以上的Bayer到RGB彩色圖像轉(zhuǎn)換的實(shí)時(shí)采集顯示是非常適合的。根據(jù)Bayer格式圖像中R、G、B分量與鄰近像素的R、G、B分量存在高度相關(guān)性的特點(diǎn)[3],本文設(shè)計(jì)的彩色圖像轉(zhuǎn)換算法是基于像素矩陣模板的插值算法,能夠很好地實(shí)現(xiàn)彩色圖像的恢復(fù)。

1CMOS圖像傳感器

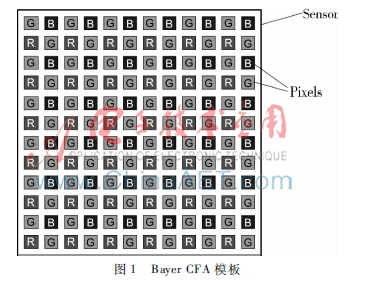

出于對成本及體積的考慮,目前大部分?jǐn)?shù)字圖像采集系統(tǒng)都是采用一塊CCD/CMOS來作為接收圖像的傳感器,在傳感器表面會(huì)覆蓋CFA(Color Filter Array)顏色濾波矩陣以得到每個(gè)感光單元的分量灰度值[4]。基于FPGA的彩色圖像采集顯示系統(tǒng)一般由系統(tǒng)采集前端、FPGA內(nèi)部各處理模塊以及顯示三個(gè)部分組成。本系統(tǒng)前端采用的CMOS相機(jī)為Basler公司的acA2000340kc,該相機(jī)支持的最大分辨率為2 046×1 086,最大幀率為340 f/s,其成像CFA模板如圖1所示。acA2000340kc為Camera Link接口,支持三種配置模式即Base、Medium和Full,三種模式的最大數(shù)據(jù)帶寬分別為255 MB/s、510 MB/s、680 MB/s[5],本文選用的是Full傳輸模式。

2Bayer插值算法

實(shí)現(xiàn)Bayer到RGB圖像格式轉(zhuǎn)換的算法有很多,比如鄰域插值法、線性插值法[67]、神經(jīng)網(wǎng)絡(luò)插值法等,好的插值方法對高質(zhì)量圖像的獲取非常重要。一般而言,選用的方法越復(fù)雜,產(chǎn)生的圖像質(zhì)量越高,但是同時(shí)也需要付出更大的處理時(shí)間代價(jià),在硬件中的實(shí)現(xiàn)也更困難。因此在處理速度與成像質(zhì)量之間找到一種平衡是非常有必要的。文獻(xiàn)[3]采用的是基于自適應(yīng)的局部去馬賽克算法,雖然處理效果好,但是算法復(fù)雜,難以在FPGA中實(shí)時(shí)實(shí)現(xiàn);文獻(xiàn)[4]中采用的是基于像素矩陣模板的插值算法,處理圖像的分辨率為1 280×1 024;文獻(xiàn)[6]中采用的是基于像素矩陣模板的插值算法,能夠基本保證實(shí)時(shí)地處理分辨率為1 280×1 024的圖像。綜合考慮以上情況,本文采用基于像素矩陣模板的線性插值法,該方法運(yùn)算量小,成像質(zhì)量良好,易于在FPGA中實(shí)現(xiàn)。

由圖1可知Bayer CFA模板中可能出現(xiàn)的3×3像素矩陣有4種情況,如圖2所示,其中(a)和(b)的中心像素點(diǎn)為G分量,(c)為R分量,(d)為B分量。本文針對不同情況下的像素矩陣,具體設(shè)計(jì)了不同的插值方法。

2.1中心像素為G分量

中心像素為G分量的包含圖2中的(a)和(b)兩種情況。在這里為了方便說明,以(a)為例,用Glu、Gld、Gru、Grd分別代表左上、左下、右上、右下的4個(gè)G值,左右兩邊的R值用Rl和Rr表示,上下方向的兩個(gè)B值用Bu和Bd表示,當(dāng)前中心點(diǎn)的G值為Gc,對中心點(diǎn)Gc進(jìn)行插值之后得到的三個(gè)分量的值就用R、G、B來表示,之后的(b)、(c)、(d)中的像素點(diǎn)命名方式與此類似。本文在考慮了3×3像素矩陣相鄰像素之間的影響之后,針對圖(a)所示的情況,改進(jìn)設(shè)計(jì)的插值方法如下:

G=1/2Gc+1/8(Glu+Gld+Gru+Grd)(1)

R=1/2Rl+1/2Rr(2)

B=1/2Bu+1/2Bd(3)

(b)與(a)的區(qū)別僅在于R和B分量的像素點(diǎn)位置剛好相反,改進(jìn)方法與(a)的情況類似,這里就不再贅述。

2.2中心像素為R(B)分量

以圖2中的(c)為例進(jìn)行說明,插值的方法如下:

G=1/4(Gu+Gd+Gl+Gr)(4)

R=1/4(Rlu+Rld+Rru+Rrd)(5)

B=Bc(6)

(d)和(c)的區(qū)別也僅在于R和B分量的像素點(diǎn)位置剛好相反,改進(jìn)方法與(c)的類似,這里也不再贅述。

3FPGA硬件設(shè)計(jì)與實(shí)現(xiàn)

3.1硬件系統(tǒng)結(jié)構(gòu)

本文綜合考慮所用FPGA的資源實(shí)現(xiàn)Bayer到RGB圖像轉(zhuǎn)換的硬件系統(tǒng)整體架構(gòu)如圖3所示。系統(tǒng)前端由Camera Link相機(jī)將采集的視頻數(shù)據(jù)傳送至三片DS90CR288A進(jìn)行差分信號(hào)的轉(zhuǎn)換,轉(zhuǎn)換后的64 bit RGB單色數(shù)據(jù)傳送至FPGA,F(xiàn)PGA利用兩組DDR2對圖像數(shù)據(jù)進(jìn)行緩存、處理,最后控制DVI顯示芯片CH7301C進(jìn)行實(shí)時(shí)顯示。

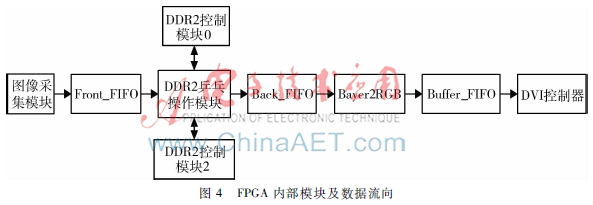

FPGA內(nèi)部首先通過圖像采集模塊將圖像傳送至Front_FIFO中,然后由乒乓操作模塊將Front_FIFO中的數(shù)據(jù)讀出進(jìn)行乒乓操作處理后暫存在DDR2中,實(shí)現(xiàn)前后速度的匹配,再將數(shù)據(jù)輸出至Back_FIFO中。Bayer2RGB模塊讀取Back_FIFO中的數(shù)據(jù)進(jìn)行處理之后將生成的RGB彩色圖像數(shù)據(jù)傳送至Buffer_FIFO中,最后由DVI顯示模塊將數(shù)據(jù)讀出以進(jìn)行顯示。FPGA內(nèi)部各模塊及其數(shù)據(jù)流向如圖4所示。

3.2Bayer2RGB模塊

Bayer2RGB模塊的內(nèi)部結(jié)構(gòu)框圖如圖5所示,由Back_FIFO輸出的8 bit位寬的圖像數(shù)據(jù)shiftin首先傳送到一個(gè)三行線性移位寄存器組進(jìn)行緩存,同時(shí)shiftin會(huì)進(jìn)入一個(gè)行、列計(jì)算模塊對圖像的行、列進(jìn)行計(jì)數(shù),由row_cnt和col_cnt兩個(gè)變量輸出。由于本文的算法是基于像素矩陣塊的,因此在緩存完三行完整的圖像數(shù)據(jù)后才能夠開始進(jìn)行Bayer到RGB的圖像插值算法處理。圖4FPGA內(nèi)部模塊及數(shù)據(jù)流向

三行移位寄存器組的結(jié)構(gòu)如圖6所示,輸入數(shù)據(jù)shiftin在時(shí)鐘上升沿傳送給line1[0],同時(shí)line1、line2和line3均要進(jìn)行線性移位,line1[1919]移至line2[0],同樣地,line2[1919]移至line3[0],系統(tǒng)每次取出圖6中虛線框內(nèi)的像素矩陣塊與行、列計(jì)算模塊的row_cnt和col_cnt一起傳送至插值算法模塊進(jìn)行處理。

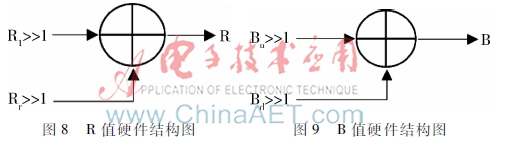

插值算法模塊根據(jù)中心點(diǎn)即line2[1918]的行、列值奇偶情況來選擇相應(yīng)的運(yùn)算處理,總共有4種情況,分別對應(yīng)圖2所示的四種情況。本系統(tǒng)使用移位運(yùn)算和加法運(yùn)算對每種情況的插值算法設(shè)計(jì)了相應(yīng)的硬件實(shí)圖7G值硬件結(jié)構(gòu)圖現(xiàn)結(jié)構(gòu),這里以圖2中的(a)為例,硬件結(jié)構(gòu)如圖7、8、9所示,分別對應(yīng)公式(1)、(2)、(3)。

本文最終的實(shí)驗(yàn)測試結(jié)果如圖10所示,圖(a)為整個(gè)系統(tǒng)的整體成像圖,圖(b)為Bayer2RGB模塊處理后的彩色圖像,圖(c)為實(shí)物圖,對比可知系統(tǒng)的實(shí)時(shí)彩色還原效果良好。

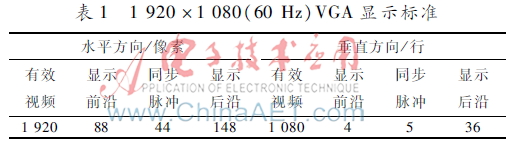

系統(tǒng)前端Camera Link接口的CMOS相機(jī)采集幀率為120 f/s,分辨率為1 920×1 080,DVI顯示幀率最大為60 f/s,視頻電子標(biāo)準(zhǔn)協(xié)會(huì)VESA制

定的顯示分辨率標(biāo)準(zhǔn)如表1所示,根據(jù)表中的數(shù)據(jù)可以計(jì)算出顯示時(shí)鐘頻率=2 200 (clk)1125(h)60(f/s)=148.5 MHz。

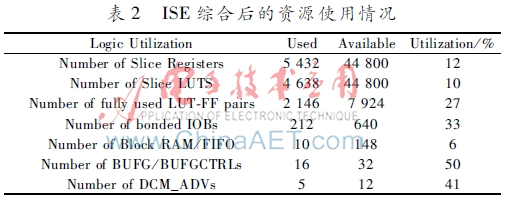

由于Bayer2RGB模塊需要緩存3行數(shù)據(jù),處理時(shí)鐘與DVI時(shí)鐘頻率一致為148.5 MHz,因此可以通過公式(7)粗略算出總延時(shí)t約為38.8 ns,完全實(shí)現(xiàn)了真正的高分辨率高幀率實(shí)時(shí)彩色圖像采集顯示。由本文算法可知采用FPGA的并行流水線結(jié)構(gòu),運(yùn)算速度快,時(shí)延小,完全可以對分辨率更高的視頻數(shù)據(jù)進(jìn)行實(shí)時(shí)彩色圖像的采集顯示。本系統(tǒng)在Xilinx的FPGA開發(fā)工具ISE 10.1下綜合之后的資源使用情況如表2所示,本系統(tǒng)僅消耗了xc5vfx70t中12%的slice資源,6%的Block RAM資源。

![]()

5結(jié)論

本文利用FPGA邏輯資源豐富、并行處理能力強(qiáng)等特點(diǎn),實(shí)現(xiàn)了高分辨率高幀率的實(shí)時(shí)彩色圖像采集顯示。FPGA現(xiàn)在發(fā)展越來越快,片內(nèi)可用資源越來越豐富,不但可以很方便地實(shí)現(xiàn)系統(tǒng)前端的高分辨率高幀率的視頻采集,并且還能對圖像進(jìn)行算法處理。本文提出的Bayer到RGB圖像轉(zhuǎn)換算法簡單,易于在FPGA中實(shí)現(xiàn),移植性好,如果需要將本系統(tǒng)移植至其他FPGA硬件平臺(tái),只要該FPGA的邏輯資源滿足表2中的資源需求,修改相應(yīng)的管腳配置即可。本系統(tǒng)體積小、性能穩(wěn)定、便于攜帶,目前已經(jīng)穩(wěn)定地應(yīng)用在實(shí)驗(yàn)室相關(guān)的研究項(xiàng)目中,具有較強(qiáng)的工程應(yīng)用價(jià)值。

參考文獻(xiàn)

[1] 滕偉, 安博文. 基于 FPGA+ DSP 技術(shù)的 Bayer 格式圖像預(yù)處理[J]. 電子設(shè)計(jì)工程, 2010 (10): 145147.

[2] MA H, LIU S, ZHOU J, et al. The FPGA realization of a realtime Bayer image restoration algorithm with better performance[C].International Symposium on Optoelectronic Technology and Application 2014. International Society for Optics and Photonics, 2014: 93010C93010C4.

[3] TIAN Q, YANG X, ZHANG L, et al. Image reconstruction research on color filter array[J]. Procedia Engineering, 2012, 29(4): 22042208.