世界上每三部手機中就有一部有CEVA基帶DSP,CEVA已占據(jù)DSP IP主要市場份額,超過任何其它DSP IP供應商三倍以上。大家耳熟能詳?shù)娜恰⒂⑻貭枴⒅信d、聯(lián)發(fā)科、新岸線、展訊等公司都是CEVA的客戶。近期CEVA推出新型CEVA-X DSP 架構框架,可以勝任日益復雜的基帶設計,適用于廣泛的應用場景,包括LTE-Advanced 物理層控制、機器通信(MTC)和無線連接技術等。

CEVA市場營銷及企業(yè)發(fā)展副總裁Eran Briman

“特別值得注意的是,CEVA-X4——基于新型CEVA-X DSP架構的首款內(nèi)核,由于具有強大的性能,可以在嵌入式系統(tǒng)中順利運行CDNN(深層神經(jīng)網(wǎng)絡)。CDNN使得嵌入式系統(tǒng)執(zhí)行深層學習任務的速度比基于GPU的領先系統(tǒng)提高3倍,同時消耗的功率減少30倍,所需存儲帶寬減少15倍。” CEVA市場營銷及企業(yè)發(fā)展副總裁Eran Briman表示。

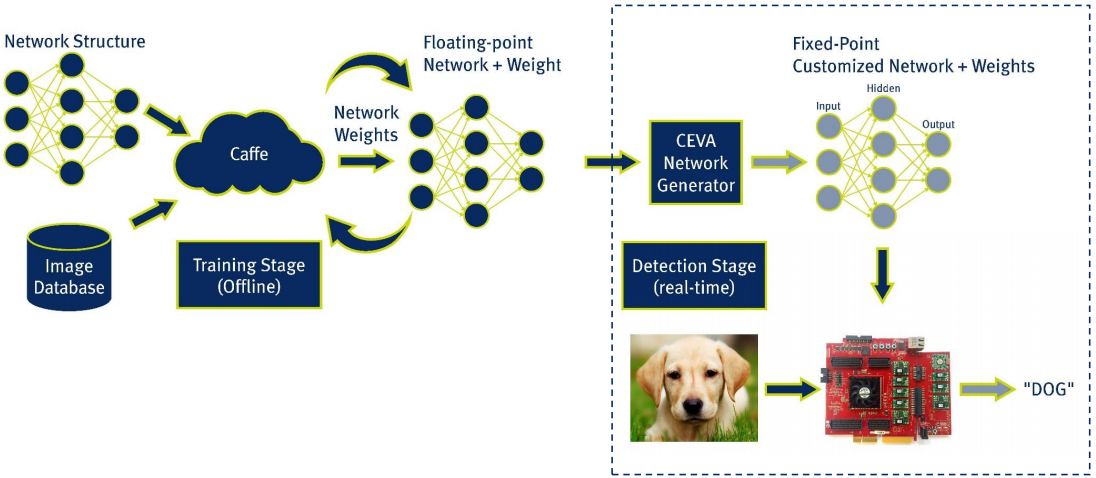

CEVA深層神經(jīng)網(wǎng)絡模型

Eran Briman進一步解釋說:“首先,通用的神經(jīng)網(wǎng)絡結構,在離線狀態(tài)下在大型服務器上做訓練,形成數(shù)據(jù)庫,這大約需要一周或幾周時間,最終輸出一個適用于某類應用專門優(yōu)化的神經(jīng)網(wǎng)絡,這個神經(jīng)網(wǎng)絡具有浮點權重,最終決定運轉(zhuǎn)的過程。接著,將經(jīng)過訓練的浮點數(shù)據(jù)組成的神經(jīng)網(wǎng)絡嵌入終端時需要做處理,因為這些浮點數(shù)之前運行在大型服務器上,非常復雜。讓它運轉(zhuǎn)在低功耗的終端平臺上,有幾個步驟。先通過CEVA開發(fā)的神經(jīng)網(wǎng)絡轉(zhuǎn)換工具,把復雜的浮點數(shù)網(wǎng)絡轉(zhuǎn)化成定點數(shù)表達的神經(jīng)網(wǎng)絡,然后把神經(jīng)網(wǎng)絡加載到XM4的運轉(zhuǎn)平臺上,這樣,這個嵌入式設備就有非常強大的處理能力。”

CEVA-X4架構圖

新型CEVA-X使用可擴展的VLIW/SIMD架構、高達128位SIMD、可變流水線長度和支持定點運算和浮點運算。與前一代CEVA-X相比,新型CEVA-X可以提供2倍以上的DSP性能,而功耗卻低50%。這種架構還包括專用32位零延遲指令集架構(Instruction Set Architecture, ISA)、32位硬件除法和乘法、動態(tài)分支預測和超快上下文轉(zhuǎn)接,以提供現(xiàn)代基帶設計要求的高效控制處理。

CEVA-X4是基于新型CEVA-X DSP架構的首款內(nèi)核,瞄準 2G/3G/4G/5G基帶中multi-RAT多載波P物理層控制處理中最復雜的工作負荷。

最新的CEVA-X4基帶應用處理器將為下一代調(diào)制解調(diào)器提供更加優(yōu)異的性能。

下一代調(diào)制解調(diào)器架構

CEVA-X4將解決新一代調(diào)制解調(diào)器設計中面臨的三個關鍵挑戰(zhàn)。

首先是高效控制處理:對于多載波聚合來說,L1 PHY控制處理顯著增加。例如,并行處理高達5個載波分量和在多個載波上順序處理多個PHY控制任務,需要新一代Rel-13 LTE Advanced Pro調(diào)制解調(diào)器。

其次是強大的DSP處理:需要顯著提高DSP的性能以支持繁重的LTE工作負荷,包括逐個信道測量、校正和解碼,以及其他RAT標準。

最后是先進的系統(tǒng)控制:為了以較低的延時限制方式處理系統(tǒng)中的多個加速器、DSP和共處理器,需要開展復雜的系統(tǒng)調(diào)度和數(shù)據(jù)通信管理。