張良,葛榮駿,張志釗,馬義德

(蘭州大學 電路與系統(tǒng)研究所,甘肅蘭州 730000 )

摘要:介紹了一款以FPGA和NIOS系統(tǒng)為核心設計的智能電子測試儀器。該儀器主要圍繞友晶公司的Altera DE270開發(fā)板進行開發(fā),借助直接數(shù)字頻率合成(DDS)技術與FPGA芯片的可編程、易修改的特性,實現(xiàn)了正弦波、余弦波、三角波、方波、鋸齒波5種基礎波形與AM、FM、2ASK、2PSK 4種調制信號的輸出,并且在LCD液晶屏上實時顯示輸出波形。此外,對于外部反饋信號,系統(tǒng)利用NiosⅡ嵌入式微處理器對信號做進一步的處理,例如波形的幅度變換、頻率測量、電壓測量和幅頻特性分析等。該智能電子測試儀器實現(xiàn)了波形發(fā)生器、數(shù)字示波器、掃頻儀、頻率計、電壓表等多種儀器在功能上的綜合,是智能儀器儀表設計的一次全新的嘗試。

關鍵詞:FPGA;NiosⅡ;智能儀器;波形發(fā)生器

0引言

隨著社會科技水平的不斷發(fā)展,越來越多的企業(yè)、學校和個人都參與到電子產品設計與制作的工作中來,而電子測量儀器是從事電子設計工作時必不可少的工具,因此,對電子測量儀的研究也一直是電子設計領域的熱門話題[14]。

目前,國內外對于電子測量儀器的研究已經非常成熟,以泰克、安捷倫、惠普為首的公司也推出了很多高性能的電子測量儀器。然而,這些儀器雖然性能出眾,但是價格十分昂貴且性能單一,人們從事電子設計時往往需要配備多臺儀器,這無疑極大地增加了電子產品的設計成本。同時,許多公司在設計電子測量儀器時為了追求單一設計指標的高性能,使用大量價格昂貴、體積龐大的模擬電路,造成許多儀器體積龐大且操作不智能,這也增加了從事電子設計的學習負擔。

基于以上背景,本文設計了一款基于FPGA和NIOS系統(tǒng)的智能電子測試儀器。本儀器綜合了波形發(fā)生器、數(shù)字存儲示波器、掃頻儀、頻率計、電壓表等多種儀器的功能,在功能上涵蓋了電路設計所需的輸入信號激勵和輸出信號處理,能夠獨立完成一些復雜實驗,簡化了操作步驟,降低了實驗成本,為智能儀器設計提供了一個全新的思路。

1系統(tǒng)的功能描述

本文以友晶公司設計的DE2開發(fā)平臺為核心,結合FPGA內嵌NiosⅡ微處理器設計了一款智能電子測試儀器。本儀器具備以下功能:

(1)豐富的波形輸出功能

本系統(tǒng)能夠輸出正弦波、余弦波、三角波、方波、鋸齒波5種基礎波形,以及AM(調幅信號)、FM(調頻信號)、2ASK(二進制振幅鍵控信號)、2PSK(二進制相位鍵控信號)4種調制波形。同時系統(tǒng)能夠接收外部調制信號參與調制。

(2)靈活的掃頻輸出功能

借助NiosⅡ微處理器強大的控制能力,本系統(tǒng)能夠在 10 Hz~10 MHz頻率范圍內連續(xù)輸出正弦掃頻信號,借助系統(tǒng)的信息處理能力,能夠對外部被測網絡進行幅頻特性分析。其中掃頻信號的起始頻率、終止頻率、頻率間隔等參數(shù)可預置。

(3)精準的電壓和頻率測量功能

本系統(tǒng)能夠測量1 Hz~10 MHz的頻率范圍內的周期波形的頻率值和電壓值。頻率測量采用全同步等精度測量技術[67],具有較高的測量精度(優(yōu)于10-6)。電壓測量采用數(shù)字峰值檢波技術[8],具有較高的測量穩(wěn)定性,避免了復雜的模擬電路帶來的不穩(wěn)定性和飄移帶來的測量精度不高的影響。

(4)智能的輸入波形輸出波形顯示功能

本系統(tǒng)不僅能夠在LCD液晶屏上實時顯示輸出信號的波形、頻率等信息,借助信號反饋網絡,同時能夠顯示被測信號的波形、頻率、幅度等信息。這樣的設計方便人們在從事電子設計時能夠同時觀察輸入端和輸出端的波形、頻率、幅度等參數(shù)的變化。

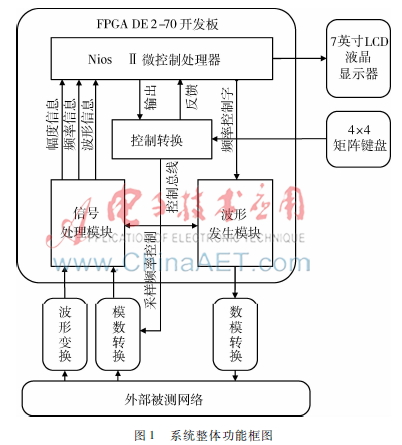

根據(jù)以上對儀器功能的分析,本儀器的系統(tǒng)整體功能框圖如圖1所示。

2系統(tǒng)的結構設計

通過對智能電子測試儀器的具體功能進行分析,將整個系統(tǒng)劃分成3個子系統(tǒng),分別為信號激勵子系統(tǒng)、反饋處理子系統(tǒng)和嵌入式微控制子系統(tǒng)。

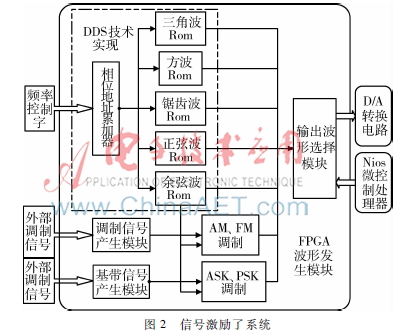

2.1信號激勵子系統(tǒng)

信號激勵子系統(tǒng)的工作流程如圖2所示。首先,子系統(tǒng)接收來自微控制子系統(tǒng)的頻率控制字,借助直接數(shù)字頻率合成技術(DDS技術)[1]在FPGA內部通過Verilog硬件邏輯語言產生正弦波、余弦波、三角波、方波、鋸齒波5種基礎波形[7]。然后以余弦波為載波,以正弦波為調制信號或通過調制信號產生模塊接收外部輸入的調制信號,借助相關算法產生AM和FM兩種調制波形。同時以方波為基帶信號或通過基帶信號產生模塊接收外部輸入的基帶信號,借助相關算法產生ASK和FSK兩種編碼信號。最后通過輸出波形選擇模塊來輸出這些激勵信號[8]。

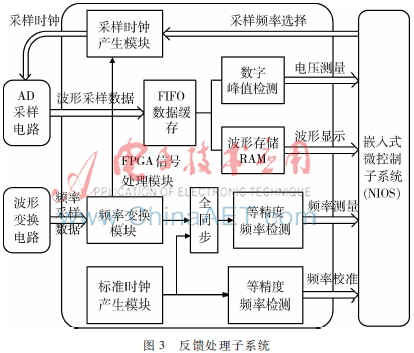

2.2反饋處理子系統(tǒng)

反饋處理子系統(tǒng)的工作流程如圖3所示。在嵌入式微控制子系統(tǒng)的控制下,采樣時鐘模塊首先產生一個預置的采樣時鐘,控制AD采樣電路的采樣速率。然后系統(tǒng)將反饋信號的波形數(shù)據(jù)通過FIFO緩存讀取到FPGA中,再分別對其進行數(shù)字峰值檢波和波形存儲,將處理結果發(fā)送到NiosⅡ微處理器中,實現(xiàn)波形的存儲顯示和電壓測量功能。

波形變換電路首先將具有周期性質的反饋信號變換成同頻率的方波信號并將其輸入到頻率變換模塊,通過控制采樣時鐘產生模塊,使其產生的采樣信號為被測信號的整數(shù)倍,這樣使得不同頻率的信號在液晶上可以顯示相同的周期數(shù)。最后,采用全同步的等精度測頻法對變換后的方波信號進行測頻。此外,采用一個標準時鐘信號進行頻率校準,最終實現(xiàn)頻率測量功能。

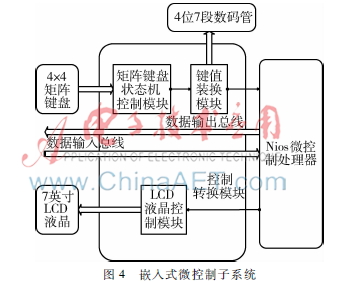

2.3嵌入式微控制子系統(tǒng)

嵌入式微控制子系統(tǒng)的工作流程圖如圖4所示。子系統(tǒng)的主要功能是通過矩陣鍵盤輸入人機交互信息,再通過數(shù)據(jù)輸入和輸出總線控制其他子系統(tǒng),最終在7英寸LCD液晶上進行數(shù)據(jù)顯示。

通過對智能電子測試儀器的系統(tǒng)結構進行分析,明確了整個系統(tǒng)的硬件設計目標。其中信號激勵子系統(tǒng)的波形發(fā)生模塊、反饋處理子系統(tǒng)的信號處理模塊和嵌入式微控制子系統(tǒng)的控制轉換模塊均采用基于Verilog的FPGA硬件邏輯語言實現(xiàn)。最終FPGA硬件設計的RTL視圖如圖5所示。

3系統(tǒng)的軟件設計

嵌入式微控制子系統(tǒng)的核心是來自FPGA內部的NiosⅡ微控制處理器。整個NiosⅡ微控制處理器的軟件工作流程如圖6所示。

首先,NiosⅡ接收來自矩陣鍵盤的輸入控制信息,這些控制信息包括:系統(tǒng)的波形輸出模式、正弦波掃頻的掃描頻率間隔及中斷控制、基礎波形輸出的波形類型和輸出頻率、調制信號的產生方式和調制度、基帶信號的產生方式、AD采樣時鐘頻率和LCD液晶顯示界面的的波形顯示模式等信息。然后,NiosⅡ將這些控制信息通過輸出數(shù)據(jù)總線發(fā)送到各個模塊,使各模塊正常工作。同時,NiosⅡ也通過輸入數(shù)據(jù)總線接收各個模塊的反饋信息,這些信息包括:輸出端的波形信息、采樣時鐘的頻率、輸入信號的波形、電壓最大值和最小值和頻率信息。最終,NiosⅡ微控制處理器將這些信息顯示在外接的7英寸LCD液晶顯示器上。

4系統(tǒng)的測試與分析

本文設計的基于FPGA和Nios系統(tǒng)設計的智能電子測試儀器的實際工作效果如圖7所示。

為了檢測智能電子測試儀器系統(tǒng)波形輸出功能的穩(wěn)定性和測量功能的準確性,借助一臺由泰克公司生產的數(shù)字示波器(型號:Tektronix TDS 2022B)來對其進行測試。

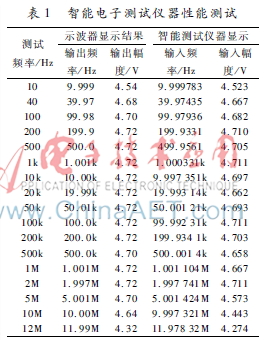

表1是以正弦波為代表,借助示波器檢測本儀器輸出信號的頻率和幅度的穩(wěn)定性與輸入信號頻率和幅度測量的準確性的部分測量結果。

測量結果表明,本儀器采用全同步的等精度頻率測量技術,頻率的有效測量范圍與測量精度相較于傳統(tǒng)儀器有較大的提高。波形輸出的3 dB帶寬為1 Hz~22 MHz,波形在100 Hz~10 MHz

的輸出頻率范圍內,具有良好的幅度穩(wěn)定性。相較于傳統(tǒng)的二極管峰值檢波幅度測量方式,本儀器采用數(shù)字峰值檢波的幅度測量方式,具有較高的測量精度與穩(wěn)定性。

5結論

本系統(tǒng)外圍電路簡單、體積小巧、操作方便,各種功能采用模塊化思路集成在一起,可以根據(jù)用戶需求隨意增減功能模塊,也能根據(jù)不同設計需求改變各功能模塊的技術指標,與傳統(tǒng)電子儀器相比更加智能和靈活。

系統(tǒng)注重多種功能的綜合,減少了實驗所需的儀器數(shù)量,降低了實驗成本,非常適合于沒有足夠成本建立大型實驗室且對于性能指標沒有極高追求的中小型企業(yè)和個人,以及剛剛接觸電子設計的高校學生。圖6NIOS微控制子處理器軟件工作流程圖圖7智能電子測試儀器實驗效果圖

參考文獻

[1] 趙茂泰.智能儀器原理及應用(第3版)[M].北京:電子工業(yè)出版社,2009.

[2] 陳尚松.電子測量與儀器(第2版)[M].北京:電子工業(yè)出版社,2007.

[3] 王媛媛.基于FPGA的數(shù)字秒表設計與實現(xiàn)[J].微型機與應用,2014,33(5):23-26.

[4] 吳征,蘇淑靖.基于FPGA+PWM的多路信號發(fā)生器設計[J].電子技術應用,2014,40(3):38-40,44.

[5] 張志剛.FPGA與SOPC設計教程—DE2實踐[M].西安:西安電子科技大學出版社,2007.

[6] 劉德亮,王竹林,尉廣軍.基于FPGA高精度頻率測量儀的設計[J].河北工業(yè)科技,2010(1): 29-31.

[7] 包本剛.基于FPGA的全同步數(shù)字頻率計的設計[D].長沙:湖南大學,2007.

[8] 石明江,顧亞雄,何道青.基于FPGA的手持式數(shù)字存儲示波器峰值采樣技術[J].儀器儀表,2009(4):6-8.