陳嘯,李廣俠,李志強(qiáng),朱文明

(解放軍理工大學(xué) 通信工程學(xué)院,江蘇 南京210007)

摘要:提出了一種基于FPGA的低截獲概率衛(wèi)星測(cè)控信號(hào)捕獲解決方案。基于AD+FPGA的硬件架構(gòu)完成了帶寬為200 MHz的跳頻和直接序列擴(kuò)頻混合擴(kuò)頻信號(hào)的解跳、解擴(kuò),實(shí)現(xiàn)了基于Xilinx的快速傅里葉變換IP核的擴(kuò)頻碼的快速滑動(dòng)碼相關(guān),以及多跳積分結(jié)果的相干累加,并采用相對(duì)門限法進(jìn)行了捕獲判決。板上試驗(yàn)結(jié)果證明了該方案的捕獲性能,最大捕獲時(shí)間小于4 s,捕獲概率達(dá)到99%,虛警概率小于0.001。該系統(tǒng)已應(yīng)用于北斗二代導(dǎo)航MEO衛(wèi)星測(cè)控鏈路。

關(guān)鍵詞:FPGA;低截獲概率信號(hào);衛(wèi)星測(cè)控;信號(hào)捕獲

0引言

當(dāng)前我國(guó)衛(wèi)星測(cè)控網(wǎng)主要采用微波直接序列擴(kuò)頻測(cè)控體制,具有抗干擾性強(qiáng)、測(cè)距精度較高、一站對(duì)多星測(cè)控等優(yōu)點(diǎn)[1]。一種新的低截獲率混合擴(kuò)頻測(cè)控信號(hào)綜合了跳頻擴(kuò)頻(FHSS)和直接序列擴(kuò)頻(DSSS)的優(yōu)點(diǎn),測(cè)控信號(hào)抗截獲、抗干擾能力得到有效提升,測(cè)控精度也隨信號(hào)帶寬增加而提高[2]。

低截獲概率信號(hào)的合作性接收機(jī)設(shè)計(jì)中,信號(hào)捕獲設(shè)計(jì)最關(guān)鍵,是信號(hào)跟蹤的前提,運(yùn)算量通常占同步運(yùn)算的80%以上。其結(jié)合了DSSS和FHSS的低截獲率擴(kuò)頻信號(hào),由于信號(hào)頻譜比直擴(kuò)信號(hào)進(jìn)一步展寬,因此其自相關(guān)函數(shù)峰更加尖銳,導(dǎo)致捕獲時(shí)的時(shí)延搜索精度要求更高,另一方面,由于采用跳頻體制,多普勒捕獲問(wèn)題中又加入了跳頻頻率跳變,需要設(shè)計(jì)高效的捕獲算法[3]。

FPGA具有設(shè)計(jì)開(kāi)發(fā)周期短、可在線更新、處理性能優(yōu)異等特點(diǎn),適用于解決測(cè)控通信中的捕獲問(wèn)題[46]。針對(duì)低截獲率混合擴(kuò)頻信號(hào)的捕獲問(wèn)題,本文設(shè)計(jì)了一種基于FPGA芯片的跳頻直擴(kuò)混合擴(kuò)頻信號(hào)捕獲系統(tǒng),該系統(tǒng)在完成跳頻解跳、直接序列擴(kuò)頻序列剝離的同時(shí),實(shí)現(xiàn)快速的跳頻多普勒搜索和時(shí)延搜索。對(duì)A/D采樣信號(hào)進(jìn)行FPGA芯片內(nèi)數(shù)字正交下變頻解跳,使用Xilinx的IP核進(jìn)行基于FFTIFFT的并行直擴(kuò)碼解擴(kuò),用分段積分和相位補(bǔ)償?shù)姆椒▽?shí)現(xiàn)了大多普勒范圍搜索,實(shí)現(xiàn)了較大時(shí)間范圍內(nèi)的信號(hào)滑動(dòng)相關(guān),采用相對(duì)門限法進(jìn)行信號(hào)捕獲的判決,獲得了優(yōu)異的檢測(cè)性能。該捕獲系統(tǒng)芯片資源占用率合理,功耗較低,采用多重高可靠性設(shè)計(jì),適用于衛(wèi)星等空間飛行器的測(cè)控系統(tǒng)。

1捕獲模型

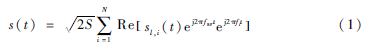

本文研究的低截獲率擴(kuò)頻測(cè)控信號(hào)是相位連續(xù)的快跳頻加直接序列擴(kuò)頻信號(hào),也稱為DS/FH混合擴(kuò)頻信號(hào),采用二進(jìn)制相位調(diào)制方式(BPSK)。跳頻方式為塊跳頻(block hopping),即直擴(kuò)碼相位周期、跳頻相位周期均等于一個(gè)調(diào)制符號(hào)的時(shí)間長(zhǎng)度,跳頻圖案和偽碼相位同周期變化,周期均為N跳,信號(hào)自相關(guān)峰的周期也為N跳,每個(gè)跳頻時(shí)段內(nèi)包含一個(gè)整周期的直接序列擴(kuò)頻碼。由于衛(wèi)星測(cè)控通信屬于高可靠性的低速率通信,一個(gè)跳擴(kuò)頻周期內(nèi)的調(diào)制信息是恒定的,那么信號(hào)可表示為:

其中,S為發(fā)送信號(hào)的平均功率,fi表示跳頻頻點(diǎn), fRF 表示跳頻頻點(diǎn)的射頻基準(zhǔn)頻率,那么實(shí)際的射頻跳頻頻率為fi+fRF。Th為一個(gè)跳頻頻率的持續(xù)時(shí)間,N個(gè)Th組成一個(gè)跳頻周期。Re[·]為取實(shí)部運(yùn)算。sl,i(t) 表示第i個(gè)跳頻頻率內(nèi)的擴(kuò)頻碼,并且定義:

sl,i(t)=PN(t)(2)

其中,PN(t)表示偽碼速率為fc的直接序列擴(kuò)頻碼。為了確保各個(gè)跳頻時(shí)段Th內(nèi)的射頻載波相位起始值相同,跳頻頻率設(shè)計(jì)為:

fi=k/Th, k∈{1,2,...,K},i=1,2,3,...,N(3)

其中,k表示跳頻圖案,fi為1/Th的k次諧波,射頻跳頻帶寬為 BH=K/Th,K為跳頻頻率池的大小,N為所選用的跳頻點(diǎn)的個(gè)數(shù),NK。擴(kuò)頻碼采用周期長(zhǎng)度為M的偽隨機(jī)碼。為了滿足塊跳頻要求,M滿足

MTC=NTh

TC為一個(gè)碼片時(shí)間長(zhǎng)度。這種擴(kuò)頻信號(hào)的處理增益高,能夠?qū)箚我舾蓴_、寬帶干擾等多種樣式的單一和組合干擾。跳頻圖案采用Costas跳頻序列,周期為200跳,PN碼采用周期為1 023的Gold碼,信號(hào)參數(shù)如表1所示。

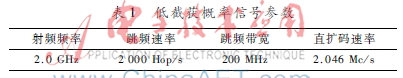

DS/FH混合信號(hào)作為一種擴(kuò)頻信號(hào),信號(hào)頻帶寬,且能量均勻分布在整個(gè)頻帶內(nèi),導(dǎo)致信號(hào)被噪聲所淹沒(méi),具有很強(qiáng)的抗截獲能力,要實(shí)現(xiàn)對(duì)此混合信號(hào)的捕獲,必須對(duì)接收信號(hào)進(jìn)行滑動(dòng)相關(guān)運(yùn)算。如圖1所示,接收機(jī)中頻圖1相干累加原理接收到跳擴(kuò)信號(hào)后,經(jīng)過(guò)滑動(dòng)解擴(kuò)和解跳,將信號(hào)的跳變頻率和直擴(kuò)偽碼從信號(hào)中剝離[8]。當(dāng)滑動(dòng)相關(guān)時(shí)接收信號(hào)和本地信號(hào)相位重合,即信號(hào)恢復(fù)成窄帶信號(hào)后,再對(duì)信號(hào)進(jìn)行累加,濾除帶外噪聲,得到高信噪比的檢測(cè)量或檢測(cè)信號(hào);最后將其送入檢測(cè)器,完成捕獲判決。

對(duì)于式(1)中的相干跳擴(kuò)頻信號(hào),在背景噪聲為白噪聲、信道中無(wú)干擾的條件下,本地跳頻擴(kuò)頻信號(hào)以半個(gè)碼片(或者更細(xì)小)的搜索間隔進(jìn)行滑動(dòng),完成載波/偽碼剝離后經(jīng)長(zhǎng)度為多跳的相干積分后檢測(cè)量的獲得。無(wú)信號(hào)時(shí)檢測(cè)量服從自由度為1的中心χ2分布,有信號(hào)時(shí)檢測(cè)量服從自由度為1的非中心χ2分布。

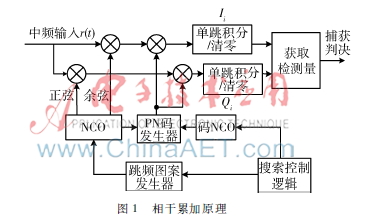

假設(shè)有信號(hào)條件下,單跳積分檢測(cè)量服從A/σ2=10,σ2=1的高斯分布,并取N=10,那么根據(jù)參考文獻(xiàn)[7],3種檢測(cè)量的包絡(luò)在信號(hào)有/無(wú)條件下的概率密度函數(shù)如圖 2所示。信號(hào)捕獲判決準(zhǔn)則采用NeymanPearson準(zhǔn)則,即在給定信號(hào)虛警概率PF前提下,設(shè)定判斷區(qū)域V,使信號(hào)檢測(cè)概率PD最大。從圖2中可看出,選多跳相干累加檢測(cè)量作為捕獲判決量,在相同的虛警概率條件下能獲得較高的檢測(cè)概率。

2系統(tǒng)設(shè)計(jì)方案

2.1硬件環(huán)境

根據(jù)捕獲運(yùn)算要求,本系統(tǒng)用基于FPGA的硬件設(shè)計(jì)方案實(shí)現(xiàn)高速并行捕獲邏輯運(yùn)算。FPGA處理的硬件環(huán)境如圖3所示。

待捕獲的跳擴(kuò)頻信號(hào)通過(guò)兩路ADC,將模擬信號(hào)轉(zhuǎn)換為數(shù)字信號(hào),進(jìn)入FPGA,供FPGA進(jìn)行處理。程序存儲(chǔ)PROM中是本設(shè)計(jì)產(chǎn)生的FPGA配置文件,加電后,F(xiàn)PGA讀取配置文件,在時(shí)鐘驅(qū)動(dòng)下,實(shí)現(xiàn)開(kāi)發(fā)人員設(shè)計(jì)的邏輯功能。

2.2分模塊設(shè)計(jì)

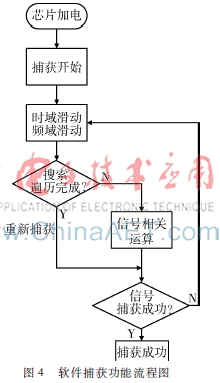

為實(shí)現(xiàn)FPGA內(nèi)部軟件的跳擴(kuò)頻信號(hào)捕獲功能,本系統(tǒng)設(shè)計(jì)的處理流程如圖4所示。

軟件設(shè)計(jì)分為4個(gè)功能模塊,其名稱和功能如下:

(1)捕獲控制模塊:AcqCtrl

負(fù)責(zé)捕獲處理流程控制和捕獲結(jié)果的判斷。

(2)正交解跳模塊:AcqFront

在捕獲控制模塊控制下,完成跳擴(kuò)頻信號(hào)的解跳。

(3)并行解擴(kuò)模塊:CorrFFT

用FFTIFFT并行相關(guān)算法完成直接序列擴(kuò)頻信號(hào)的解擴(kuò),負(fù)責(zé)時(shí)間長(zhǎng)度為1個(gè)跳頻時(shí)段的信號(hào)積分。此模塊負(fù)責(zé)完成分辨率為半個(gè)直接序列擴(kuò)頻碼碼片的時(shí)延搜索。

(4)多跳累積模塊:PhasCmp

負(fù)責(zé)將N個(gè)跳頻時(shí)段內(nèi)的積分結(jié)果累加起來(lái),得到半碼片以內(nèi)的時(shí)域搜索的捕獲結(jié)果,同時(shí)實(shí)現(xiàn)(-50 kHz,50 kHz)范圍的多普勒搜索,將累加結(jié)果送給捕獲控制模塊進(jìn)行判斷。綜合以上4個(gè)模塊,形成了本軟件的模塊架構(gòu),如圖5所示。虛線表示控制信號(hào),實(shí)線表示信號(hào)流。

2.2.1正交解跳模塊

為節(jié)省硬件資源,本文算法對(duì)應(yīng)的捕獲結(jié)構(gòu)采用了雙下變頻器交替變頻解跳和基于FFT的快速碼相關(guān)解擴(kuò)的方案。圖6表示解跳結(jié)構(gòu),跳頻帶寬為200 MHz,采樣頻率為280 MHz正交I、Q采樣,用不同圖案表示不同跳頻頻圖6AcqFront模塊工作示意率,τ表示收發(fā)時(shí)間差,PN1表示接收第1跳內(nèi)的PN碼,本地下變頻器相位從0開(kāi)始,到4 kπ結(jié)束,跳頻頻率重合時(shí),解擴(kuò)A、B輸出正確的PN碼。2個(gè)下變頻器A、B交替解跳的結(jié)構(gòu)加長(zhǎng)了單個(gè)跳頻諧波解跳的時(shí)長(zhǎng),獲得了2Th時(shí)長(zhǎng)的解跳結(jié)果,交替解跳結(jié)構(gòu)能夠保留2Th時(shí)長(zhǎng)的解擴(kuò)輸出,從而保證碼相關(guān)積分時(shí)長(zhǎng)為Th時(shí),碼滑動(dòng)相關(guān)的搜索范圍能夠達(dá)到τmax=Th。

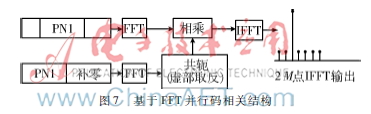

2.2.2基于FFT的并行解擴(kuò)模塊

解跳完成后,在芯片內(nèi)對(duì)信號(hào)進(jìn)行下抽處理,降低后端信號(hào)處理速率需求。將280 MHz采樣信號(hào)下抽40倍到7 MHz后進(jìn)行處理。圖 7表示解擴(kuò)結(jié)構(gòu),解跳結(jié)果以流水線順序送入FFT核,每一幀點(diǎn)數(shù)為4 096點(diǎn),同時(shí)本地?cái)U(kuò)頻碼也進(jìn)行FFT。經(jīng)處理后,每一跳時(shí)間內(nèi)對(duì)應(yīng)輸出M=2 046個(gè)解擴(kuò)結(jié)果,存入RAM中。

2.2.3多跳累積模塊

將解擴(kuò)模塊輸出的N跳內(nèi)M個(gè)碼相位上的共M×N個(gè)解擴(kuò)結(jié)果從RAM中讀出之后,按0.1碼片的步進(jìn)進(jìn)行時(shí)間搜索和相干累積。圖8所示為相干累積結(jié)構(gòu)。

將2NM個(gè)數(shù)據(jù)點(diǎn)Pi(m)按跳頻點(diǎn)i分為2M組,逐組對(duì)i=1,2,…,N個(gè)數(shù)據(jù)進(jìn)行相干累加,相干累加結(jié)果取平方后經(jīng)過(guò)一個(gè)比較器,保留最大相干累積能量及其對(duì)應(yīng)的時(shí)間頻率搜索值。當(dāng)?shù)玫阶畲笙喔衫鄯e能量Pmax及其對(duì)應(yīng)的時(shí)間頻率信息后,再取該時(shí)間點(diǎn)附近的L個(gè)點(diǎn)計(jì)算出L個(gè)積分結(jié)果,表示碼相位范圍為(-L/2,L/2)個(gè)碼片。若Pmax>2·E[P(l)],則判斷捕獲成功,反之則判定為捕獲失敗。

2.3實(shí)現(xiàn)情況

為實(shí)現(xiàn)低截獲概率信號(hào)捕獲系統(tǒng),選用了Xilinx公司的Kintex7FFG900芯片,A/D芯片采用2片14位輸入的AD9726芯片。FPGA外部參考時(shí)鐘為100 MHz,內(nèi)部工作時(shí)鐘為280 MHz。芯片內(nèi)部Slice使用率為56%,滿足航天設(shè)備芯片降額使用的標(biāo)準(zhǔn),芯片功耗估計(jì)值為4.3 W,包括A/D轉(zhuǎn)換等器件的基帶電路總功耗為7 W。實(shí)現(xiàn)了第2節(jié)中低截獲概率跳擴(kuò)頻信號(hào)的捕獲,時(shí)間捕獲范圍為(-50 ms,50 ms),多普勒頻率捕獲范圍為(-50 kHz, 50 kHz),多普勒變化率范圍為(-12 kHz/s, 12 kHz/s)。最大捕獲時(shí)間不超過(guò)4 s,捕獲概率大于99%,虛警概率小于0.001。

3試驗(yàn)結(jié)果

對(duì)本文的捕獲系統(tǒng)進(jìn)行了基帶電路板仿真驗(yàn)證,統(tǒng)計(jì)了不同的時(shí)間搜索精度下,信號(hào)源發(fā)射信噪比與檢測(cè)概率的關(guān)系如圖9所示。試驗(yàn)環(huán)境包括安捷倫E4438C信號(hào)源2臺(tái)、XX型衛(wèi)星應(yīng)答機(jī)射頻通道、基于Xilinx Kintex7的基帶板一副,以及電源、連接線若干。信號(hào)源負(fù)責(zé)信號(hào)上變頻和射頻加噪,基帶板完成發(fā)送和捕獲中頻跳擴(kuò)測(cè)控信號(hào)的功能。

電路板驗(yàn)證時(shí)可通過(guò)FPGA預(yù)留調(diào)試口調(diào)整時(shí)間搜索精度,可選精度有0.01/0.1/0.25/0.5 chip。由于碼相位搜索間隔以及FFT運(yùn)算的有限字長(zhǎng)效應(yīng)[9],導(dǎo)致板上仿真檢測(cè)性能略有下降,距離理論值約有3 dB距離;當(dāng)選取Δτ=0.1 chip,本文算法在單符號(hào)信噪比為17 dB時(shí)可達(dá)到99%的捕獲概率;當(dāng)碼相位搜索間隔從0.25 chip擴(kuò)大到0.5 chip時(shí),檢測(cè)性能急劇下降。

4結(jié)論

為解決低截獲概率混合擴(kuò)頻的快速捕獲問(wèn)題,選擇了以FPGA作為處理核心的基帶解決方案[10],設(shè)計(jì)實(shí)現(xiàn)了基于FFT分段碼相關(guān)和多跳相干累積的捕獲系統(tǒng)并進(jìn)行了板上試驗(yàn)。本算法捕獲精度達(dá)到0.01 chip,捕獲到的DS/FH信號(hào)可直接送入載波環(huán)路進(jìn)行載波跟蹤,能減輕跟蹤環(huán)路負(fù)擔(dān)。實(shí)際應(yīng)用中,可根據(jù)捕獲精度需求選擇時(shí)間捕獲分辨率,大小從0.01 chip到0.5 chip。經(jīng)在軌測(cè)試后,本系統(tǒng)已成功運(yùn)用于北斗二代導(dǎo)航衛(wèi)星的某新型衛(wèi)星測(cè)控系統(tǒng)中。

參考文獻(xiàn)

[1] 沈榮駿,趙軍.我國(guó)航天測(cè)控技術(shù)的發(fā)展趨勢(shì)與策略[J].宇航學(xué)報(bào),2001,22(3):15

[2] 楊文革,王金寶,孟生云,等.DS/FH混合擴(kuò)頻信號(hào)捕獲方法綜述[J].測(cè)控技術(shù),2009,28(z1):1620.

[3] KAPLAN E D, HEGARTY C J, Understanding GPS, principles and applications(Second Edition)[M]. Norwood, MA: Artech House, Inc. ch. 5.4,173200.

[4] 王水魚(yú),馮曉靖.一種新型deltasigma小數(shù)分頻器的FPGA實(shí)現(xiàn)[J].微型機(jī)與應(yīng)用,2013,32(5):2527,31.

[5] 彭奇,習(xí)友寶.基于FPGA和改進(jìn)CORDIC算法的NCO設(shè)計(jì)與實(shí)現(xiàn)[J].微型機(jī)與應(yīng)用,2013,32(5):6062.

[6] 宋萬(wàn)均,張安堂.雙基地雷達(dá)目標(biāo)速度計(jì)算的FPGA實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2014,40(1):4749,52.

[7] MARCUM F I. A statistical theory of target detection by pulsed radar, rand research memo[R]. RM754, December 1947, with Appendix, RM753, July 1948.

[8] 潘點(diǎn)飛,程乃平,郝建華,等.DS/FH測(cè)控系統(tǒng)抗干擾性能分析與測(cè)試[J].空間科學(xué)學(xué)報(bào), 2013, 33(5): 540547.

[9] 黃磊,張其善,寇艷紅,等.GPS信號(hào)FFT捕獲算法的有限字長(zhǎng)效應(yīng)分析[J]. 宇航學(xué)報(bào), 2006, 27(5): 10291033.

[10] 陳巍,王國(guó)富,張法全,等.基于FPGA同步時(shí)鐘測(cè)量系統(tǒng)的研究及實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2014,40(12):8688,91.