俞凌筠,韓佳鑫,孫立達

(上海衛(wèi)星工程研究所, 上海 200240)

摘要:對高速基帶傳輸中產(chǎn)生噪聲" title="同步開關(guān)噪聲" target="_blank">同步開關(guān)噪聲的原因進行了深入分析。通過理論分析和試驗數(shù)據(jù),提出了抗同步開關(guān)噪聲的方法。對于今后在高速基帶設(shè)計中避免同步開關(guān)噪聲有一定的指導意義。

關(guān)鍵詞: 同步開關(guān)噪聲;基帶傳輸

0引言

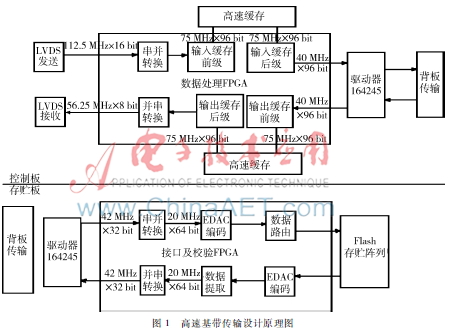

圖1高速基帶傳輸設(shè)計原理圖隨著衛(wèi)星基帶設(shè)備電路板上大量使用高集成度的高速數(shù)字芯片,同步開關(guān)噪聲(Simultaneous Switching Noise,SSN)問題成為制約高速基帶傳輸設(shè)計的一個瓶頸。同步開關(guān)噪聲是指當器件上多個邏輯電路或I/O管腳同時處于開關(guān)狀態(tài)時,產(chǎn)生瞬間變化的電流,在經(jīng)過回流路徑上存在的電感時,形成交流壓降,從而引起噪聲。如果引起地平面的波動,就會造成芯片地與系統(tǒng)地不一致,這種現(xiàn)象稱為地彈[12]。

同步開關(guān)噪聲的危害是非常大的,會增加電源噪聲,影響信號的質(zhì)量和時序,產(chǎn)生毛刺,從而導致數(shù)字電路誤采樣[3]。另外,同步開關(guān)噪聲引起的問題一般隱藏得很深,只有在器件多個邏輯單元同時開關(guān)時才會發(fā)生,用正常的業(yè)務(wù)測試方法很難發(fā)現(xiàn),容易漏測[4]。針對高速基帶傳輸中的同步開關(guān)噪聲問題,本文提出了優(yōu)化設(shè)計方案。

1高速基帶傳輸設(shè)計

某衛(wèi)星型號高速基帶傳輸設(shè)計如下:數(shù)據(jù)處理FPGA通過LVDS接口接收外部112.5 Mb/s×16 bit高速數(shù)據(jù)流,對其進行串并轉(zhuǎn)換后緩存,利用驅(qū)動器164245建立96 bit并行數(shù)據(jù)傳輸,通過背板傳輸至接口及校驗FPGA進行后續(xù)數(shù)據(jù)處理,其中背板上單位傳輸速率為40 Mb/s。其設(shè)計原理圖如圖1所示。

在上述傳輸條件下,當傳輸隨機數(shù)據(jù)序列時,傳輸結(jié)果無誤碼;而在傳輸含有長0或長1的數(shù)據(jù)序列時,產(chǎn)生了大量的誤碼。通過對背板傳輸信號進行監(jiān)視,發(fā)現(xiàn)在傳輸長0或長1數(shù)據(jù)時,產(chǎn)生了同步開關(guān)噪聲。本該傳輸0的某些時間點出現(xiàn)了毛刺,該毛刺信號接近接收器的門限,從而導致誤判。

2同步開關(guān)噪聲產(chǎn)生原因分析

2.1開關(guān)驅(qū)動器數(shù)量

開關(guān)驅(qū)動器的數(shù)量為在并行傳輸中邏輯0向邏輯1跳變的位數(shù)數(shù)量。開關(guān)驅(qū)動器的數(shù)量由并行傳輸?shù)目偽粩?shù)和數(shù)據(jù)源的類型兩方面決定。近年來由于衛(wèi)星載荷高速傳輸?shù)男枨螅沟帽嘲寤鶐鬏斨袀鬏斘粩?shù)由32 bit增加到96 bit,且載荷數(shù)據(jù)隨機性不強,常常含有長0長1的數(shù)據(jù)。因此,并行傳輸?shù)奈粩?shù)增加和傳輸含有長0長1的數(shù)據(jù)序列增加了開關(guān)驅(qū)動器的數(shù)量,當開關(guān)驅(qū)動器增加到一定數(shù)量時,就會引發(fā)同步開關(guān)噪聲,產(chǎn)生毛刺,造成誤判,如圖2所示。

2.2回路電感

電路板級的電源必須通過感性連接器為元器件提供各種瞬時的電流需求。在電路板級任何流經(jīng)連接器的電流必須有對應(yīng)的供電電源,并通過電源引腳和接地引腳返回。由于電流在連接器上必須通過接地引腳返回電源,當接地引腳與目標信號引腳之間的距離增加時,總的回路電感將增大。如果回路不連續(xù),且若干個輸出對應(yīng)的返回電流流經(jīng)一塊很小的區(qū)域,則同步開關(guān)噪聲會急劇增大。

圖3背板引腳分配示意圖根據(jù)背板的引腳分配圖(如圖3所示),通過對引腳A31和A24上的眼圖信號進行分析(A31引腳離電源地最近,A24引腳離電源地最遠),發(fā)現(xiàn)離電源地近的引腳A31的信號眼圖質(zhì)量比離電源地遠的引腳A24的好,如圖4、圖5所示。因此,引腳離電源地越遠,回路電感越大,同步開關(guān)噪聲越大;反之,同步開關(guān)噪聲越小。

2.3開關(guān)時間

開關(guān)同步時間為驅(qū)動器上由0跳變至1或由1跳變至0的時間。板級上的走線本身有著一定的寄生電容,通過串接電阻即可實現(xiàn)RC充放電電路,調(diào)節(jié)電阻的阻值即可改變充放電時間。通過對上節(jié)同步開關(guān)噪聲最嚴重的引腳24進行不同阻值的電阻(33 Ω、51 Ω)串接后再對其眼圖進行監(jiān)測,發(fā)現(xiàn)串接51 Ω電阻后的信號眼圖質(zhì)量比串接33 Ω的好,如圖6、圖7所示。因此,串聯(lián)電阻的阻

圖7引腳24串接51Ω電阻眼圖值越小(或不串接電阻),開關(guān)時間越短,同步開關(guān)噪聲越大;反之,同步開關(guān)噪聲越小。

3高速基帶傳輸抗同步開關(guān)噪聲設(shè)計

針對多位并行高速傳輸容易造成同步開關(guān)噪聲的缺點,抗同步開關(guān)噪聲設(shè)計的方案包括對數(shù)據(jù)源傳輸前后進行加解擾處理、增加接地引腳數(shù)量并合理分配其位置、在背板傳輸線上串聯(lián)電阻三個方面。

由于高速基帶傳輸無法降低并行傳輸位數(shù),因此只能通過增加傳輸數(shù)據(jù)的隨機性來減小開關(guān)驅(qū)動器的數(shù)量,從而有效地抑制同步開關(guān)噪聲。通過在數(shù)據(jù)源傳輸前對數(shù)據(jù)源進行加擾,傳輸后進行解擾的方法增加傳輸過程中數(shù)據(jù)源的隨機性,從而有效減小傳輸過程中同步開關(guān)驅(qū)動器的數(shù)量。

在PCB板設(shè)計時增加接地引腳數(shù)量,合理分配接地引腳的位置,保證每個傳輸節(jié)點附近都分布接地引腳,使得板級電流回路暢通,從而減少回路電感,減小同步開關(guān)噪聲。

在背板每位傳輸線中串接電阻,增加驅(qū)動開關(guān)時間。考慮串聯(lián)電阻與輸出阻抗的匹配性,選擇串接51 Ω的電阻。

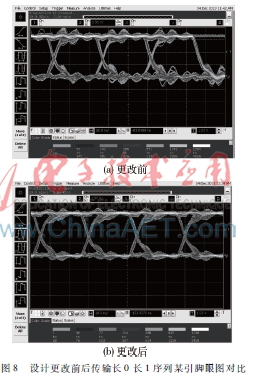

按照上述優(yōu)化方案,對某型號衛(wèi)星高速基帶傳輸設(shè)計進行優(yōu)化更改,對優(yōu)化后的設(shè)計采用長0長1數(shù)據(jù)樣本進行測試,更改前后的某引腳眼圖如圖8所示,同步開關(guān)噪圖8設(shè)計更改前后傳輸長0長1序列某引腳眼圖對比聲影響改善顯著(毛刺現(xiàn)象減少)。誤碼率測試中,測試樣本數(shù)據(jù)量大于1 GB,測試結(jié)果顯示測試誤碼率為0。

4結(jié)束語

本文結(jié)合衛(wèi)星高速基帶傳輸設(shè)計的工程實際,對同步開關(guān)噪聲產(chǎn)生的原因進行了分析,并進行了設(shè)計改進。通過對多種數(shù)據(jù)樣本的測試,驗證了改進設(shè)計的有效性,對今后高速基帶傳輸?shù)脑O(shè)計具有一定的指導意義。

參考文獻

[1] 張穎.高速PCB電路中同步開關(guān)噪聲抑制方法研究[D].西安:西安電子科技大學,2012.

[2] 宋萬均,張安堂.雙基地雷達目標速度計算的FPGA實現(xiàn)[J].電子技術(shù)應(yīng)用,2014,40(1):4749,52.

[3] 張從力,史記征.擴頻技術(shù)在礦井透地通信系統(tǒng)中的應(yīng)用與仿真[J].微型機與應(yīng)用, 2013,32(1): 5153,56.

[4] 陸增援. FPGA上同步開關(guān)噪聲的分析[EB/OL].(20090403)[20160115].電子工程專