文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2016.09.030

中文引用格式: 張艷輝,郭洺宇,何賓. Vivado HLS嵌入式實(shí)時(shí)圖像處理系統(tǒng)的構(gòu)建與實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2016,42(9):115-117,121.

英文引用格式: Zhang Yanhui,Guo Mingyu,He Bin. Construction and implementation of Vivado HLS embedded real-time image processing system[J].Application of Electronic Technique,2016,42(9):115-117,121.

0 引言

近年來(lái),由于成像技術(shù)的不斷進(jìn)步以及圖像應(yīng)用領(lǐng)域的拓寬,數(shù)字圖像包含的數(shù)據(jù)量與日俱增,圖像處理算法也越來(lái)越復(fù)雜[1]。目前應(yīng)用普遍的數(shù)字信號(hào)處理器(Digital Signal Processor,DSP)和圖形處理器(Graphics Processing Unit,GPU)技術(shù)雖然在實(shí)現(xiàn)圖像處理上有著廉價(jià)、易于編程的優(yōu)點(diǎn),但是在性能、功耗、實(shí)時(shí)性方面,它們與FPGA相比仍有巨大的差距,難以滿足嵌入式圖像領(lǐng)域不斷增長(zhǎng)的靈活性、高性能、低功耗的要求。大量研究表明,采用FPGA實(shí)現(xiàn)圖像處理能夠獲得較高的計(jì)算性能。因此,從計(jì)算性能、實(shí)時(shí)性的角度考慮,F(xiàn)PGA是嵌入式圖像處理應(yīng)用的理想選擇方案[2]。

Xilinx公司的ZYNQ-7000系列產(chǎn)品集成了最新工藝的ARM Cortex-A9雙核處理器與高性能的FPGA。作為新一代的可編程片上系統(tǒng),ZYNQ-7000 SoC非常適合于計(jì)算密集、功能豐富的嵌入式應(yīng)用設(shè)計(jì)。Xilinx公司的Vivado HLS工具將C語(yǔ)言、C++以及系統(tǒng)C語(yǔ)言引入到可編程邏輯設(shè)計(jì)中,而無(wú)須通過(guò)傳統(tǒng)的硬件描述語(yǔ)言編寫(xiě)復(fù)雜的程序,大大地加速了IP創(chuàng)建,滿足了處理算法的靈活性[3]。設(shè)計(jì)利用Vivado HLS工具實(shí)現(xiàn)了可變參數(shù)的拉普拉斯算子圖像濾波算法,將生成的IP加入到ZYNQ-7000的可編程邏輯部分,用于處理OV7670攝像頭采集到的圖像數(shù)據(jù)。移植Ubuntu Linux桌面系統(tǒng)到ZYNQ-7000雙核處理器中,利用Qt工具編寫(xiě)上位機(jī)人機(jī)交互控制界面與下位機(jī)顯示程序,實(shí)現(xiàn)了嵌入式Linux可視化實(shí)時(shí)圖像處理系統(tǒng)。

1 系統(tǒng)總體結(jié)構(gòu)

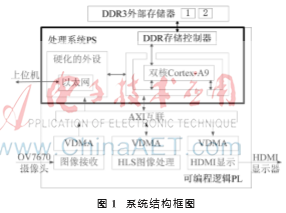

ZYNQ-7000嵌入式數(shù)字圖像處理系統(tǒng)結(jié)構(gòu)框圖如圖1所示,系統(tǒng)主要由OV7670攝像頭、ZYNQ-7000 SoC、數(shù)據(jù)存儲(chǔ)單元DDR3、HDMI顯示器以及上位機(jī)等組成。ZYNQ-7000 SoC作為整個(gè)實(shí)時(shí)處理系統(tǒng)的核心,包括處理系統(tǒng)(Processing System,PS)和可編程邏輯(Programmable Logic,PL)兩部分,其中PS部分主要包含了雙ARM Cortex-A9核,PL部分包含了傳統(tǒng)意義的DSP資源和FPGA邏輯單元。

1.1 PL部分實(shí)現(xiàn)的功能

可編程邏輯PL部分實(shí)現(xiàn)的主要功能如下:

(1)從OV7670攝像頭中獲取圖像數(shù)據(jù),并通過(guò)視頻存儲(chǔ)器直接訪問(wèn)(Video Direct Memory Access,VDMA)傳輸至DDR3存儲(chǔ)芯片中存儲(chǔ);

(2)將DDR3中存儲(chǔ)的圖像數(shù)據(jù)通過(guò)VDMA傳輸?shù)娇勺儏?shù)的拉普拉斯濾波算法IP模塊進(jìn)行圖像處理,并把處理生成的圖像數(shù)據(jù)通過(guò)VDMA重新傳輸?shù)紻DR3;

(3)PL中的顯示模塊配合VDMA構(gòu)成嵌入式Linux的硬件顯示單元。

圖像采集采用OV7670攝像頭,OV7670圖像傳感器體積小、工作電壓低,提供單片VGA攝像頭和影像處理器的所有功能。通過(guò)SCCB 總線控制,可以輸出整幀、子采樣、取窗口等方式的各種分辨率的8位影像數(shù)據(jù)。設(shè)計(jì)選用RGB565、VGA640×480作為輸出格式,將相應(yīng)的寄存器值通過(guò)SCCB控制模塊寫(xiě)入到寄存器中,并把采集的數(shù)據(jù)通過(guò)AXI4 Stream接口協(xié)議寫(xiě)入到DDR3中。在該設(shè)計(jì)中,通過(guò)硬件描述語(yǔ)言實(shí)現(xiàn)SCCB圖像控制與圖像接收模塊的設(shè)計(jì)。

1.2 PS部分實(shí)現(xiàn)的功能

處理系統(tǒng)PS部分實(shí)現(xiàn)的主要功能如下:

(1)運(yùn)行Ubuntu桌面系統(tǒng),為上層應(yīng)用提供操作系統(tǒng)支持;

(2)調(diào)用編寫(xiě)的VDMA、HDMI圖像顯示驅(qū)動(dòng)實(shí)現(xiàn)與PL數(shù)據(jù)交互、桌面系統(tǒng)顯示的功能;

(3)實(shí)現(xiàn)Qt編寫(xiě)的上層應(yīng)用程序及網(wǎng)絡(luò)編程等。

如圖1所示,VDMA提供了PL與DDR3存儲(chǔ)器進(jìn)行高速數(shù)據(jù)傳輸?shù)臋C(jī)制。VDMA具有兩個(gè)數(shù)據(jù)端口:MM2S和S2MM。MM2S和S2MM的最大數(shù)據(jù)位寬均為64 bit,緩存區(qū)深度為512 B[4]。其中S2MM端口實(shí)現(xiàn)圖像數(shù)據(jù)從PL向DDR3存儲(chǔ)器傳輸,MM2S端口實(shí)現(xiàn)圖像數(shù)據(jù)從DDR3存儲(chǔ)器向PL傳輸。ARM處理器可以通過(guò)通用接口AXI_GP對(duì)VDMA進(jìn)行控制。

2 拉普拉斯算子濾波算法的實(shí)現(xiàn)

2.1 拉普拉斯算子濾波算法

拉普拉斯算子是圖像處理技術(shù)中常見(jiàn)的一種增強(qiáng)算子,因?yàn)榫哂行D(zhuǎn)不變性、實(shí)現(xiàn)簡(jiǎn)單等特點(diǎn),被廣泛地應(yīng)用于圖像銳化和高頻增強(qiáng)等算法中。圖像信號(hào)中,高頻分量一般對(duì)應(yīng)于圖像的邊緣輪廓,采用拉普拉斯算子的圖像濾波算法能夠?qū)崿F(xiàn)圖像銳化、增強(qiáng)圖像輪廓清晰度的效果。拉普拉斯算子是最簡(jiǎn)單的各向同性微分算子,具有旋轉(zhuǎn)不變性。一個(gè)二維圖像函數(shù)的拉普拉斯變換是各向同性的二階導(dǎo)數(shù),定義為:

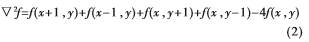

該方程的離散形式為:

拉普拉斯算子可以表示成模板的形式,如圖2(a)所示,圖2(b)表示其擴(kuò)展模板,圖2(c)和圖2(d)則分別表示其他兩種拉普拉斯的實(shí)現(xiàn)模板。

2.2 Vivado HLS實(shí)現(xiàn)算法編寫(xiě)

Vivado HLS利用C語(yǔ)言、C++語(yǔ)言以及系統(tǒng)C語(yǔ)言提供的高級(jí)結(jié)構(gòu)來(lái)提高抽象層次,提供數(shù)據(jù)原語(yǔ)方便使用基礎(chǔ)硬件構(gòu)建IP模塊。與使用RTL相比,Vivado HLS代碼更加緊湊,可讀性和可維護(hù)性更加優(yōu)良,可以更輕松地實(shí)現(xiàn)各種接口協(xié)議,從簡(jiǎn)單的FIFO接口到完整的AXI4 Stream,滿足不同模塊間的數(shù)據(jù)通信。

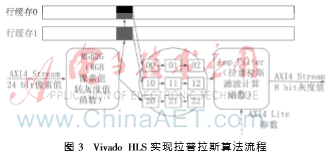

Vivado HLS實(shí)現(xiàn)拉普拉斯算法流程如圖3所示。數(shù)據(jù)處理按照?qǐng)D中箭頭依次進(jìn)行,數(shù)據(jù)在單個(gè)單元中并行運(yùn)算或在不同單元間并行移動(dòng)。每個(gè)時(shí)鐘周期AXI4 Stream接口將24 bit的一個(gè)像素?cái)?shù)據(jù)送入算法模塊中,先經(jīng)過(guò)灰度處理,然后存入2×640的行緩存中,行緩存和新的數(shù)據(jù)構(gòu)成3×3的窗口數(shù)據(jù),窗口的9個(gè)數(shù)據(jù)和AXI_GP接口傳輸進(jìn)來(lái)的拉普拉斯算子參數(shù)進(jìn)行運(yùn)算得到一個(gè)新的8 bit像素?cái)?shù)據(jù)送回到DDR3中。

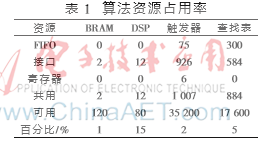

編寫(xiě)的算法在XC7Z010器件上的資源占用率如表1所示,可以看出,只用了PL很少的資源便實(shí)現(xiàn)了圖像濾波算法。

2.3 Qt實(shí)現(xiàn)參數(shù)控制程序

良好的人機(jī)交互功能是嵌入式系統(tǒng)重要的一部分[5]。設(shè)計(jì)采用Qt Creator開(kāi)發(fā)工具在PC上實(shí)現(xiàn)了控制端應(yīng)用程序,如圖4所示。PC通過(guò)以太網(wǎng)與下位機(jī)進(jìn)行連接,在控制端輸入不同的拉普拉斯算子,系統(tǒng)會(huì)產(chǎn)生不同的濾波效果,并將濾波后的圖像顯示在下位機(jī)的HDMI顯示器上。

3 設(shè)計(jì)仿真與系統(tǒng)測(cè)試

3.1 Vivado HLS仿真

Vivado HLS除了將高效的編程代碼轉(zhuǎn)換為IP以外,還提供了另一項(xiàng)重要功能:C語(yǔ)言仿真和C/RTL協(xié)同仿真。C語(yǔ)言仿真中C/C++的編譯和執(zhí)行與常見(jiàn)的C/C++程序相同,具有良好的可讀性和高效性。C/RTL協(xié)同仿真會(huì)根據(jù)C/C++測(cè)試平臺(tái)自動(dòng)生成RTL測(cè)試平臺(tái),設(shè)置并執(zhí)行RTL仿真,檢查實(shí)現(xiàn)方案的正確性。C語(yǔ)言仿真測(cè)試代碼如下:

IplImage* src=cvLoadImage("lena.jpg");//加載測(cè)試圖片

AXI_STREAM src_axi, dst_axi;//定義流數(shù)據(jù)類型變量

IplImage2AXIvideo(src, src_axi);

//圖片轉(zhuǎn)換為流數(shù)據(jù)類型

Laplasian_fil(&lap00,&lap01,&lap02,&lap10,&lap11,

&lap12,&lap20,&lap21,&lap22,src_axi, dst_axi);

//濾波算法主函數(shù)

AXIvideo2IplImage(dst_axi, dst);

//流數(shù)據(jù)類型轉(zhuǎn)換為圖片

cvSaveImage("lena_result.jpg", dst);//保存圖片

測(cè)試程序首先將本地用于測(cè)試的圖片轉(zhuǎn)換為AXI4 Stream接口協(xié)議數(shù)據(jù),并設(shè)置拉普拉斯算子的值,然后將圖片數(shù)據(jù)和拉普拉斯算子以參數(shù)的形式送入到圖像濾波算法中,濾波后的圖片會(huì)以jpg的形式存入本地。測(cè)試原圖片及生成圖片如圖5所示。

3.2 系統(tǒng)測(cè)試

測(cè)試系統(tǒng)采用Xilinx公司提供的ZyBo開(kāi)發(fā)板,該開(kāi)發(fā)板搭載了XC7Z010主芯片,擴(kuò)展外設(shè)通過(guò)PMOD接口與OV7670攝像頭進(jìn)行連接,PC通過(guò)板載以太網(wǎng)接口和串行接口與ZyBo通信,HDMI顯示運(yùn)行的Ubuntu桌面系統(tǒng)。

控制端輸入圖2中不同的拉普拉斯算子得到的處理結(jié)果如圖6所示,結(jié)果完全滿足每秒30幀、RGB640×480格式圖像實(shí)時(shí)濾波的要求。

4 結(jié)論

基于ZYNQ-7000異構(gòu)架構(gòu)的圖像處理系統(tǒng)不但可以實(shí)現(xiàn)嵌入式操作系統(tǒng)相關(guān)的任務(wù),如圖形界面、用戶輸入、網(wǎng)絡(luò)、DDR3控制等,還可以提供高性能實(shí)時(shí)圖像處理的功能[6]。采用Xilinx最新的Vivado HLS工具進(jìn)行FPGA高層次設(shè)計(jì)對(duì)圖像算法進(jìn)行加速,能夠有效提高設(shè)計(jì)效率,并且能夠快速生成工業(yè)標(biāo)準(zhǔn)的IP核,有利于進(jìn)一步實(shí)現(xiàn)系統(tǒng)集成。設(shè)計(jì)的實(shí)驗(yàn)和驗(yàn)證結(jié)果表明了基于ZYNQ-7000異構(gòu)架構(gòu)和Vivado HLS工具的實(shí)時(shí)圖像處理系統(tǒng)易于移植,便于針對(duì)特定應(yīng)用定制,為未來(lái)的高性能圖像處理提供了較高的工程應(yīng)用與參考價(jià)值。

參考文獻(xiàn)

[1] 何賓.Xilinx FPGA設(shè)計(jì)權(quán)威指南[M].北京:清華大學(xué)出版社,2014.

[2] 陸佳華,江舟.嵌入式系統(tǒng)軟硬件協(xié)同設(shè)計(jì)實(shí)戰(zhàn)指南[M].北京:機(jī)械工業(yè)出版社,2013.

[3] 陸啟帥,陸彥婷,王地.Xilinx Zynq SoC與嵌入式Linux設(shè)計(jì)實(shí)戰(zhàn)指南[M].北京:清華大學(xué)出版社,2014.

[4] KARRAS K,HRICA J.Vivado HLS推動(dòng)協(xié)議處理系統(tǒng)蓬勃發(fā)展[DB/OL].(2014-09-16)[2016-03-01].http://xilinx.eetrend.com/article/7676.

[5] 梁柱華,顧新.嵌入式Linux實(shí)時(shí)性的研究[J].電子科技,2005(11):57-60,64.

[6] 焦再?gòu)?qiáng).基于Zynq-7000的嵌入式數(shù)字圖像處理系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)[D].太原:太原理工大學(xué),2015.