文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2016.09.038

中文引用格式: 李攀,田文娟,李娟,等. FC協(xié)議處理芯片設(shè)計與實現(xiàn)[J].電子技術(shù)應(yīng)用,2016,42(9):147-151.

英文引用格式: Li Pan,Tian Wenjuan,Li Juan,et al. The design and realization of FC protocol processing chip[J].Application of Electronic Technique,2016,42(9):147-151.

0 引言

FC網(wǎng)絡(luò)以其高帶寬、低延時、擴展性好、傳輸可靠性高等特點得到了多方肯定,已廣泛應(yīng)用于民用網(wǎng)絡(luò)、存儲和數(shù)據(jù)傳輸領(lǐng)域,并成為我國新一代飛機航電系統(tǒng)通信網(wǎng)絡(luò)首選[1]。根據(jù)國際航電系統(tǒng)的發(fā)展趨勢和國內(nèi)對航電系統(tǒng)研究論證的結(jié)果,我國采用基于交換架構(gòu)的FC光纖通道網(wǎng)絡(luò)作為新一代飛機航空電子系統(tǒng)的統(tǒng)一數(shù)據(jù)通訊網(wǎng)絡(luò),并選用光纖通道航空電子環(huán)境匿名簽署消息(Fibred Channel Avionic Environment Anonymous Subscriber Messaging,FC-AE-ASM)協(xié)議作為航電系統(tǒng)間的通信標(biāo)準(zhǔn)[2]。

本文在深入研究及分析FC網(wǎng)絡(luò)協(xié)議的基礎(chǔ)上,結(jié)合我國機載航電系統(tǒng)對FC總線網(wǎng)絡(luò)的應(yīng)用需求,介紹了一種采用SoC技術(shù)實現(xiàn)FC-AE-ASM協(xié)議處理芯片的設(shè)計與實現(xiàn)過程[4],體系性地解決了制約我國FC網(wǎng)絡(luò)發(fā)展的關(guān)鍵問題及瓶頸,填補了國內(nèi)空白,實現(xiàn)了我國FC通信網(wǎng)絡(luò)研制核心器件的自主保障、自主發(fā)展。

1 研制總體思路

首先全面解讀和正確分析FC網(wǎng)絡(luò)協(xié)議及標(biāo)準(zhǔn),探索有效實現(xiàn)FC協(xié)議技術(shù)方法和途徑,經(jīng)過反復(fù)的理論分析和仿真、驗證,突破FC協(xié)議正確解讀及分析、關(guān)鍵IP設(shè)計與驗證、高速串行SerDes電路實現(xiàn)等關(guān)鍵技術(shù),開發(fā)FC協(xié)議處理關(guān)鍵IP,研制高速SerDes電路,構(gòu)建芯片F(xiàn)PGA原型,并在多個系統(tǒng)中進(jìn)行大量的應(yīng)用驗證和優(yōu)化,為芯片定義、研制及應(yīng)用打下扎實的技術(shù)基礎(chǔ),降低芯片研制風(fēng)險。

在此基礎(chǔ)上,結(jié)合系統(tǒng)需求,完成FC-AE-ASM協(xié)議處理芯片的定義、體系結(jié)構(gòu)設(shè)計及優(yōu)化;采用軟硬件協(xié)同設(shè)計[3-6]方法完成芯片的邏輯設(shè)計、虛擬原型驗證、FPGA原型驗證、協(xié)議符合性測試驗證;基于成熟工藝,完成后端物理設(shè)計、管殼定制、流片制造、封裝與測試;基于FC-AE-ASM協(xié)議處理芯片開發(fā)配套驅(qū)動軟件,為自主知識產(chǎn)權(quán)的機載FC網(wǎng)絡(luò)開發(fā)提供核心芯片及基礎(chǔ)軟件。

2 設(shè)計與實現(xiàn)

2.1 芯片功能

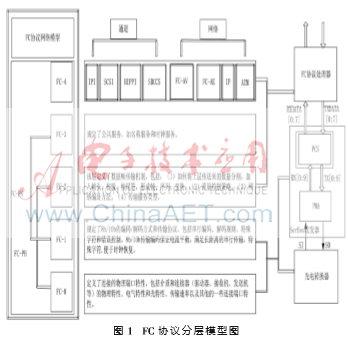

通過對FC網(wǎng)絡(luò)協(xié)議全面解讀與分析,確定使用光電轉(zhuǎn)換器和SerDes收發(fā)器模擬電路實現(xiàn)FC-0層和FC-1層的功能,F(xiàn)C協(xié)議處理器數(shù)字電路實現(xiàn)FC-2層到FC-4層的全部功能。如圖1所示。

通過對協(xié)議分層模型的反復(fù)理論分析,采用軟硬件協(xié)同設(shè)計的方式,遵循與性能或者功耗相關(guān)的功能用硬件實現(xiàn)、其他用軟件實現(xiàn)的原則。研制核心FC-MAC IP核完成FC-1、FC-2層協(xié)議的8b/10b編解碼[5]、流量控制、FC-FS協(xié)議[7-8]核心端口狀態(tài)機等功能;研制核心FC-AE-ASM協(xié)議處理核心IP,完成FC-4層中FC-AE-ASM協(xié)議中明確規(guī)定的對數(shù)據(jù)流分包和重組、組幀等內(nèi)容。結(jié)合FC-AE-ASM節(jié)點機的功能及性能需求,提出FC-AE-ASM協(xié)議處理芯片的主要功能如下:

(1)內(nèi)嵌高性能PPC460處理器,工作頻率125 MHz/250 MHz可配置;

(2)FC-FS協(xié)議處理功能和性能:支持1、2、3、6類服務(wù)和N、F、E、B端口;傳輸速率:1.062 5 Gb/s、2.125 Gb/s可選;支持幀的CRC校驗、信用管理;支持統(tǒng)計信息收集。

(3)集成FC-AE-ASM協(xié)議處理引擎:FC-AE-ASM協(xié)議通信處理功能;FC網(wǎng)絡(luò)系統(tǒng)時統(tǒng)功能;FC網(wǎng)絡(luò)運行控制功能;雙余度FC鏈路功能。

(4)集成FC高速串并轉(zhuǎn)換SerDes。

(5)存儲器控制器。片內(nèi)存儲器資源128 KB;片外存儲器接口:片上處理器程序加載Flash 32 MB;主機訪問Flash 32 MB;片上處理器程序擴展SSRAM 64 MB。

(6)外圍接口。高速PCIe主機接口支持4x、1x模式,通道速率為2.5 Gb/s;高速RapidIO主機接口支持自適應(yīng)的4x、1x模式,3種不同線速率:1.25 Gb/s、2.5 Gb/s、3.125 Gb/s;串口、GPIO接口;JTAG調(diào)試接口。

2.2 芯片架構(gòu)設(shè)計

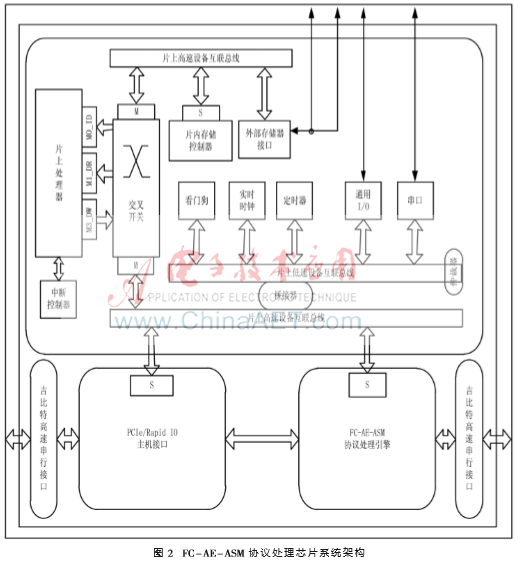

根據(jù)對FC協(xié)議標(biāo)準(zhǔn)的理解和系統(tǒng)應(yīng)用功能及性能需求的分析,提出FC-AE-ASM協(xié)議處理芯片的體系架構(gòu)如圖2所示。

FC-AE-ASM協(xié)議處理芯片提供ASM協(xié)議處理功能,其工作原理如下:

(1)發(fā)送數(shù)據(jù)時,由主機在內(nèi)存中按ASM消息格式準(zhǔn)備消息,之后啟動消息發(fā)送;主機接口DMA將數(shù)據(jù)從主機內(nèi)存的消息發(fā)送緩沖區(qū)中搬移到片內(nèi)幀緩沖;發(fā)送控制模塊將數(shù)據(jù)輸出到SerDes模塊,SerDes模塊將輸入的并行數(shù)據(jù)流轉(zhuǎn)換成2.125 Gb/s/1.062 5 Gb/s的高速串行數(shù)據(jù)流輸出到片外;

(2)接收數(shù)據(jù)時,SerDes模塊將2.125 Gb/s/1.062 5 Gb/s的片外串行輸入數(shù)據(jù)流轉(zhuǎn)換為并行數(shù)據(jù)流;接收控制模塊接收幀時查詢通信配置表,如果能查到相應(yīng)的配置項,則將ASM數(shù)據(jù)搬移到FC接收緩沖區(qū),再將其搬移到片內(nèi)消息幀緩沖;接收管理模塊判斷消息所對應(yīng)的通信配置索引項的位置,然后判斷消息接收緩沖區(qū)狀態(tài),如果可以接收則計算出緩沖地址,并啟動主機接口模塊的DMA,將ASM數(shù)據(jù)幀從片內(nèi)消息幀緩沖搬移到主機內(nèi)存的接收緩沖區(qū)中;消息的接收方式可以配置為中斷主機或主機查詢,如為中斷方式,則將消息ID保存到中斷相關(guān)寄存器中,發(fā)中斷給主機。

FC-AE-ASM協(xié)議處理芯片提供ELS幀實現(xiàn)網(wǎng)絡(luò)管理功能,其工作原理如下:

(1)發(fā)送ELS幀時,片上處理器按照ELS幀格式組幀,并寫入ELS幀發(fā)送緩沖,啟動發(fā)送,由發(fā)送控制模塊將要發(fā)送的幀從ELS發(fā)送緩沖區(qū)發(fā)送到FC MAC控制器的客戶端接口;FC MAC控制器負(fù)責(zé)將ELS幀輸出到SerDes模塊;SerDes模塊將接收到的并行數(shù)據(jù)流轉(zhuǎn)換串行數(shù)據(jù)輸出。

(2)接收ELS幀時,SerDes模塊將接收到的串行數(shù)據(jù)轉(zhuǎn)換為并行數(shù)據(jù)流;FC MAC控制器將SerDes輸出的并行數(shù)據(jù)轉(zhuǎn)換為32位的數(shù)據(jù)流從客戶端輸出;接收控制模塊從FC MAC控制器的客戶端接口將ELS幀接收到ELS幀接收緩沖區(qū),更新接收頭指針,交由片上處理器處理。

2.2.1 硬件設(shè)計

根據(jù)系統(tǒng)架構(gòu)設(shè)計得出硬件系統(tǒng),包括FC-AE-ASM協(xié)議處理模塊、PCIe主機接口、RapidIO主機接口、高速串并轉(zhuǎn)換SerDes、PPC460嵌入式處理器、其他片上資源等。

FC-AE-ASM協(xié)議處理模塊支持256個非數(shù)據(jù)塊消息和16個數(shù)據(jù)塊消息的收發(fā)控制,支持ELS幀的收發(fā),提供網(wǎng)絡(luò)管理硬件支持,具備信息交互區(qū)及命令交互寄存器,用于主機與片上處理器之間交互網(wǎng)絡(luò)管理信息數(shù)據(jù),設(shè)備控制處理功能(包括設(shè)備軟復(fù)位、ASM數(shù)據(jù)收發(fā)使能和禁止、主機和設(shè)備之間的硬件信號量、FC設(shè)備的WDT定時功能、硬件設(shè)備心跳控制和檢測)、雙余度控制功能、FC網(wǎng)絡(luò)系統(tǒng)時統(tǒng)功能。

PCIe主機接口完成從PCIe串行鏈路到用戶端邏輯之間的PCIe協(xié)議轉(zhuǎn)換和數(shù)據(jù)高速傳輸。該PCIe主機接口由PCIe協(xié)議處理模塊和DMA模塊兩部分組成。PCIe協(xié)議處理模塊實現(xiàn)了協(xié)議規(guī)定的事務(wù)層、鏈路層、物理層邏輯子塊的功能,支持端點操作,為用戶提供全面的底層PCIe狀態(tài)信息。DMA模塊支持最多2個S2C及2個C2S DMA通道,支持用戶端直接控制。

RapidIO主機接口由6部分組成:邏輯及傳輸層模塊(實現(xiàn)邏輯及傳輸層協(xié)議包括負(fù)責(zé)事務(wù)組包、拆包等功能)、物理層模塊(實現(xiàn)物理層協(xié)議包括包的控制符號傳送、流量控制、錯誤管理等功能)、寄存器管理模塊(負(fù)責(zé)對寄存器進(jìn)行讀寫操作)、寄存器組模塊(集中實現(xiàn)各層寄存器)、時鐘及復(fù)位模塊、應(yīng)用模塊(實現(xiàn)DMA、門鈴操作以及片內(nèi)資源訪問等功能)。

高速串并轉(zhuǎn)換SerDes主要完成FC-1層的8b/10b編解碼、串化/解串和不同時鐘域數(shù)據(jù)的時序轉(zhuǎn)換。

PPC460嵌入式處理器提供強大的數(shù)據(jù)處理及控制能力,通過工作在較高時鐘頻率的PLB總線和外圍設(shè)備通信,完成FC速率配置,ELS幀的接收、發(fā)送以及FC MAC的初始化配置。

其他片上資源包括片上總線、中斷控制器、定時控制器、看門狗、通用輸入輸出接口、UART接口、調(diào)試接口等。

2.2.2 軟件設(shè)計

FC-AE-ASM協(xié)議處理芯片的相關(guān)軟件為各個系統(tǒng)提供使用FC-AE-ASM協(xié)議處理芯片實現(xiàn)FC網(wǎng)絡(luò)數(shù)據(jù)傳輸?shù)腁PI接口。該軟件主要分為:(1)運行在宿主機上由用戶程序調(diào)用的FC-AE-ASM接口驅(qū)動軟件、PCIe接口驅(qū)動軟件、RapidIO接口驅(qū)動軟件;(2)運行在FC-AE-ASM協(xié)議處理芯片上的FC-AE-ASM接口底層傳輸軟件,及其他資源模塊(VIC、Uart、Timer等)的驅(qū)動軟件。

FC-AE-ASM協(xié)議處理軟件的核心部件為FC-AE-ASM接口軟件,包含F(xiàn)C-AE-ASM協(xié)議通信功能、設(shè)備管理功能、時統(tǒng)管理功能、網(wǎng)絡(luò)管理功能。實現(xiàn)結(jié)構(gòu)框圖如圖3所示。

FC-AE-ASM接口軟件功能如下:

(1)FC-AE-ASM協(xié)議通信功能。實現(xiàn)對ASM消息處理程序的注冊、注銷,通信表的加載和卸載,F(xiàn)C-AE-ASM協(xié)議非數(shù)據(jù)塊消息的封裝,ASM協(xié)議通信的啟動、停止控制,ASM消息的發(fā)送、接收控制等。航電應(yīng)用通過調(diào)用ASM通信接口實現(xiàn)不同硬件模塊之間的數(shù)據(jù)通信交互;

(2)網(wǎng)絡(luò)管理功能。實現(xiàn)網(wǎng)絡(luò)初始化控制,網(wǎng)絡(luò)系統(tǒng)管理器控制權(quán)爭奪控制。網(wǎng)絡(luò)系統(tǒng)運行結(jié)構(gòu)控制,網(wǎng)絡(luò)上/下線管理(linkup/linkdown),網(wǎng)絡(luò)上/下網(wǎng)控制(online/offline),網(wǎng)絡(luò)系統(tǒng)健康監(jiān)控,網(wǎng)絡(luò)時統(tǒng)控制,網(wǎng)絡(luò)配置數(shù)據(jù)加載及固化。航電應(yīng)用系統(tǒng)管理通過調(diào)用網(wǎng)絡(luò)管理接口實現(xiàn)對FC網(wǎng)絡(luò)運行狀態(tài)的控制及管理;

(3)設(shè)備管理功能。實現(xiàn)設(shè)備的打開、關(guān)閉,設(shè)備軟復(fù)位,設(shè)備自測試,設(shè)備狀態(tài)獲取,軟件版本獲取。航電應(yīng)用系統(tǒng)管理通過調(diào)用設(shè)備管理接口實現(xiàn)對FC網(wǎng)絡(luò)設(shè)備的管理功能;

(4)時統(tǒng)管理功能。提供一組網(wǎng)絡(luò)時鐘同步驅(qū)動控制接口,包括時鐘同步模式設(shè)置、時鐘同步使能、時鐘同步禁止、任務(wù)系統(tǒng)RTC設(shè)置、任務(wù)系統(tǒng)RTC獲取、任務(wù)系統(tǒng)同步監(jiān)控門限設(shè)置、網(wǎng)絡(luò)日歷信息設(shè)置以及網(wǎng)絡(luò)日歷信息獲取功能。

2.3 物理設(shè)計與實現(xiàn)

FC-AE-ASM協(xié)議處理芯片設(shè)計規(guī)模為1 730余萬門,芯片面積為12.3×12.3(mm2),芯片工作溫度范圍-55 ℃~125 ℃。

2.4 芯片流片、封裝

FC-AE-ASM協(xié)議處理芯片的流片制造采用SMIC 0.13 ?滋m Logic工藝,內(nèi)核電壓1.2 V,IO電壓3.3 V,封裝形式為CBGA440。

2.5 芯片驗證

2.5.1 驗證策劃

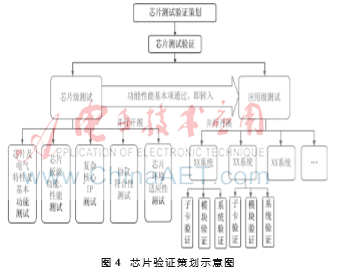

根據(jù)芯片需求以及功能定義,對芯片測試、驗證進(jìn)行詳細(xì)策劃,編制芯片樣片測試規(guī)范,依據(jù)測試規(guī)范對芯片進(jìn)行芯片級及系統(tǒng)應(yīng)用級驗證,以保證芯片功能、性能、對外接口、電氣特性以及兼容性滿足應(yīng)用要求。

芯片級測試內(nèi)容包括:電氣特性及基本功能測試、板級功能及性能測試、復(fù)雜核心IP測試、協(xié)議符合性測試及芯片的環(huán)境適應(yīng)性測試,以上測試可以基于芯片樣片同步并行開展。芯片應(yīng)用級驗證主要結(jié)合實際研制項目開展基于子卡、模塊及系統(tǒng)級的應(yīng)用驗證。具體實施如圖4所示。

2.5.2 驗證實施

芯片測試驗證從芯片級測試到應(yīng)用級測試,涵蓋FC接口2.125/1.062 5 Gb/s 2種速率、RapidIO接口1線/4線2種模式和3.125/2.5/1.25 Gb/s 3種速率、PCIe接口1線/4線2種模式、PowerPC 250/125 MHz 2種時鐘頻率,共計32種場景,每種場景下開發(fā)測試程序807項。

2.5.3 驗證結(jié)果

經(jīng)測試芯片電氣特性符合設(shè)計指標(biāo)要求,復(fù)雜核心IP SerDes測試符合測試標(biāo)準(zhǔn),協(xié)議符合FC-FS、FC-PI協(xié)議要求。系統(tǒng)應(yīng)用測試功能、性能滿足系統(tǒng)應(yīng)用需求,滿足環(huán)境適應(yīng)性設(shè)計需求。主要指標(biāo)驗證結(jié)果如表1所示。

3 技術(shù)優(yōu)勢

市場上存在的一些FC網(wǎng)絡(luò)產(chǎn)品大多都采用FPGA或ASIC方式實現(xiàn),存在板面積大、功耗高、可靠性低、通用性差等不足,已不能滿足系統(tǒng)小型化、高可靠性的要求。

與市場上的FC網(wǎng)絡(luò)產(chǎn)品相比,F(xiàn)C協(xié)議處理核心芯片符合系統(tǒng)小型化、低功耗、高性能、高可靠性、高度綜合、復(fù)雜惡劣環(huán)境等應(yīng)用要求。

以基于該芯片研制的PMC卡和市場上同類產(chǎn)品相比較,主要指標(biāo)對比情況如表2所示。

由表2可以看出,基于該芯片研制的PMC卡與市場上同類產(chǎn)品相比顯著提高了功能、性能、可靠性及FC核心產(chǎn)品的自主保障能力。

4 總結(jié)

本文針對機載航電系統(tǒng)對FC總線網(wǎng)絡(luò)的應(yīng)用需求,以及我國在FC網(wǎng)絡(luò)產(chǎn)品方面受制于人、系統(tǒng)功耗大、維護(hù)成本高的現(xiàn)狀,提出了一種采用SoC技術(shù)實現(xiàn)FC-AE-ASM協(xié)議處理芯片的設(shè)計方法。該芯片功能及性能符合設(shè)計要求,現(xiàn)已成功應(yīng)用在多個系統(tǒng)中。應(yīng)用結(jié)果表明,該芯片符合協(xié)議、系統(tǒng)等的要求。該芯片的研制體系性地解決了制約我國FC網(wǎng)絡(luò)發(fā)展的關(guān)鍵及瓶頸,填補了國內(nèi)空白,實現(xiàn)了我國FC通信網(wǎng)絡(luò)研制核心器件的自主保障和自主發(fā)展。

參考文獻(xiàn)

[1] 李攀,田澤,蔡葉芳,等.基于FPGA的雙通道FC數(shù)據(jù)采集卡設(shè)計[J].計算機技術(shù)與發(fā)展,2013,23(7):179-182.

[2] SULLIVAN W.Fibre channel: replacement for MIL-STD-1553&next generation military data bus[EB/OL].1998-09.

[3] 淮偉華.基于FC-2協(xié)議的SoC軟硬件協(xié)同設(shè)計與驗證[D].西安:陜西科技大學(xué),2009.

[4] 黎小玉,田澤.FC協(xié)議分析儀軟件設(shè)計與實現(xiàn)[J].計算機技術(shù)與發(fā)展,2013,23(8):31-34.

[5] 田澤,韓煒,蔡葉芳,等.基于FC接口的SoC軟硬件協(xié)同設(shè)計驗證平臺構(gòu)建與實現(xiàn)[C].第十三屆計算機工程與工藝會議論文集.西安:西北工業(yè)大學(xué)出版社,2009.

[6] 張艷,胡桂.SOC設(shè)計中的核心技術(shù)[J].微計算機信息,2007,23(10-2):110-112.

[7] 張丹,董雷剛,祝裕璞,等.基于SOPC嵌入式系統(tǒng)中軟硬件協(xié)同設(shè)計方法研究[J].大慶師范學(xué)院學(xué)報,2012,32(6):40-44.

[8] ANSI Fiber Channel Fhysical and Signaling Interface(FC-PH),X3[M].US:ANSI,1994.

[9] ANSI Fiber Channel Framing and Signaling-2(FC-FS-2),Rev0.01[M].US:ANSI,2003.