文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.021

中文引用格式: 王龍,楊承志,吳宏超,等. 基于FPGA的數(shù)字基帶多模雷達(dá)信號(hào)源設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2016,42(8):87-90.

英文引用格式: Wang Long,Yang Chengzhi,Wu Hongchao,et al. The design of digital multi-mode radar signal generator based on FPGA[J].Application of Electronic Technique,2016,42(8):87-90.

0 引言

隨著雷達(dá)技術(shù)的快速發(fā)展,采用復(fù)雜調(diào)制樣式、具有低截獲概率(Low Probability of Intercept,LPI)特性的雷達(dá)信號(hào)被廣泛運(yùn)用于火力引導(dǎo)和預(yù)警探測(cè)中,使得傳統(tǒng)電子偵察設(shè)備很難截獲到這類信號(hào),需要設(shè)計(jì)一個(gè)能夠模擬這些復(fù)雜調(diào)制樣式的雷達(dá)信號(hào)的設(shè)備對(duì)現(xiàn)有和新研制的電子偵察設(shè)備進(jìn)行測(cè)試,檢驗(yàn)電子偵察設(shè)備對(duì)LPI雷達(dá)信號(hào)的有效性和可靠性[1-3];此外,在生成式欺騙干擾中,需要根據(jù)偵察到的雷達(dá)信號(hào)的調(diào)制類型和參數(shù)產(chǎn)生相應(yīng)的干擾信號(hào)對(duì)目標(biāo)實(shí)施欺騙干擾[4,5],因此有必要研究一個(gè)能夠靈活產(chǎn)生多種調(diào)制樣式的多模雷達(dá)信號(hào)源。文獻(xiàn)[2]中提出一種采用ARM輸入雷達(dá)參數(shù),并通過USB接口將數(shù)據(jù)傳輸?shù)紻SP中進(jìn)行參數(shù)處理,然后傳遞給FPGA合成多種模式的雷達(dá)信號(hào)的方法,但這種產(chǎn)生多模雷達(dá)信號(hào)的方法具有整體結(jié)構(gòu)復(fù)雜、占用資源多、不利于小型化的缺點(diǎn)。本文設(shè)計(jì)了一種基于FPGA的多模雷達(dá)信號(hào)源產(chǎn)生結(jié)構(gòu),在FPGA中構(gòu)建微控制器實(shí)現(xiàn)參數(shù)的處理,降低系統(tǒng)的復(fù)雜度,提高了系統(tǒng)的集成度。

本文選用Xilinx Zynq-7 系列xc7z010clg400 FPGA芯片[6]實(shí)現(xiàn)系統(tǒng)設(shè)計(jì),上位機(jī)通過網(wǎng)口向FPGA中構(gòu)建的微控制器(MCU)發(fā)送信號(hào)描述參數(shù),微控制器經(jīng)過計(jì)算和處理得到寄存器配置參數(shù),并通過AXI(Advanced eXtensible Interface)總線[7]對(duì)自制的多模信號(hào)源IP核進(jìn)行配置,產(chǎn)生特定調(diào)制形式和特定參數(shù)的雷達(dá)信號(hào)。由于整個(gè)數(shù)字系統(tǒng)都在一片F(xiàn)PGA上實(shí)現(xiàn),降低了外部電路的設(shè)計(jì)難度,易于實(shí)現(xiàn)系統(tǒng)的小型化設(shè)計(jì),同時(shí)關(guān)鍵的多模信號(hào)源產(chǎn)生模塊被封裝成具有AXI總線結(jié)構(gòu)的IP核,提高了模塊的靈活性、易用性和重用性,通過AXI總線可以很方便地與微控制器連接實(shí)現(xiàn),并且在AXI總線上掛載多個(gè)多模雷達(dá)信號(hào)源IP核,可以模擬多部雷達(dá)信號(hào),為電子偵察設(shè)備對(duì)同時(shí)到達(dá)信號(hào)的性能檢測(cè)和生成式同時(shí)多目標(biāo)干擾提供硬件支持。經(jīng)測(cè)試,該IP核最高可工作在500 MHz 的時(shí)鐘頻率下,即數(shù)字信號(hào)的輸出速率能達(dá)500 MS/s。輸出的信號(hào)調(diào)制形式包含常規(guī)脈沖信號(hào)、線性調(diào)頻信號(hào)、相位編碼信號(hào)、頻率捷變信號(hào)、重頻抖動(dòng)信號(hào)、重頻參差信號(hào)和其他復(fù)合調(diào)制信號(hào)等。

1 關(guān)鍵技術(shù)研究

1.1 雷達(dá)信號(hào)模型

雷達(dá)信號(hào)的一般表達(dá)式可以用下式表示:

其中,A(t)表示信號(hào)的時(shí)域包絡(luò),f(t)為信號(hào)的頻率調(diào)制函數(shù), 為信號(hào)的相位偏移調(diào)制函數(shù)。從式中可以看出,雷達(dá)信號(hào)的調(diào)制方式不外乎幅度調(diào)制、頻率調(diào)制、相位調(diào)制、時(shí)間調(diào)制這四種方式及這四種調(diào)制方式的組合,其中幅度調(diào)制常見的是矩形脈沖調(diào)制,故本文不對(duì)脈沖調(diào)制作過多研究。

為信號(hào)的相位偏移調(diào)制函數(shù)。從式中可以看出,雷達(dá)信號(hào)的調(diào)制方式不外乎幅度調(diào)制、頻率調(diào)制、相位調(diào)制、時(shí)間調(diào)制這四種方式及這四種調(diào)制方式的組合,其中幅度調(diào)制常見的是矩形脈沖調(diào)制,故本文不對(duì)脈沖調(diào)制作過多研究。

以線性調(diào)頻信號(hào)為例,線性調(diào)頻信號(hào)是信號(hào)的瞬時(shí)頻率隨時(shí)間線性變化的信號(hào),其瞬時(shí)頻率可以用式(2)表示:

其中,f0為信號(hào)的初始頻率,K=B/T是信號(hào)的調(diào)頻斜率。

1.2 DDS原理和模塊設(shè)計(jì)

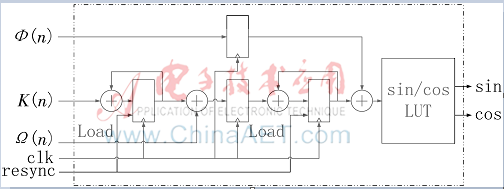

數(shù)字頻率合成器DDS(Direct Digital Synthesizer)常用于數(shù)字信號(hào)產(chǎn)生,主要包括相位累加器和正弦計(jì)算器兩部分,其中正弦計(jì)算多采用查表的方法實(shí)現(xiàn)。DDS技術(shù)同模擬方法相比,具有穩(wěn)定可靠、波形產(chǎn)生靈活、精確度高的優(yōu)點(diǎn),因此得到了廣泛應(yīng)用[8]。本文根據(jù)生成線性調(diào)頻信號(hào)的需求,設(shè)計(jì)了如圖1所示的二階相位累加結(jié)構(gòu)。雷達(dá)信號(hào)的通用表達(dá)式作離散化,可用式(3)表示:

圖1 DDS模塊結(jié)構(gòu)原理框圖

其中K(n)為時(shí)刻的調(diào)頻斜率, 為時(shí)刻的頻率偏移,

為時(shí)刻的頻率偏移, 為時(shí)刻的相位偏移。通過控制這三個(gè)量,即可輸出單載頻信號(hào)、線性調(diào)頻和相位編碼等信號(hào)調(diào)制形式。為了減少查找表對(duì)FPGA中RAM資源的消耗,本文采用相位抖動(dòng)和平衡DAC方法[9,10]對(duì)DDS 結(jié)構(gòu)進(jìn)行改進(jìn),抑制了相位截?cái)嗾`差并減小DAC非理想特性的影響,仿真結(jié)果表明采用該方法能夠有效節(jié)約73%的RAM資源。

為時(shí)刻的相位偏移。通過控制這三個(gè)量,即可輸出單載頻信號(hào)、線性調(diào)頻和相位編碼等信號(hào)調(diào)制形式。為了減少查找表對(duì)FPGA中RAM資源的消耗,本文采用相位抖動(dòng)和平衡DAC方法[9,10]對(duì)DDS 結(jié)構(gòu)進(jìn)行改進(jìn),抑制了相位截?cái)嗾`差并減小DAC非理想特性的影響,仿真結(jié)果表明采用該方法能夠有效節(jié)約73%的RAM資源。

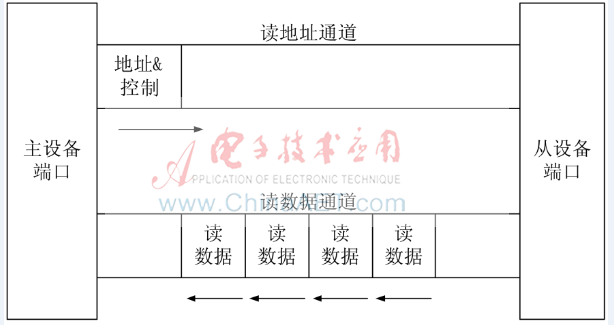

1.3 AXI總線協(xié)議

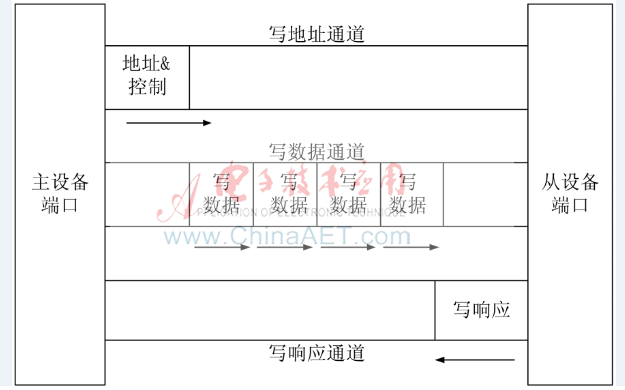

AXI總線是ARM公司提出的一種片內(nèi)總線協(xié)議,該協(xié)議是先進(jìn)微控制器總線結(jié)構(gòu)(Advanced Microcontroller Bus Architecture,AMBA)協(xié)議[7]中最重要的部分,面向高性能、高帶寬、低延遲的片內(nèi)總線。Xilinx公司提供的IP核基本都采用這種總線結(jié)構(gòu),顯著提高了系統(tǒng)設(shè)計(jì)的效率,降低了系統(tǒng)開發(fā)的復(fù)雜度。為了增強(qiáng)多模雷達(dá)信號(hào)源模塊的靈活性和重用性,本文將多模雷達(dá)信號(hào)源模塊分裝成具有AXI總線結(jié)構(gòu)的IP核。圖2為AXI總線讀寫通道結(jié)構(gòu)。

(a)AXI總線讀通道結(jié)構(gòu)

(b)AXI總線寫通道結(jié)構(gòu)

圖2 AXI總線讀寫通道結(jié)構(gòu)

AXI總線的地址、控制和數(shù)據(jù)相互是分離的,支持非對(duì)齊的數(shù)據(jù)傳輸,同時(shí)在猝發(fā)傳輸中,只需要首地址,同時(shí)具有獨(dú)立的讀寫數(shù)據(jù)通道并支持亂序訪問,能更加容易進(jìn)行時(shí)序收斂。AXI 是AMBA 中一個(gè)新的高性能協(xié)議,并且兼容原有的AHB和APB總線,使得基于原有總線結(jié)構(gòu)的組件能夠很好地與AXI總線結(jié)構(gòu)結(jié)合使用。AXI 技術(shù)豐富了現(xiàn)有的AMBA 標(biāo)準(zhǔn)內(nèi)容,滿足超高性能和復(fù)雜的片上系統(tǒng)(SoC)設(shè)計(jì)的需求。

2 多模信號(hào)源IP核設(shè)計(jì)

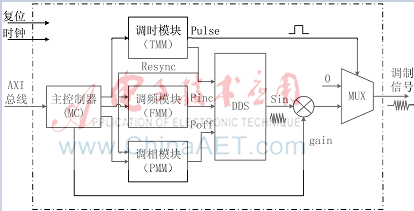

本文將所設(shè)計(jì)的多樣式雷達(dá)信號(hào)源分成時(shí)間調(diào)制模塊(Timing Modulation Module,TMM)、頻率調(diào)制模塊(Fre-quency Modulation Module,F(xiàn)MM)和相位調(diào)制模塊(Phase Modulation Module,PMM)3種調(diào)制模塊,每個(gè)模塊分別負(fù)責(zé)產(chǎn)生時(shí)域調(diào)制控制信號(hào)、頻域調(diào)制控制信號(hào)和相位調(diào)制控制信號(hào)。IP核的頂層結(jié)構(gòu)如圖3所示。

圖3 多模信號(hào)源IP核結(jié)構(gòu)框圖

其中主控制器包含所有信號(hào)樣式的配置參數(shù)寄存器和控制寄存器,MCU通過AXI總線將配置參數(shù)寫入到配置寄存器中,并通過讀寫控制寄存器實(shí)現(xiàn)對(duì)信號(hào)源的發(fā)射使能、復(fù)位等控制。調(diào)時(shí)模塊TMM產(chǎn)生單比特脈沖控制多路選擇器(MUX)在高電平期間選擇DDS 模塊的信號(hào)輸出,而在低電平期間選擇“0”輸出,同時(shí)產(chǎn)生同步信號(hào)(Resync)給調(diào)頻模塊FMM、調(diào)相模塊PMM和DDS模塊控制模塊的同步。調(diào)頻模塊產(chǎn)生相位增量值(Phase Increase,Pinc)控制信號(hào)的瞬時(shí)頻率產(chǎn)生調(diào)頻類信號(hào)。調(diào)相模塊產(chǎn)生相位偏移值(Phase Offset,Poff)控制DDS模塊輸出信號(hào)的瞬時(shí)相位偏移值,產(chǎn)生調(diào)相類信號(hào)。DDS模塊是信號(hào)的產(chǎn)生單元,在調(diào)時(shí)模塊、調(diào)頻模塊和調(diào)相模塊的控制下產(chǎn)生特定調(diào)制類型的連續(xù)信號(hào),經(jīng)乘法器按指定衰減量衰減后,通過多路選擇器產(chǎn)生具有調(diào)時(shí)特征的信號(hào),然后輸出特定樣式的雷達(dá)信號(hào)。

3 多模基帶雷達(dá)信號(hào)源總體結(jié)構(gòu)設(shè)計(jì)

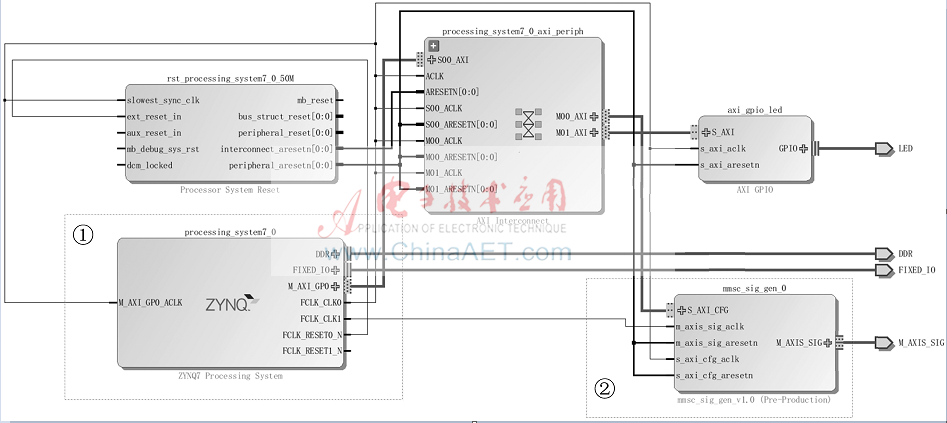

多模基帶雷達(dá)信號(hào)源總體設(shè)計(jì)結(jié)構(gòu)如圖4所示。上位機(jī)軟件通過網(wǎng)口發(fā)送信號(hào)描述參數(shù)給FPGA中的微控制器,微控制器通過計(jì)算和處理將信號(hào)描述參數(shù)轉(zhuǎn)換為多模雷達(dá)信號(hào)源IP核需要的寄存器配置參數(shù),然后多模雷達(dá)信號(hào)源IP核產(chǎn)生數(shù)字雷達(dá)信號(hào)并通過DAC輸出模擬基帶雷達(dá)信號(hào)。

在Xilinx提供的Vivado編程開發(fā)環(huán)境中,利用塊設(shè)計(jì)方式搭建FPGA上的系統(tǒng)結(jié)構(gòu),最終得到的塊設(shè)計(jì)圖如圖5所示。其中①為cortex-A9硬核,負(fù)責(zé)與上位機(jī)的網(wǎng)口通信,接收上位機(jī)下發(fā)的信號(hào)描述參數(shù)并通過計(jì)算處理產(chǎn)生多模雷達(dá)信號(hào)源IP核所需的配置寄存器參數(shù)。②為本文所設(shè)計(jì)的多模雷達(dá)信號(hào)源IP核,在cortex-A9硬核的控制下生成相應(yīng)的基帶雷達(dá)信號(hào)。

圖4 多模基帶雷達(dá)信號(hào)源總體結(jié)構(gòu)框圖

圖5 多模基帶雷達(dá)信號(hào)源塊設(shè)計(jì)視圖

4 測(cè)試與分析

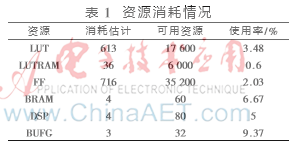

本文在Xilinx公司提供的FPGA開發(fā)環(huán)境Vivado 2015.4[11]下使用Verilog 語(yǔ)言進(jìn)行編程,將關(guān)鍵的多模信號(hào)源模塊分裝成具有AXI總線結(jié)構(gòu)的IP核,使得模塊可以方便地掛載到AXI總線系統(tǒng)中。將系統(tǒng)工作時(shí)鐘約束到500 MHz ,進(jìn)行綜合實(shí)現(xiàn),布局布線的結(jié)果表明系統(tǒng)能夠滿足500 MHz 時(shí)鐘的時(shí)序要求,并且占用資源少。其中多模信號(hào)源IP核僅占用了4個(gè)DSP核和2個(gè)BRAM(Block RAM),分別占總資源的3.3%和5%。具體資源消耗見表1。

將多模雷達(dá)信號(hào)源的系統(tǒng)工作時(shí)鐘設(shè)置為250 MHz,信號(hào)模式設(shè)置為線性調(diào)頻脈沖信號(hào)。信號(hào)的具體參數(shù)如表 2所示。

5 結(jié)論

多模雷達(dá)信號(hào)源在電子偵察設(shè)備的檢測(cè)和生成式干擾信號(hào)生成方面具有重要的應(yīng)用價(jià)值。本文提出的基于FPGA的多模雷達(dá)信號(hào)源具有占用資源少、結(jié)構(gòu)簡(jiǎn)單、生成信號(hào)多樣的特點(diǎn),能夠產(chǎn)生常見的調(diào)時(shí)、調(diào)頻和調(diào)相信號(hào)以及這些調(diào)制方法的組合。最高輸出信號(hào)的數(shù)據(jù)速率為500 MHz。

參考文獻(xiàn)

[1] 吳宇,顧村鋒,趙學(xué)州.低成本多通道注入式雷達(dá)信號(hào)模擬源設(shè)計(jì)方法[J].艦船電子工程,2016(2):58-60.

[2] 史高,胡兆峰.基于BF533和FPGA的雷達(dá)信號(hào)模擬器設(shè)計(jì)實(shí)現(xiàn)[J].電子科技,2015(1):32-35.

[3] 李楊.多模式軟件化雷達(dá)波形產(chǎn)生的技術(shù)研究[D].成都:電子科技大學(xué),2013.

[4] 何亮,李煒,郭承軍.生成式欺騙干擾研究[J].計(jì)算機(jī)應(yīng)用研究,2016(8).

[5] 馬克,孫迅,聶裕平.GPS生成式欺騙干擾關(guān)鍵技術(shù)[J].航天電子對(duì)抗,2014(6):24-26.

[6] Xilinx Corporation.Zynq-7000 All Programmable SoC Overview[EB/OL].(2016-01).http://www.xilinx.com/support/docu mentation/data_sheets/ds190-Zynq-7000-Overview.pdf.

[7] ARM Corporation.AMBA AXI Protocol(Version:2.0) Speci-fication.[EB/OL](2010-3-3).http://www.arm.com/products/system-ip/amba- specification.php.

[8] 顧趙宇,王平,傅其詳.一種基于DDS的信號(hào)源的設(shè)計(jì)與實(shí)現(xiàn)[J].現(xiàn)代電子技術(shù),2015,38(5):51-53.

[9] 王碩,馬永奎,高玉龍,等.基于FPGA的改進(jìn)結(jié)構(gòu)的DDS設(shè)計(jì)與實(shí)現(xiàn)[J].微電子技術(shù),2016(3):28-30.

[10] Xilinx Corporation.LogiCORE IP DDS Compiler v6_0[EB/OL].(2013-11-18).http://www.xilinx.com/support/docu-menta-tion/ip_documentation/pg141-dds-compiler.pdf.

[11] Xilinx Corporation.Vivado Design Suite User Guide:Designing with IP.[EB/OL](2014-5-1).http://www.xilinx.com/support/documentation/sw_manuals/ug896-vivado-ip.pdf.