關(guān)鍵詞:

FPGA

FPGA" alt="FPGA中六種異步邏輯轉(zhuǎn)化方法.jpg"/>

FPGA" alt="FPGA中六種異步邏輯轉(zhuǎn)化方法.jpg"/>

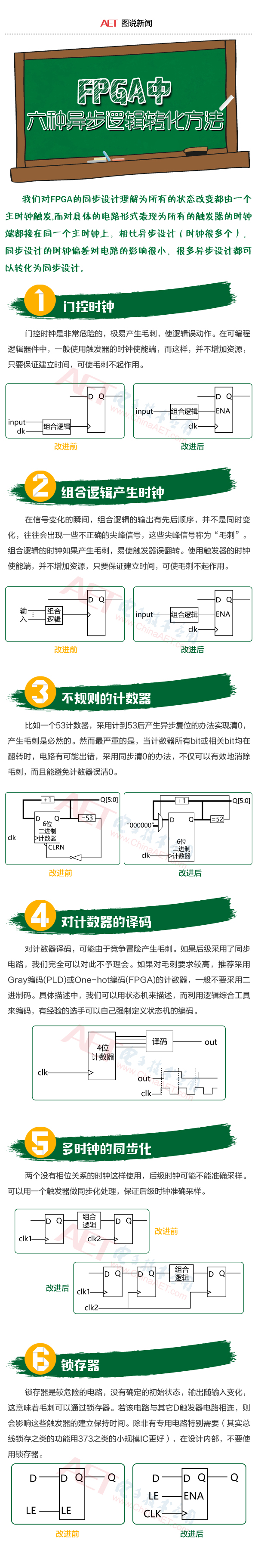

FPGA設(shè)計中不建議使用電路:

1、不建議使用組合邏輯時鐘或門控時鐘。組合邏輯和門控時鐘很容易產(chǎn)生毛刺,用組合邏輯的輸出作為時鐘很容易使系統(tǒng)產(chǎn)生誤動作。

2、 不建議使用行波時鐘。行波記數(shù)器雖然原理簡單,設(shè)計方便,但級連時鐘(行波時鐘)最容易造成時鐘偏差(△T),級數(shù)多了,很可能會影響其控制的觸發(fā)器的建立/保持時間,使設(shè)計難度加大。轉(zhuǎn)換的方法是采用同步記數(shù)器,同步計數(shù)器用原理圖描述可能較難,但用HDL語言很簡單就可以描述一個4位計數(shù)器。

3、盡量避免采用多個時鐘,多使用觸發(fā)器的使能端來解決。在可編程邏輯器件設(shè)計時,由于時鐘建立應(yīng)盡量避免采用多時鐘網(wǎng)絡(luò),或者采用適當?shù)拇胧p少時鐘的個數(shù),使用頻率低的時鐘盡量簡化消除。

4、 觸發(fā)器的置/復(fù)位端盡量避免出現(xiàn)毛刺,及自我復(fù)位電路等,最好只用一個全局復(fù)位信號。

5、 電路中盡量避免“死循環(huán)”電路,如RS觸發(fā)器等。

6 、禁止時鐘在不同可編程器件中級連,盡量降低時鐘到各個器件時鐘偏差值。

本站內(nèi)容除特別聲明的原創(chuàng)文章之外,轉(zhuǎn)載內(nèi)容只為傳遞更多信息,并不代表本網(wǎng)站贊同其觀點。轉(zhuǎn)載的所有的文章、圖片、音/視頻文件等資料的版權(quán)歸版權(quán)所有權(quán)人所有。本站采用的非本站原創(chuàng)文章及圖片等內(nèi)容無法一一聯(lián)系確認版權(quán)者。如涉及作品內(nèi)容、版權(quán)和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經(jīng)濟損失。聯(lián)系電話:010-82306118;郵箱:[email protected]。