馮建文,王春

(杭州電子科技大學(xué) 計算機(jī)應(yīng)用所,浙江 杭州 310018)

摘要:介紹了FPGA遠(yuǎn)程實驗系統(tǒng)的組成、工作原理以及遠(yuǎn)程配置,著重介紹FPGA遠(yuǎn)程實驗系統(tǒng)的遠(yuǎn)程配置的原理及具體實現(xiàn),即在ARM微控制器的主導(dǎo)下,通過以太網(wǎng)實現(xiàn)FPGA配置數(shù)據(jù)的傳輸和下載,然后由ARM作為時序控制器,通過FPGA的從串(slave serial)配置方式,完成FPGA的遠(yuǎn)程配置。在FPGA配置的同時,通過研究配置管腳輸出的波形,來驗證FPGA從串配置模式下的配置原理。

關(guān)鍵詞:FPGA;遠(yuǎn)程實驗系統(tǒng);遠(yuǎn)程配置;ARM

0引言

近年來,使用可編程器件 FPGA/CPLD 和 VHDL 進(jìn)行硬件設(shè)計發(fā)展快速,可編程邏輯器件逐漸取代了傳統(tǒng)通用的中、小規(guī)模集成電路而得到廣泛的應(yīng)用,并且隨著系統(tǒng)的復(fù)雜程度越來越高,借助在電子系統(tǒng)的開發(fā)過程中具有重要作用的EDA(Electronic Design Automation)軟件,使得FPGA 成為數(shù)字邏輯電路設(shè)計、計算機(jī)組成原理、嵌入式系統(tǒng)等課程實驗教學(xué)的首選方式[1]。同時隨著嵌入式技術(shù)以及網(wǎng)絡(luò)技術(shù)的發(fā)展,遠(yuǎn)程控制也變得越來越容易實現(xiàn),把遠(yuǎn)程控制技術(shù)引入到FPGA實驗系統(tǒng)中來,利用FPGA可重復(fù)編程的特點,實現(xiàn)FPGA實驗操作遠(yuǎn)程執(zhí)行,從而實現(xiàn)實驗設(shè)備的遠(yuǎn)程共享和實驗設(shè)備的最大利用。

1FPGA工作原理及配置

現(xiàn)場可編程門陣列(Field Programmable Gate Array,F(xiàn)PGA)是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點[2]。以硬件描述語言(Verilog或VHDL)所完成的電路設(shè)計,可以經(jīng)過簡單的綜合與布局,快速燒錄至FPGA上進(jìn)行測試,是現(xiàn)代 IC設(shè)計驗證的技術(shù)主流。

FPGA利用小型查找表(16×1 RAM)來實現(xiàn)組合邏輯,每個查找表連接到一個D觸發(fā)器的輸入端,觸發(fā)器再來驅(qū)動其他邏輯電路或驅(qū)動I/O,由此構(gòu)成了既可實現(xiàn)組合邏輯功能又可實現(xiàn)時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。在FPGA正常工作時,配置數(shù)據(jù)存儲在SRAM單元中,這個SRAM單元也被稱為配置存儲器(Configuration RAM)。由于SRAM是易失性的存儲器,因此FPGA在上電之后,外部電路需要將配置數(shù)據(jù)重新載入到片內(nèi)的配置RAM中[3]。FPGA的配置過程如下:外部電路將配置數(shù)據(jù)載入片內(nèi)配置RAM中;片內(nèi)配置RAM中的配置數(shù)據(jù)用于控制FPGA內(nèi)部可編程的內(nèi)部邏輯、內(nèi)部寄存器和I/O寄存器初始化、I/O驅(qū)動器使能等。配置完成后,F(xiàn)PGA進(jìn)入用戶模式。在掉電后,F(xiàn)PGA又恢復(fù)成白片,內(nèi)部邏輯關(guān)系消失。

FPGA一般有4種配置模式:從串模式(Slave Serial)、主串模式(Master Serial)、從并模式(Slave Parallel/SelectMap)以及邊界掃描模式(Boundary Scan)。配置模式的選擇一般由FPGA芯片上配置模式選擇引腳的輸入電平?jīng)Q定[4]。

從串配置模式是指在進(jìn)行配置時,由外部控制器主導(dǎo)同步時鐘輸入,將配置數(shù)據(jù)一位一位地加載進(jìn)FPGA;主從配置模式則是在FPGA內(nèi)部同步時鐘的作用下,將配置數(shù)據(jù)從外部存儲器按位串行加載到FPGA中;從并模式則是將配置數(shù)據(jù)多位數(shù)據(jù)一起并行輸入;而邊界掃描模式即JTAG配置模式,JTAG模式在開發(fā)調(diào)試階段使用。

2基于ARM的遠(yuǎn)程實驗系統(tǒng)

基于ARM的遠(yuǎn)程實驗系統(tǒng)主要功能是實現(xiàn)遠(yuǎn)程FPGA的實驗操作。用戶通過該系統(tǒng),能夠在PC端登錄該實驗系統(tǒng),進(jìn)行預(yù)約FPGA實驗,同時能夠發(fā)送FPGA控制命令,并且能夠得到實驗結(jié)果信息。系統(tǒng)結(jié)構(gòu)如圖1所示,主要分為3個模塊:PC客戶端、服務(wù)器端和ARMFPGA模塊。PC客戶端為用戶提供遠(yuǎn)程實驗操作接口,服務(wù)器端則主要負(fù)責(zé)數(shù)據(jù)或命令的發(fā)送和接收,而ARMFPGA模塊則是進(jìn)行控制和執(zhí)行客戶端發(fā)來的命令,并向服務(wù)器返回實驗結(jié)果。

2.1PC客戶端

客戶端的主要作用是提供用戶操作接口,為用戶提供遠(yuǎn)程操作ARM控制器的界面,方便用戶控制FPGA的配置及相關(guān)的FPGA實驗操作。客戶端的設(shè)計主要采用C/C++編程,采用Socket編程模式進(jìn)行配置數(shù)據(jù)的發(fā)送和配置結(jié)果數(shù)據(jù)的返回。

2.2服務(wù)器端

服務(wù)器是基于FPGA實驗平臺的遠(yuǎn)程實驗系統(tǒng)的核心,負(fù)責(zé)控制實驗系統(tǒng)的運行。它負(fù)責(zé)FPGA實驗平臺的調(diào)度管理,給實驗用戶(PC客戶端)分配空閑的實驗平臺。并且需要能連接上百個ARM客戶端和PC客戶端,作為兩種客戶端之間的信息中轉(zhuǎn)站。同時,服務(wù)器還負(fù)責(zé)管理數(shù)據(jù)庫,及時進(jìn)行學(xué)生信息、FPGA平臺信息、預(yù)約記錄和實驗記錄等信息的記錄和更新。

2.3ARM客戶端

ARM客戶端作為系統(tǒng)整體結(jié)構(gòu)中的重要組成部分,是與FPGA實驗平臺進(jìn)行數(shù)據(jù)交互的唯一接口,它主要實現(xiàn)如下功能:

(1)連接服務(wù)器,接收PC客戶端發(fā)來的指令信息,還需接收存儲FPGA配置執(zhí)行文件。

(2)解析指令,調(diào)用程序完成指令。

(3)實現(xiàn)FPGA動態(tài)配置,把配置文件加載到FPGA運行。

(4)連接PC客戶端,實時將FPGA相關(guān)引腳的信息發(fā)送到PC客戶端。

(5)實現(xiàn)對FPGA實驗平臺上開關(guān)、按鍵的遠(yuǎn)程控制操作。

3FPGA遠(yuǎn)程配置的實現(xiàn)

在本次實驗中,選用ARM9開發(fā)板+FPGA實驗板來完成FPGA遠(yuǎn)程配置的具體實現(xiàn)。其中ARM控制器采用以ARM9為處理器的單片機(jī)開發(fā)板。ARM9開發(fā)板支持網(wǎng)絡(luò)接口連接,并且成功地移植了Linux 2.6.30內(nèi)核操作系統(tǒng)以及相應(yīng)的文件系統(tǒng),為Socket網(wǎng)絡(luò)編程和ARM客戶端的軟件實現(xiàn)與執(zhí)行提供了良好的Linux環(huán)境。FPGA則使用為計算機(jī)組成原理所設(shè)計的FPGA實驗板卡,該實驗板卡所用的FPGA芯片為Xilinx生產(chǎn)的Spartan-6系列芯片,并將其專用的配置接口引出,方便后續(xù)的實驗操作。

3.1配置文件

本設(shè)計所用的FPGA的配置數(shù)據(jù)格式為.bin格式,是由Xilinx的FPGA設(shè)計工具ISE軟件產(chǎn)生的FPGA配置數(shù)據(jù)的一種格式,也是進(jìn)行Spartan-6系列芯片進(jìn)行從串配置的配置數(shù)據(jù)格式。在PC客戶端可通過Socket編程配置引腳

將文件由網(wǎng)絡(luò)傳送至ARM控制器客戶端。

3.2配置電路

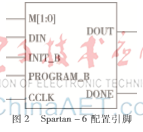

Spartan-6配置引腳如圖2所示,各個引腳的功能如表1所示。表1FPGA配置引腳說明引腳名類型說明M[1:0]輸入模式選擇引腳,決定FPGA的配置模式CCLK輸入/輸出除JTAG配置模式外其他配置模式的同步時鐘源DIN輸入串行配置數(shù)據(jù)輸入引腳,同步于時鐘的上升沿DOUT輸出用于菊花鏈配置器件后面的器件配置數(shù)據(jù)的串行輸入DONE輸出高電平表示配置完成,低電平表示配置失敗INIT_B輸入/輸出在配置模式選擇完成前,拉低該引腳電平表示延遲配置;配置模式選擇完成后,該引腳的電平輸出表示配置有無發(fā)生CRC校驗錯誤:

0=CRC error

1=No CRC errorPROGRAM_B輸入低電平輸入使芯片復(fù)位

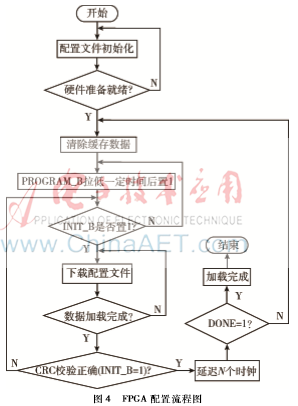

3.3配置流程

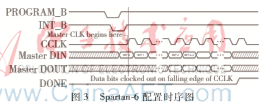

Spartan-6芯片的配置時序如圖3所示,先給PROGRAM_B引腳一個低電平信號,然后再恢復(fù)高電平,檢測INIT_B引腳電平信號,如果其電平信號也隨著PROGRAM_B而變化,則表明FPGA內(nèi)部配置已經(jīng)完成初始化,可以進(jìn)行FPGA配置了。接下來在ARM輸入到FPGA的DCLK引腳的信號的同步下,按位加載配置數(shù)據(jù),直到加載完配置數(shù)據(jù)。當(dāng)檢測到DONE引腳信號變?yōu)楦唠娖綍r,表明FPGA已經(jīng)完成配置,進(jìn)入到工作狀態(tài)了。其配置程序的流程圖如圖4所示。

4實驗結(jié)果分析

實驗時,將FPGA的配置引腳DIN、CCLK、INIT_B、DONE、PROGRAM_B連接到ARM開發(fā)板的I/O引腳上,同時注意ARM開發(fā)板和FPGA實驗板卡要共地,將ARM開發(fā)板接上網(wǎng)線,供電并啟動后,通過PC客戶端進(jìn)行配置文件的傳輸和加載,當(dāng)配置完成后返回客戶端“config done!”則表示配置完成。實驗結(jié)果演示如圖5所示。

為了得到配置過程中DIN引腳和CCLK引腳的數(shù)據(jù),在程序中進(jìn)行了配置數(shù)據(jù)輸出,并用示波器捕捉到這兩個引腳的輸出波形,如圖6所示。由圖可以看出,在一個配置循環(huán)中,ARM控制器是按字節(jié)進(jìn)行位傳輸?shù)模總€字節(jié)8位數(shù)據(jù),在每輸入一個時鐘過程中,輸入一位配置數(shù)據(jù),直至加載完所有配置數(shù)據(jù),完成FPGA的配置。

5結(jié)論

本設(shè)計中采用兩個獨立模塊的連接來實現(xiàn)總體功能,而且ARM控制器的一些操作命令是通過串口進(jìn)行命令傳輸實現(xiàn)的。在接下來的FPGA遠(yuǎn)程實驗系統(tǒng)中,將完全通過單網(wǎng)線進(jìn)行ARM所有操作命令的實現(xiàn),并且不僅能完成FPGA的遠(yuǎn)程配置,還能完成FPGA的遠(yuǎn)程實驗——遠(yuǎn)端實、近端虛的遠(yuǎn)程FPGA實驗,即在客戶端電腦上完成界面上開關(guān)、按鍵等操作,這些操作命令通過網(wǎng)線傳遞到ARM端,控制FPGA相關(guān)引腳的輸入高低電平,并返回相關(guān)引腳的輸出電平,在客戶端電腦上通過LED或數(shù)碼管來顯示該引腳電平的高低。

參考文獻(xiàn)

[1] 丁偉, 肖鐵軍. 基于FPGA的通用實驗平臺的設(shè)計與實現(xiàn)[J]. 無線通信技術(shù), 2013, 22(4):38-39.

[2] 劉笑嫘, 何廣平. FPGA芯片的配置與下載[J]. 科技信息, 2011(15):109-109.

[3] 高闖, 吳利華, 芳羅,等. 一種用于FPGA的可配置存儲器設(shè)計[J]. 固體電子學(xué)研究與進(jìn)展, 2016,36(1):67-67.

[4] 陳曦, 沈佐峰. 一種可靠的FPGA動態(tài)配置方法及實現(xiàn)[J]. 通信技術(shù), 2012, 45(3):105-107.