文獻(xiàn)標(biāo)識碼: A

文章編號: 0258-7998(2014)04-0048-04

隨著數(shù)字化變電站的發(fā)展以及分布式網(wǎng)絡(luò)的廣泛應(yīng)用,對于系統(tǒng)的時間同步精度和穩(wěn)定性要求越來越高[1-2]。本文設(shè)計實(shí)現(xiàn)了時鐘對時同步的系統(tǒng)方案和軟件實(shí)現(xiàn)過程,其基于ADI公司的BF518高性能DSP,包含支持IEEE-1588協(xié)議的模塊以及具有硬件時間戳功能的TSYNC模塊[3-4]。

基于IEEE-1588協(xié)議的主從時鐘通過周期性地交互帶有時間戳的報文計算出時間偏差和頻率偏差,并采用適當(dāng)?shù)姆椒ㄕ{(diào)整時鐘的時間和頻率,從而達(dá)到時鐘同步的目的。其中報文攜帶的時間戳的精度是決定時鐘對時精度的一個重要因素[5]。

1 系統(tǒng)模塊方案

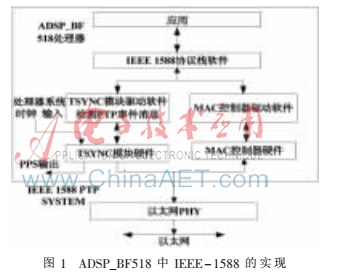

圖1所示是一個建立在ADSP_BF518處理器中的完整的兼容IEEE-1588 2008版本的系統(tǒng)。處理器的TSYNC模塊探測傳入和傳出的IEEE-1588消息以及使用硬件標(biāo)記事件消息的時間戳。IEEE-1588協(xié)議棧完成標(biāo)準(zhǔn)要求的消息交換。TSYNC驅(qū)動負(fù)責(zé)讀寫和調(diào)整TSYNC時鐘,以及使用MAC控制器驅(qū)動發(fā)送和接收以太網(wǎng)MAC層(開放式系統(tǒng)互聯(lián)的第二層)消息。同時也完成控制律和過濾P2P延時測量。以太網(wǎng)PHY芯片采用美國國家半導(dǎo)體的DP83848,因?yàn)樗哂械偷难訒r抖動特性。采用處理器50 MHz系統(tǒng)時鐘作為TSYNC模塊的時鐘源。

2 ADSP_BF518處理器的TSYNC模塊

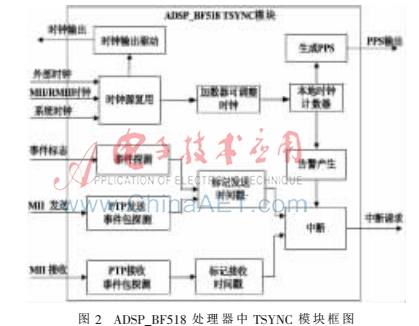

ADSP_BF518擁有一個內(nèi)置的EMAC模塊,具有支持由額外的TSYNC模塊擴(kuò)展的包含在IEEE-1588標(biāo)準(zhǔn)協(xié)議內(nèi)的EMAC功能的能力;同時額外的特性是支持以太網(wǎng)中廣泛的IEEE-1588應(yīng)用。圖2所示是TSYNC模塊的框圖。

ADSP_BF518處理器具有如下特性:

(1)包探測:ADSP_BF518處理器能夠探測和提供硬件時間戳給所有的IEEE-1588事件消息,包括傳入和傳出包。IEEE-1588系統(tǒng)的精度主要依賴于事件消息的時間戳精度和時間戳標(biāo)記的時機(jī),因?yàn)檫@些影響了路徑延時對稱和不變的前提要求。TSYNC模塊一直監(jiān)視MAC控制器與以太網(wǎng)PHY之間的硬件接口(即MII層接口),并為任何時候探測到的事件消息生成硬件時間戳。由于物理層對報文傳輸?shù)难訒r很小且?guī)缀鯚o延時波動,因而可以得到很高的時間標(biāo)記精度[6]。事件消息的探測被設(shè)計為可編程的,基本可配置為支持IEEE-1558 2002版本或IEEE-1588 2008版本。此外,此種可編程特性允許支持IEEE-1588將來的版本,也可以支持需要時間戳的通用協(xié)議,包括配置打入時間戳到進(jìn)入或傳出的每個以太網(wǎng)包。

(2)靈活的時鐘源:本地時鐘的屬性對于IEEE-1588系統(tǒng)的性能至關(guān)重要。為滿足各種應(yīng)用的需求,ADSP_BF518處理器允許本地時鐘源有3個選項(xiàng):系統(tǒng)時鐘、外部時鐘、以太網(wǎng)時鐘。如果應(yīng)用程序有特定的時鐘要求,可選擇外部時鐘以提供定制的時鐘源。以太網(wǎng)時鐘的選擇可以提供很好的精度,如果主從設(shè)備連接在同一個回路,因?yàn)閰⒖紩r鐘來自以太網(wǎng)線,所以兩個設(shè)備運(yùn)行相同的時鐘。通常的應(yīng)用可以選擇系統(tǒng)時鐘作為時鐘源。被選的時鐘源也是由TSYNC模塊驅(qū)動,并通過特定的ClockOut引腳作為處理器的一個輸出,被系統(tǒng)的其他部分用來獲取本地時間信息。

(3)可調(diào)時鐘:TSYNC模塊的可調(diào)時鐘是基于加數(shù)器的時鐘。如圖3所示,輸入固定的時鐘信號,輸出一個脈沖變少了的輸入信號:每一次輸入時鐘,加數(shù)器的值會被加到累加器,每次累加器的溢出產(chǎn)生的進(jìn)位會驅(qū)動本地時間計數(shù)器,時間計數(shù)器是以脈沖的數(shù)目表征本地時間信息。可以通過改變加數(shù)器的值來調(diào)整本地時鐘的頻率,因?yàn)榧訑?shù)器決定累加器溢出的頻率,從而決定本地時鐘計數(shù)器增加的頻率,因而可達(dá)到調(diào)整本地時鐘的目的。如式(1)所示,F(xiàn)in是輸入時鐘的頻率,A是加數(shù)器的值,F(xiàn)out是本地時鐘頻率。

3 影響時鐘同步精度的因素

在IEEE1588精確時鐘協(xié)議進(jìn)行主從時鐘同步的過程中,由主時鐘先發(fā)送同步報文。從時鐘收到同步報文時,根據(jù)同步報文中的時間戳和線路延時計算出與主時鐘的偏差,對本地時鐘進(jìn)行調(diào)整。

在同步過程中,要滿足一些基本的前提條件。其中包括:同步系統(tǒng)子網(wǎng)內(nèi)的主從時鐘通信傳輸延時須對稱,如不對稱不可忽略,則必須做出補(bǔ)償;時鐘內(nèi)的晶體振蕩器應(yīng)具有足夠好的固有穩(wěn)定性。同步計算方式如下:

式中:D為主從時鐘線路的平均延時(D的存在是因?yàn)閺臅r鐘得到的時間是主時鐘發(fā)出包的時間戳,Tmk-Tsk是主從時間差),在系統(tǒng)啟動時設(shè)為默認(rèn)值0;Ok為第k次同步時從時鐘計算出的與主時鐘的偏差;Tmk和Tsk分別為第k次同步時,主時鐘和從時鐘在底層記錄的時間戳;T為本次同步修改系統(tǒng)時鐘前的PTP系統(tǒng)時間,T為本次同步后的PTP系統(tǒng)時間[7]。

主從時鐘通過交換時間消息的方式達(dá)到同步,存在如下局限性:

(1)主時鐘發(fā)送攜帶時間信息的廣播報文的時間間隔不能無限大。因?yàn)閺臅r鐘將使用自身精度低的振蕩器打入時間戳到接收到的廣播報文,如果報文的時間間隔過大,會導(dǎo)致主從時鐘隨著時間的推移偏差逐漸增大。如式(1)主從時鐘振蕩器的特點(diǎn)不同引起的偏差Ok,如果時鐘內(nèi)的晶體振蕩器的固有穩(wěn)定性不夠好,那么偏差Ok會更大,間隔時間內(nèi)產(chǎn)生的同步誤差就更大。

(2)如式(1)所示,主從時鐘的線路延時存在一定的誤差D,增加了額外的偏移值,間隔時間內(nèi)產(chǎn)生的同步誤差也就相應(yīng)地增加。

(3)如果路徑平均延時D在主從時鐘間不對稱,即無法通過平均值計算得到D,那么隨著D的準(zhǔn)確度降低,將進(jìn)一步導(dǎo)致主從時鐘間的同步精度降低。

4 主從時鐘延時計算和調(diào)整從時鐘時間的實(shí)現(xiàn)

如式(2)中Ok=Tmk+D-Tsk所示,Tmk和Tsk分別為第k次同步時,主時鐘和從時鐘記錄的時間戳,為已知的時間信息。因此只要計算出平均路徑延時D,就可以得出Ok,從而最終算出同步后的從時鐘時間T。

主從時鐘的振蕩器越相似,則平均路徑延時D越準(zhǔn)確,那么從時鐘同步時間的精度就越高。IEEE-1588協(xié)議提供以下方法提高平均路徑延時D的準(zhǔn)確度:

(1)由于主從時鐘設(shè)備對同步報文的協(xié)議棧處理和操作系統(tǒng)調(diào)度存在不確定的延時抖動,造成平均路徑延時D變化大,準(zhǔn)確度降低,從而降低了同步精度。IEEE-1588提出越往底層打上時間戳,精度越高。從而消除了軟件處理帶來的不確定性延時抖動,提高了同步精度。

(2)在IEEE-1588第二版本引入的對等時鐘中,對不對稱的路徑延時必須做出修正,提高了平均路徑延時D的準(zhǔn)確度,從而提高了同步精度。

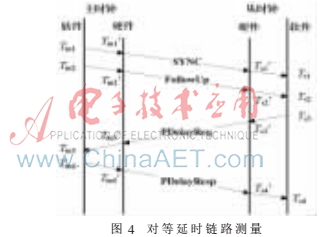

更新版本的IEEE-1588 2008進(jìn)一步引入了對等時鐘延時機(jī)制,同時增加了3個額外的事件消息,分別為PdelayReq、PdelayRespFollowUp和PdelayResp。圖4所示包括對等時鐘的事件消息交互過程以及時間戳產(chǎn)生的時刻和過程。

如圖4所示,可以把延時計算分為兩個過程:主時鐘到從時鐘的延時和從時鐘到主時鐘的延時。

4.1 主時鐘到從時鐘的延時計算過程

SYNC和FollowUp消息是由主時鐘發(fā)出,從時鐘對消息作出響應(yīng)并計算出主時鐘到從時鐘的傳輸延時[8]。

主時鐘設(shè)備讀取軟件時間戳Tm1,插入到SYNC消息中,然后發(fā)送此消息。接著在SYNC消息離開設(shè)備時,主時鐘設(shè)備物理層會自動在SYNC消息中的相應(yīng)字段打上硬件時間戳。SYNC消息到達(dá)從時鐘時,從時鐘物理層打上硬件時間戳T,隨后被從時鐘軟件接收,標(biāo)記軟件時間戳Ts1。從時鐘軟件讀取接收硬件時間戳T,以便計算主時鐘到從時鐘的傳輸延時。如果沒有傳輸延時,則Ts1′=Tm1′+Tms成立,其中Tms是主從時鐘間的時間差。1588 協(xié)議的最終目標(biāo)就是要補(bǔ)償該時間差。

SYNC發(fā)送完成后,主時鐘設(shè)備軟件讀取SYNC消息時間戳單元的離開時間T,并把T插入到FollowUp消息中,然后在軟件時間戳Tm2發(fā)送FollowUp消息。FollowUp消息在從時鐘設(shè)備的軟件時間戳Ts2收到。此時,從時鐘設(shè)備軟件有兩個時間點(diǎn)T和T,分別為SYNC到達(dá)時間戳和SYNC離開時間戳。主從時鐘路徑延時Tmsd:

![WD`YE1YKV}0]8]IT12_}{J1.png WD`YE1YKV}0]8]IT12_}{J1.png](http://files.chinaaet.com/images/2017/01/16/6362017811924453857241291.png)

4.2 從時鐘到主時鐘的延時計算過程

PDlayReq消息由從時鐘設(shè)備發(fā)送,主時鐘接收到PDlayReq消息后,發(fā)送PDlayResp消息作為回應(yīng)。通過此過程,從時鐘設(shè)備可以計算出從時鐘到主時鐘的傳輸路徑延時。

如圖4所示,在時刻Ts3,從時鐘設(shè)備軟件讀取當(dāng)前的系統(tǒng)時間Ts3,并插入到PDlayReq消息中,然后發(fā)送出去。發(fā)送完成后,從時鐘設(shè)備軟件讀取消息離開設(shè)備的硬件時間戳T,并等待主時鐘設(shè)備的回應(yīng)。

隨后PDlayReq消息到達(dá)主時鐘設(shè)備,物理層標(biāo)記硬件時間戳T,且在軟件時間戳Tm3時刻被主時鐘設(shè)備軟件處理。軟件讀取PDlayReq消息到達(dá)主時鐘設(shè)備的硬件時間戳T,并插入到PDlayResp消息中,然后在軟件時間戳Tm4時刻發(fā)送給從時鐘。當(dāng)從時鐘設(shè)備軟件在軟件時間戳Ts4接收到PDlayReq消息時,從時鐘設(shè)備軟件讀取該消息硬件時間戳T。此時,從時鐘設(shè)備軟件具有兩個已知時間戳T,可以得出從時鐘到主時鐘的延時計算公式:

在式(3)、式(4)中,有一個未知量即主從時鐘間的時間差Tms,所以不可能求解出Tmsd或Tsmd。然而IEEE-1588協(xié)議的一個重要的假設(shè)為“傳輸路徑是對稱的”,即Tmsd=Tsmd=Td。那么可以得出平均路徑延時Td:

![5~QKVVA9L2~XX7Q]H8$$2W0.png 5~QKVVA9L2~XX7Q]H8$$2W0.png](http://files.chinaaet.com/images/2017/01/16/6362017814509253859788380.png)

從時鐘需同步于主時鐘的時間,以上所有的計算由從時鐘完成。從時鐘從主時鐘設(shè)備的FollowUp消息中得到T,接收FollowUp消息后得到自身的接收硬件時間戳T,發(fā)送PDlayReq消息得到自身的發(fā)送硬件時間戳T以及從主時鐘設(shè)備PDlayResp消息中抽取的硬件時間戳T。

4.3 從時鐘時間調(diào)整

計算出從主時鐘之間的時延后,需對從時鐘作出時間調(diào)整。這里包括兩方面:(1)需加上與主時鐘的絕對偏差以調(diào)整自身的絕對時間;(2)調(diào)整自身的時鐘頻率與主時鐘同步。

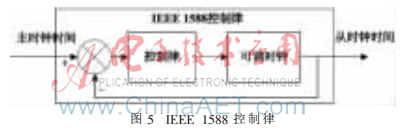

如圖5所示,調(diào)整從時鐘的控制律,從時鐘與主時鐘之間的差別驅(qū)動了可調(diào)時鐘的運(yùn)行。可調(diào)時鐘分兩個步驟進(jìn)行,使得從時鐘的時間增長不產(chǎn)生向前跳躍或向后折回:(1)當(dāng)時間差大于1 s時,從時鐘采用絕對時間調(diào)整;(2)當(dāng)時間差在1 s內(nèi)時,從時鐘采用頻率調(diào)節(jié)。

5 試驗(yàn)測試結(jié)果

測試環(huán)境是采用兩塊時鐘板卡直接連接進(jìn)行主從時鐘的對時,主從時鐘輸出的PPS通過示波器保存處理。圖6所示是實(shí)驗(yàn)測試數(shù)據(jù),橫坐標(biāo)為對時次數(shù),縱坐標(biāo)為主從時延,單位為ns。

正值處理后的主從時鐘對時數(shù)據(jù)如表1所示。實(shí)驗(yàn)數(shù)據(jù)表明,主從時鐘對時精度在100 ns之內(nèi),且有90.26%的數(shù)據(jù)在50 ns內(nèi)。

由實(shí)驗(yàn)測試數(shù)據(jù)可知,對時精度滿足電力系統(tǒng)應(yīng)用的要求。可以得出結(jié)論:(1)通過本文介紹的在MII層標(biāo)記硬件時間戳的方式,可以消除操作系統(tǒng)和協(xié)議棧處理產(chǎn)生的延時,更精確地標(biāo)記硬件時間戳,從而提高了對時精度;(2)以太網(wǎng)PHY芯片采用美國國家半導(dǎo)體DP83848,因?yàn)樗哂械偷难訒r抖動特性,百兆網(wǎng)速的點(diǎn)對點(diǎn)主從對時產(chǎn)生的物理層延時抖動非常微小。

參考文獻(xiàn)

[1] IEC 61850.Communication networks and systems in substa-tions[S].2003.

[2] 國家電網(wǎng)公司.智能變電站技術(shù)導(dǎo)則[Z].2009.

[3] 王水魚,魏傳均.基于IEEE 1588的智能變電站時鐘同步技術(shù)研究[J].微型機(jī)與應(yīng)用,2012,31(23):78-81.

[4] 黃健,劉鵬,楊瑞民.IEEE 1588精確時鐘同步協(xié)議從時鐘設(shè)計[J].電子技術(shù)應(yīng)用,2010,36(7):91-97,108.

[5] 魏豐,孫文杰.IEEE-1588協(xié)議時鐘同步報文的精確時間標(biāo)記方法研究[J].儀器儀表學(xué)報,2009,30(1):162-169.

[6] 胡永春,張雪松,許偉國,等.IEEE-1588時鐘同步系統(tǒng)誤差分析及其檢測方法[J].電力系統(tǒng)自動化,2010,34(21):107-110.

[7] 陳炯聰.IEEE 1588同步技術(shù)在電力系統(tǒng)中的應(yīng)用[M].北京:中國電力出版社,2012.

[8] IEEE Std.1588-2008.1588 IEEE standard for a precision clock synchronization protocol for networked measurement and control systems[S].2008.