李煒

(中電海康集團有限公司,浙江 杭州 311121)

摘要:傳統(tǒng)企業(yè)級固態(tài)硬盤存儲芯片采用外接DRAM(Dynamic Random Access Memory)顆粒的方式來存儲閃存地址轉(zhuǎn)換映射表,不僅成本高,占用面積大,還需要設(shè)計復雜的掉電保護流程和額外的備電保持電容。利用新型磁旋存儲芯片的掉電非易失特性,以及密度高、速度快、功耗低、數(shù)據(jù)保持時間長、可擦寫次數(shù)無限等特點,提出了一種基于嵌入式磁旋存儲芯片的固態(tài)硬盤控制器架構(gòu)方案,能夠大大簡化控制器芯片的掉電異常流程和備電設(shè)計,節(jié)省固態(tài)硬盤內(nèi)部的備電電容成本,有效支撐固態(tài)硬盤的容量提升。

關(guān)鍵詞:磁旋存儲芯片;固態(tài)硬盤;芯片架構(gòu);嵌入式

中圖分類號:TN492文獻標識碼:ADOI: 10.19358/j.issn.1674-7720.2017.01.009

引用格式:李煒. 一種基于嵌入式磁旋存儲芯片的固態(tài)硬盤控制器芯片架構(gòu)[J].微型機與應(yīng)用,2017,36(1):2931.

0引言

隨著大數(shù)據(jù)和云計算的發(fā)展,大量的數(shù)據(jù)需要進行存儲,另一方面,隨著NAND閃存(NAND Flash)工藝的進步和良率的提升,固態(tài)硬盤(Solid State Disk,SSD)的成本已經(jīng)下降至接近企業(yè)級機械硬盤(Hard Disk Drive)相當?shù)乃剑琒SD在服務(wù)器、數(shù)據(jù)中心以及存儲系統(tǒng)中的應(yīng)用越來越廣泛。

傳統(tǒng)的企業(yè)級SSD控制器大多采用基于DRAM方案的數(shù)據(jù)和表項存儲方案,不僅設(shè)計難度大,掉電異常流程復雜,而且在SSD盤內(nèi)需要占用大量的空間用來擺放備電鉭電容,既增加了成本又制約了盤內(nèi)利用空間,無法做到SSD的容量提升。

本文將嵌入式磁旋存儲芯片(SpinTransferTorque Magnetic Random Access Memory, STTMRAM)應(yīng)用于SSD控制器芯片架構(gòu)設(shè)計中,能夠簡化掉電異常流程,節(jié)省SSD盤內(nèi)備電電容,并可以提升硬盤容量達30%以上。

1當前固態(tài)硬盤控制器架構(gòu)方案簡介

圖1為當前主流企業(yè)級固態(tài)硬盤架構(gòu)方案示意圖。

當前的固態(tài)硬盤控制器芯片分為前端主機接口模塊、系統(tǒng)管理模塊、后端Flash接口模塊幾個主要的部分。

前端主機接口模塊主要負責接收和處理主機側(cè)下發(fā)的讀寫命令并將數(shù)據(jù)接收下來存到DRAM中。企業(yè)級SSD中,由于對性能要求高,前端主機接口基本上選用基于NVMe(NonVolatile Memory Express)協(xié)議的第三代PCIe(PCI Express)的接口,除此之外,SAS(Serial Attached SCSI)12 G和SATA(Serial ATA)接口也是當前SSD前端主機接口的主流協(xié)議。

系統(tǒng)管理模塊是SSD控制器芯片的最核心單元,包括閃存地址映射表(Flash Translate Layer,F(xiàn)TL)管理、元數(shù)據(jù)管理、日志管理、流程控制等。其中FTL表項管理是其中最重要的部分。

FTL主要處理主機下發(fā)的邏輯地址(Logic Block Address,LBA)到介質(zhì)顆粒里存儲的物理地址(Physical Block Address, PBA)之間的映射表,是讓閃存完全模擬傳統(tǒng)硬盤操作的軟件層,有了FTL層閃存設(shè)備才能使用,F(xiàn)TL層的效率直接影響設(shè)備的性能表現(xiàn)。

系統(tǒng)管理模塊的作用主要包括下面幾點:FTL表項管理;垃圾回收的處理;增量空間的供給;冷/熱數(shù)據(jù)的交換處理;Plane、芯片、通道間的并行處理;任務(wù)請求的排序;緩沖區(qū)的管理;壞塊的管理;磨損平衡的處理;掉電恢復的處理;ECC的處理。

NAND Flash Interface主要負責處理NAND Flash顆粒的數(shù)據(jù)與命令交換。NFI負責把主機側(cè)的讀寫命令轉(zhuǎn)化成兼容ONFI和Toggle的標準NAND接口協(xié)議,并在NAND顆粒與控制器數(shù)據(jù)緩存之間做數(shù)據(jù)的讀寫交互。

在SSD盤片的PCB板上,除了控制器芯片和大量的NAND Flash顆粒之外,還包括下列幾個主要組成部分:

(1)外掛DRAM顆粒在SSD盤片的作用主要有兩個方面:作為讀寫數(shù)據(jù)的緩存及存取FTL映射表。為了滿足此設(shè)計需求,控制器芯片設(shè)計中為了適配DDR協(xié)議,需要開發(fā)DDR Controller與DDR PHY進行適配,PCB上還要預留額外空間進行DRAM顆粒的排布以及高速信號布局布線。

(2)Electrical Capacity(備電電容)的作用是為了在意外掉電的情況下,能夠及時地把DRAM顆粒中存儲的FTL表項在備電電容電量的支撐下,安全及時地下刷至非易失性介質(zhì)(NAND Flash),防止FTL表項丟失引發(fā)的數(shù)據(jù)丟失情況。

傳統(tǒng)SSD控制器芯片架構(gòu)的不足在于以下幾點:

(1)由于企業(yè)級業(yè)內(nèi)常用的方案是用外接DRAM顆粒來存儲FTL表項,因此在芯片內(nèi)部需要額外的DDRPHY和DDR 控制器進行適配,開發(fā)DDR控制器和DDR PHY的難度相當大,而從EDA vendor處進行IP 授權(quán)的費用又相當昂貴,因此會增大設(shè)計開發(fā)成本。

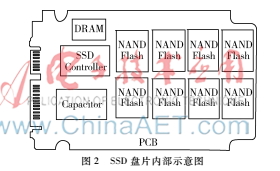

(2)盤片內(nèi)部空間限制,如圖2所示為標準2.5英寸SSD的印制電路板(PCB)示意圖。從國內(nèi)某著名公司生產(chǎn)的企業(yè)級SSD盤片剖解可以看出,SSD硬盤的PCB板大約80%的空間是布滿了閃存介質(zhì)顆粒,另外20%的空間擺放SSD控制器芯片、DRAM顆粒及備電電容等。

(3)企業(yè)級SSD對于數(shù)據(jù)可靠性的要求極高,其設(shè)計時必須考慮在各種異常情況下(如異常掉電)能夠把控制器內(nèi)部的最核心內(nèi)容—FTL表安全可靠地存儲到非易失性介質(zhì)中。在常規(guī)企業(yè)級SSD控制器芯片架構(gòu)中,DRAM內(nèi)部存儲著FTL表項,因此在遭遇掉電異常時,需要把DRAM內(nèi)部的FTL表下刷至NAND Flash中。簡而言之,就是要在備電電容支撐電量的這一小段時間內(nèi),控制器能夠?qū)TL表項的數(shù)據(jù)以寫操作的形式存儲到NAND Flash中。因此在備電設(shè)計上,一是需要消耗數(shù)量巨大的貼片式鉭電容來提供備電能量,導致PCB上的可用空間會進一步縮小,二是備電涉及到數(shù)據(jù)的異常處理流程,會提高硬件以及固件設(shè)計的復雜度。

2磁旋存儲芯片(STTMRAM)的特點

在眾多新型非易失性存儲介質(zhì)中,磁旋存儲芯片(STTMRAM)能夠良好地與CMOS半導體工藝相兼容,利用較少的金屬層即可以做到存儲單元的高密度集成。同時由于其接近于靜態(tài)隨機存儲器(Static Random Access Memory, SRAM)的讀寫速度,極低的靜態(tài)和動態(tài)功耗,具備掉電不易失的特性,接近于無限的擦寫次數(shù),高溫下長時間的數(shù)據(jù)保持能力以及抗強磁場輻射等特性,是作為企業(yè)級SSD控制器中數(shù)據(jù)緩存和FTL表項存儲的天生優(yōu)良介質(zhì)[1]。

當前,眾多半導體設(shè)計大廠都將MRAM芯片作為下一代非易失性存儲介質(zhì)的研發(fā)重點,除了臺積電、三星和東芝一直在持續(xù)推進STTMRAM的研發(fā)之外,美國的EVERSPIN公司已經(jīng)發(fā)布了256 MB的量產(chǎn)測試芯片。隨著工藝的進步和良率的提升,STTMRAM在存儲細分領(lǐng)域中的應(yīng)用將會越來越廣泛[2]。

將嵌入式STT-MRAM應(yīng)用在SSD控制器芯片架構(gòu)設(shè)計中,充分利用其掉電不易失數(shù)據(jù)的特性,能夠節(jié)省大量的備電設(shè)計和備電流程,極大地簡化SSD的控制器架構(gòu)設(shè)計。另外,由于節(jié)省了貼片式鉭電容,在PCB板上能夠留取更大的空間來支撐更多的NAND Flash顆粒的放置,達成更大的容量。除此之外,簡化了控制器芯片內(nèi)部的DDR接口相關(guān)IP設(shè)計,利用嵌入式STTMRAM的內(nèi)部總線接口(SRAMlike),既簡化了設(shè)計難度又能夠減少板上走線的信號延時,避免對接口高速信號的影響。

3基于嵌入式磁旋存儲的SSD控制器架構(gòu)方案

圖3為應(yīng)用嵌入式STTMRAM之后的SSD控制器芯片架構(gòu)示意圖。

本方案的技術(shù)特征在于:

(1)移除SSD控制器芯片內(nèi)部的DDR控制器和DDR PHY,直接以類SRAM(SRAMlike)的接口形式將嵌入式STTMRAM集成在控制器芯片內(nèi)部。

SRAMlike的總線接口信號包括片選CS、寫使能WE、讀使能RE、輸出使能信號OE、復位RST、時鐘CLK、地址線A[31:0]、數(shù)據(jù)輸入線DIN[31:0]及數(shù)據(jù)輸出線DOUT[31:0]。采用內(nèi)部總線接口與控制器內(nèi)部模塊進行交互,能夠極大地減少信號線傳輸延時以及外部接口協(xié)議帶來的額外開銷,進一步提升控制器的性能。

(2)STT-MRAM的主要作用在于:接收前端主機接口下發(fā)的數(shù)據(jù),作為與后端Flash接口的數(shù)據(jù)緩存;存儲閃存地址轉(zhuǎn)換層表項;存儲元數(shù)據(jù),如有效頁個數(shù)、壞塊管理信息、固件、啟動代碼、稀疏校驗矩陣等。

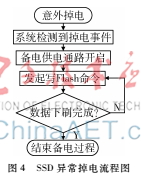

(3)備電流程的簡化。在傳統(tǒng)的SSD控制器芯片架構(gòu)中,由于數(shù)據(jù)以及FTL表項都是存儲在DRAM中,而DRAM具有掉電易失數(shù)據(jù)的特性,因此為保證數(shù)據(jù)可靠性,在遭遇到異常掉電的情形下,傳統(tǒng)控制器芯片需要在板上備電電容的電量支撐下,主動發(fā)起Flash的寫操作,將需要保存的重要信息全部下刷到非易失的閃存中,當下一次上電后,控制器需要發(fā)起讀操作再將FTL表項等數(shù)據(jù)重新讀取到DRAM中,完成系統(tǒng)的初始化。圖4為SSD異常掉電流程圖。

在本架構(gòu)方案中,由于嵌入式STTMRAM的掉電非易失特性,在遭遇到掉電異常時,數(shù)據(jù)和FTL表項依然可圖4SSD異常掉電流程圖以安全地進行存儲,因此系統(tǒng)備電流程將會被極大地簡化。盤片內(nèi)部用來做備電的鉭電容也能夠去除,節(jié)省盤片內(nèi)部的硬件設(shè)計成本。根據(jù)一款900 GB的SAS接口的企業(yè)級SSD盤片的解剖分析可以看到, 為了滿足備電需求,盤片PCB上一共放置了共400多個鉭電容。如果采用本架構(gòu)方案,能夠?qū)⑦@些額外的鉭電容全部移除,一方面節(jié)省了硬件元器件成本,另一方面利用鉭電容移除的PCB面積來貼NAND Flash顆粒,至少能夠使SSD盤容量提升20%。

4結(jié)論

本文提出的基于嵌入式STTMRAM的固態(tài)硬盤控制器架構(gòu),能夠極大地簡化控制器內(nèi)關(guān)于FTL表項的備電流程,簡化盤片內(nèi)的PCB設(shè)計難度和成本,在提升SSD讀寫性能的同時能夠有效支撐SSD做到更大的容量。隨著STTMRAM的工藝技術(shù)進步和良率的提升,磁旋存儲芯片必將在更多的存儲細分領(lǐng)域中得到廣泛的應(yīng)用。

參考文獻

[1] TANG D D, LEE Y J. Magnetic memory fundamentals and technology[M]. England: Cambridge University Press,2010.

[2] Xie Yuan. Emerging memory technologies: design, architecture, and applications[M]. Germany: Springer, 2014.